然而这里我们将举这样一个例子,就是对于某个较高时钟频率你已经检查了静态时序分析(STA),而且时序约束也是正确的。

2016-12-30 10:07:13 2344

2344 【RA系列】用时钟频率精度测量电路进行时间校验

2023-11-25 08:06:23 220

220

题目:已知8051单片机的时钟频率为6MHZ,通过定时器1的工作方式1在P1^1引脚输出一个1KHZ占空比为60%的矩形波。已知条件分析:1、时钟频率6MHZ,从这里我们可以得出它的机器周期为1/f

2021-07-20 06:17:19

时钟频率/机器周期/与执行指令时间的联系与区别是什么?

2021-10-27 06:50:08

时钟频率、机器周期与执行指令的时间有什么联系?时钟频率、机器周期与执行指令的时间区别在哪里?

2021-07-06 08:50:34

2.1kHz的频率,无论我在约束文件中更改数量。无论我把它设置为时钟的频率,我的样本都是> 20倍。我有什么理由读2.1kHz吗?如果您需要更多代码/信息,请询问。帮助将被贬低。以上来自于谷歌翻译

2019-03-20 08:31:40

1.时钟频率是什么?时钟:顾名思义,时钟以精确和固定的时间间隔,触发电信号,其信号被控制单元用于推进CPU的内部操作。而CPU执行 取指令–解码–执行的速度为时钟速度(时钟频率)。在各类CPU当中每

2021-11-30 07:17:35

我们知道,F103默认的外部晶振是8M,系统时钟频率是72M,但实际项目中,多数情况下可能会采用16M,25M晶振等等,如果不注意,很容易就超频,导致单片机无法正常运转,此处以16M晶振为例,说明

2021-08-12 07:26:34

AD5933和AD5934的时钟频率差异的相关问题?

1.时钟频率相差4倍,AD采样频率是不是也相差4倍?

AD5933:1MSPS AD5934:250kSPSPS(AD5934:250kSPS

2023-12-01 06:55:01

如题

AD9527 时钟频率范围和转换速率之间的明确关系?

时钟输入频率和功耗是否有关系?

2023-12-20 08:11:59

最近在用CDCE72010这款芯片,晶振频率是491.52MHz,是不是意味着它的输出时钟必须是晶振频率的分频或者倍频呢?按照手册配置芯片的寄存器,计算的结果应该是需要的时钟频率,但是实验测得的却还是491.52MHz的分频倍数,求问这是怎么回事呢?是不是不能配置成其他的时钟频率?求大神指教!

2016-04-16 18:15:24

本帖最后由 MANTENUO 于 2016-9-19 15:27 编辑

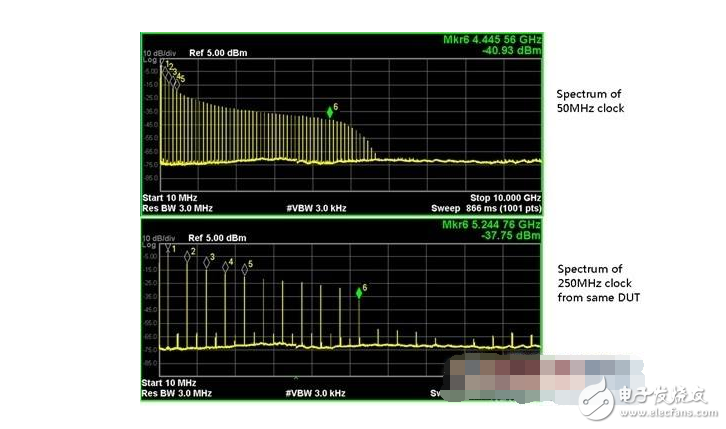

内部时钟频率为100M,个人认为是内部时钟频率倍频造成的300M/500M位置辐射发射超标,希望广大的高手们给一下

2016-09-19 14:49:59

QSPI(200M),SDIO(50M),UART(50M)和放大器生成正确的时钟频率。来自IO_PLL的ETH0(25M)。通过使能SPI0(映射到EMIO),我仍然可以看到这些时钟存在,SPI0时钟

2019-09-19 13:51:53

最近在看F28335-QEP的使用,有个困惑,“当eQEP单元工作在正交计数模式时,通过检测QEPA和QEPB信号的边沿为位置计数器提供计数时钟QCLK,因此eQEP逻辑产生的时钟频率是输入时钟频率

2018-08-23 15:17:00

SPI的时钟频率最多只能配置到fPCLK/4(18M)么?

2020-03-24 04:35:08

SPI的最高时钟频率是12MHz。虽然主机模式下,SPI的SCK频率可以配置为PCLK/2,但实际受GPIO的延时的限制,通信速率不能超过12MHz。

2022-06-02 15:24:29

STM32的时钟有何重要性?STM32时钟频率外部连接功能有哪些?

2021-10-21 09:09:27

STM32F103的时钟频率是多少?STM32F107的时钟频率是多少?

2021-10-26 07:35:09

STM32F407之时钟、频率、存储概述文章目录STM32F407之时钟、频率、存储概述1.整体特性1.1存储器组织架构1.2 内嵌SRAM1.3Flash和自举程序2.电源3.时钟介绍3.1系统

2021-08-02 07:24:37

STM32F407定时器TIM3的时钟频率设置说明时钟树设置相关时钟树先是外部时钟,然后/M后变为1MHz,xN后变为366MHz,/P后变为168MHz,此时为SYSCLK时钟频率,经过/1后变为

2021-08-04 08:37:49

cyclone iv最高工作时钟频率是多少?有没有专门的ARM核呢

2014-11-10 11:22:38

时钟频率设置为48MHZ,但是编译的时候有一条警告:大体的意思应该是说实际的时钟频率只有24MHZ。根据LED的频闪频率,时钟频率确实实际只有24MHZ。另外有cypress公司提供的实验版本的程序

2015-11-21 21:50:14

stm32定时器基本简介f4:stm32定时器时钟频率系统时钟频率/MHZSYSCLK(系统时钟)168APB1总线时钟(4分频)42APB2总线时钟(2分频)84因为系统初始化

2021-07-01 09:25:17

我在我的同学面前炫耀FPGA是做高速处理的,可是,当人家问我,我的时钟频率能达到多少时,我说利用PLL能拉到200MHz,他说,这么低啊?我的手机频率都是1.5G的呢。我无语。。。后来才了解到,他

2012-03-08 17:11:08

大家好,IM使用CY8C4127LQI-BL47 3用于我的应用。什么是最大时钟频率,我可以从时钟产生的资源在PSoC创建者?我需要它来产生一个正弦波使用PWM和过滤。例如,IM试图获得25kHz的PWM与24MHz时钟,使我的周期数为48。如果我能增加输入时钟,分辨率也会增加?谢谢阿什图什

2019-10-17 09:50:27

大家好,我有一段代码用于图像处理,我想确定最大块延迟,以便我可以推断设计可以使用的最大时钟频率。静态时序报告和时钟时序报告如下静态时间报告

2019-02-26 10:15:03

嗨,我有两个关于FPGA的问题......1)奇数频率 - 使用DCM,它很容易产生100MHz,25MHz等频率。但是如何生成11.6MHz,13.2MHz等奇数时钟频率?我可能需要什么原语?2

2019-02-25 11:13:27

的时钟频率是怎么来的?看图:单片机的最高时钟频率是由外部晶振进行提供的比如,F4的开发板的外部晶振是8MHz,8MHz的经在进行/M的分频之后进入PLL锁相环,在进行*N的倍频之后,再进行/P分频就得到了PLLCLK====也就是SYSCLK最高168MHz程序中在smt32f4xx_it.h中

2021-12-06 07:20:35

我正在尝试为外部闪存读取操作配置四路模式下 FlexSPI 操作所允许的最大时钟频率,我在 API“FLEXSPI_TransferBlocking”的 RFDR[0] 中收到值 0xC1,它不

2023-04-03 09:01:11

我正在使用IBert生成2.5 Gbps(PCIX)比特流; PCIX需要100 MHz参考时钟。在IBert时钟选项,系统时钟设置中,您可以将频率选项设置为10 MHz至100 MHz,我相信此值

2020-05-27 14:09:19

描述 为 VCU129 开发板提供的 BOARDUI.exe 可用于为板载 Si5348 时钟模块编写程序。 默认频率为 156.25Mhz,该频率的设置文件在 BOARDUI

2021-01-07 16:19:05

如何修改系统时钟频率?如何查看系统时钟频率?

2022-02-14 07:09:48

如何去配置STM32芯片的系统时钟频率呢?怎样去验证STM32芯片的系统时钟频率呢?

2021-11-10 07:23:48

我想改变spi的时钟频率我的设备可以支持高达40mhz但截至目前我正在生成500khz我需要将其增加到> 4mhz我的输入时钟频率是25mhz

2023-04-10 13:52:41

秒(100 Mhz)关闭和打开一个LED,我这样做是为了验证如何更改ZYNQ的时钟频率使用vivado的约束。这是我放在.xdc文件中生成不同的时钟频率set_property PACKAGE_PIN

2020-04-01 08:46:16

如何设置HI3519V101的DDR时钟频率?

2022-03-09 06:10:14

到报文后,以主时钟为基准进行延迟补偿,然后将计算出的新时钟值赋给从时钟。这种同步方法造成了从时钟计数值的不连续,即会出现重复(从时钟晶振频率快于主时钟)或跳跃(从时钟晶振频率慢于主时钟),而且这种

2019-08-06 06:34:51

我正在尝试使用 i.MX8MP EVK 输出 LVDS,但我无法调整 LVDS 输出时钟频率和时序。我需要修改哪些源码,应该怎么修改?需要的时序参数如下:像素时钟 = 54.13 MHz有效分辨率

2023-04-18 09:46:58

我使用时钟向导生成时钟配置文件,并将文件下载到CY3679工具包,但是我希望的时钟频率与实际频率不一致,为什么?我很困惑,我可以通过改变VCO频率来获得正确的时钟频率。那么,我应该怎么做才能产生我

2019-07-04 09:45:09

当设置PIC微控制器的时钟频率时,我们是必须在MPLAB中设置它,还是可以通过使用OSCCON寄存器的代码内的软件进行设置?

2020-03-23 10:08:31

怎样去计算stm32定时器的时钟频率呢?STM32F4的内部时钟树是由哪些部分组成的?

2021-10-22 08:21:04

怎样去设置DDR时钟的频率呢?有何方法?

2022-03-03 10:53:26

振荡器频率和时钟频率有什么不同,具体点

2016-06-01 22:02:54

如何在PSoC 5LP中生成7MHz时钟频率或PWM?我把直接时钟输出引脚,但在示波器输出不完美或良好?我如何解决这个问题? 以上来自于百度翻译 以下为原文How Can i Generate

2018-09-10 11:57:31

你好,我使用的芯片是TMS320C6416TGLZA8,该芯片上电复位后CPU时钟频率为850Mhz,还是CLKIN输入时钟频率?

2020-05-27 09:06:08

前言:在学51的时候我们知道单片机想要工作必须要有时钟,在stm32中,外部时钟源不是必须的,因为内部就有时钟源,因此我们需要了解stm32的时钟树以方便以后我们设置自己所需要的时钟频率时钟树解读

2021-08-12 06:56:41

AD9361接收通路中各个数字滤波器的输入时钟频率和ADC时钟频率的关系是什么?

2019-01-15 06:11:10

PWM时钟频率能否超过最大系统频率?

2021-01-08 06:41:04

SPI slave支持的最大时钟频率是多少?

2023-05-26 07:19:42

UCOS的软件定时器的时钟频率怎么算,

2019-05-29 04:36:00

;RCC_ADCCLKConfig(RCC_ADCCLK_PCLK_Div4);//配置ADC的时钟频率RCC_APB2PeriphClockCmd(RCC_APB2Periph_ADC1,ENABLE);RCC_AHBPeriphClockCmd(RCC_AHBPeriph_GPIOA, ENABLE);//ADC-

2021-08-04 07:22:27

时钟频率不再首要 每瓦特性能才是关键

最近Intel开始计划构建新的处理器架构,主推多核心和继Pentium M笔记本电脑处理器后的改良型电路,同

2010-01-21 15:35:05 657

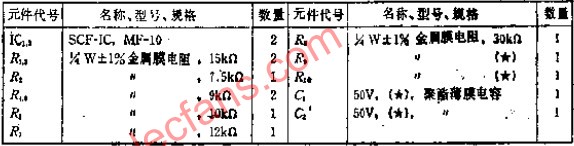

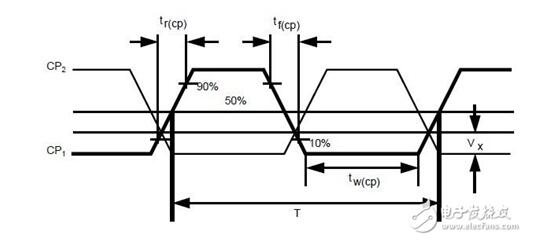

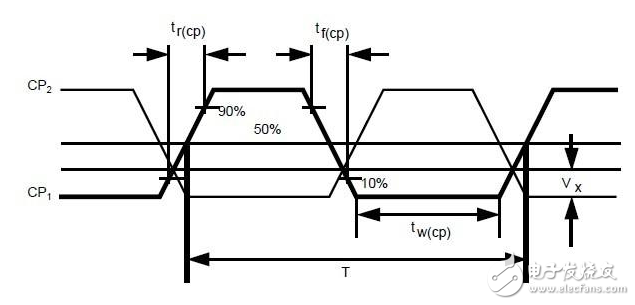

657 可使截止频率与时钟频率连动的48DB/OCTSCF低通滤波器

电路的功能

2010-05-13 14:39:56 1260

1260

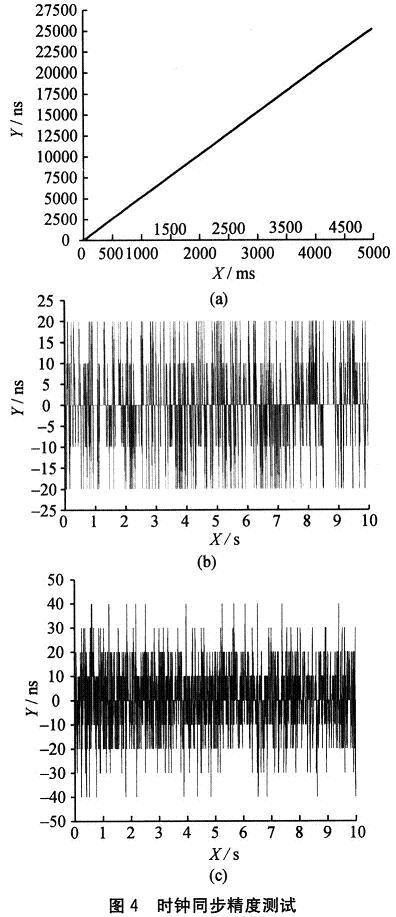

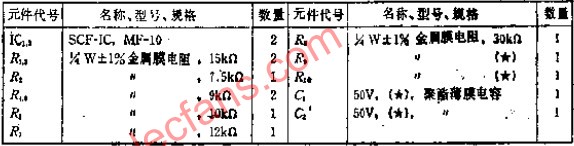

FPGA的时钟频率同步设计

网络化运动控制是未来运动控制的发展趋势,随着高速加工技术的发展,对网络节点间的时间同步精度提出了更高的要求。如造纸机械,运行速

2010-01-04 09:54:32 2762

2762

在有效抑制EMC 干扰的扩频时钟发生器(SSCG)中内置FRAM 的新产品MB88R157A 被纳入富士通的产品阵容。针对10MHz ~ 50MHz 的输入频率,该产品的输出时钟频率可以在1MHz ~ 134MHz 范围内任意设

2011-08-31 17:26:32 40

40 CPU时钟频率在过去5年里没有增加是很多不同类别的原因导致的。当设计一个CPU的微架构时,其中一个关键的设计决策就是如何实现更高的性能。

2015-06-18 11:10:35 1492

1492 通常如果你的设计在较低时钟频率时通过了仿真,但是在较高时钟频率时却失败了,你的第一个问题应该是你的设计在某个较高时钟频率时是否达到了时序约束的要求。

2017-01-04 13:08:12 2107

2107

)在单位时间内所出现的脉冲数量多少的计量名称;频率的标准计量单位是Hz(赫)。本文主要介绍什么是时钟频率及编程,具体的跟随小编一起来了解一下。

2018-04-28 09:49:46 42962

42962

目前对时钟频率还能代表处理器性能的话题在网上议论纷纷,情况有点复杂,自从英特尔在2008年推出睿频加速技术能动态、自动地对处理器超频后,这一技术就越来越普及了,在市场上销售的处理器都能根据能耗

2018-04-28 16:42:56 7158

7158 由ISP的时钟频率造成的ISP连接问题

2018-07-10 03:24:02 5027

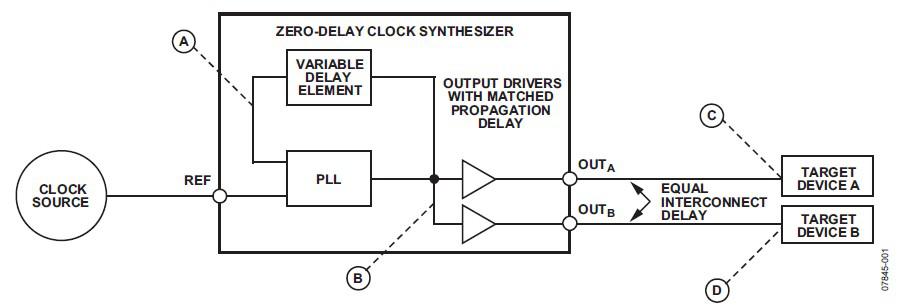

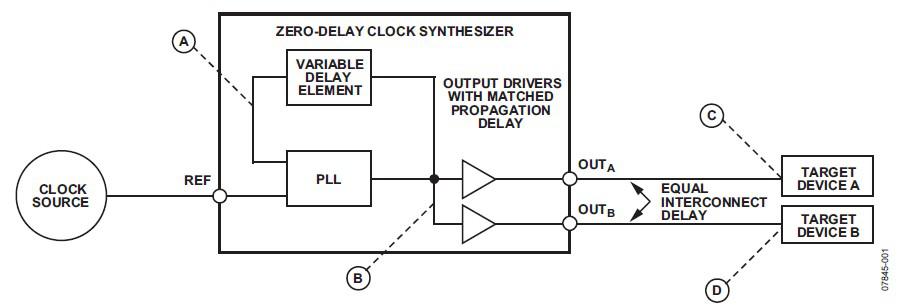

5027 零延迟指的是时钟频率合成器能够提供与时钟参考源边沿对齐的输出信号,其应用包括许多同步系统,如SONET和SDH网络、高速网络服务器、网络线路卡以及用于W-CDMA和Wi-Fi的基带定时等。 零延迟

2018-09-04 09:41:00 4454

4454

cpu时钟频率的单位是Hz,是以【若干次周期每秒】来度量,因此量度的单位采用的是SI单位赫兹(Hz),目前主流电脑和手机的CPU时钟频率单位已经迈入了GHz的时代。

2020-05-14 09:43:51 9584

9584 为 VCU129 开发板提供的 BOARDUI.exe 可用于为板载 Si5348 时钟模块编写程序。默认频率为 156.25Mhz,该频率的设置文件在 BOARDUI 的 clockFiles 目录下提供。如何修改时钟频率?

2022-02-08 15:09:04 2923

2923 PLL设计和时钟频率产生机理免费下载。

2021-06-07 14:36:43 22

22 1.时钟频率是什么?时钟:顾名思义,时钟以精确和固定的时间间隔,触发电信号,其信号被控制单元用于推进CPU的内部操作。而CPU执行 取指令–解码–执行的速度为时钟速度(时钟频率)。在各类CPU当中

2021-11-20 15:36:02 10

10 主要功能cc2530 按ok键切换时钟频率16mhz或32hmz#include <ioCC2530.h>#define uint unsigned

2021-11-29 18:51:04 21

21 本实验将给出系统时钟频率的查看方法,以及修改的方法。真正的想要了解这款单片机的时钟树还得自己去啃手册。如何修改系统时钟频率在system_msp4329401r.c文件中,在64~71行处,定义

2021-12-14 18:55:00 3

3 晶振频率是晶体振荡器的固有频率,而时钟频率是以时间为准的振荡频率,一个时钟周期等于两个振荡周期,所以晶振频率等于2倍时钟频率。那么这两个频率之间有什么区别?

2022-01-29 16:57:00 9435

9435 在IIC协议中涉及到两根线:SCL与SDA。SCL就是时钟信号线,SCL线上的频率就叫时钟频率。在对IIC总线进行学习与使用时,经常会听到设置IIC的时钟频率为xxxHz,或者设置IIC的数据传输率为xxxKbit/s。明明概念里可以进行配置的只有一个时钟频率,那么这个数据传输率这位老兄是怎么个情况。

2023-04-04 14:03:54 2613

2613 如何改变spi的时钟频率? 改变SPI的时钟频率需要以下步骤: 1. 选择合适的时钟源和分频器:SPI接口的时钟源可以是内部时钟或外部时钟,需要根据具体情况选择;同时需要根据所需的SPI时钟频率

2023-06-03 16:36:02 2130

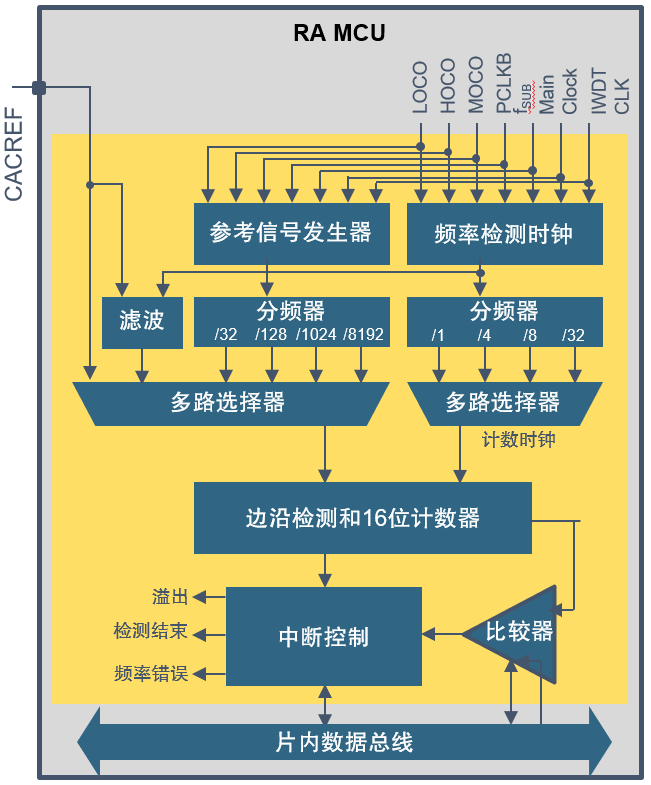

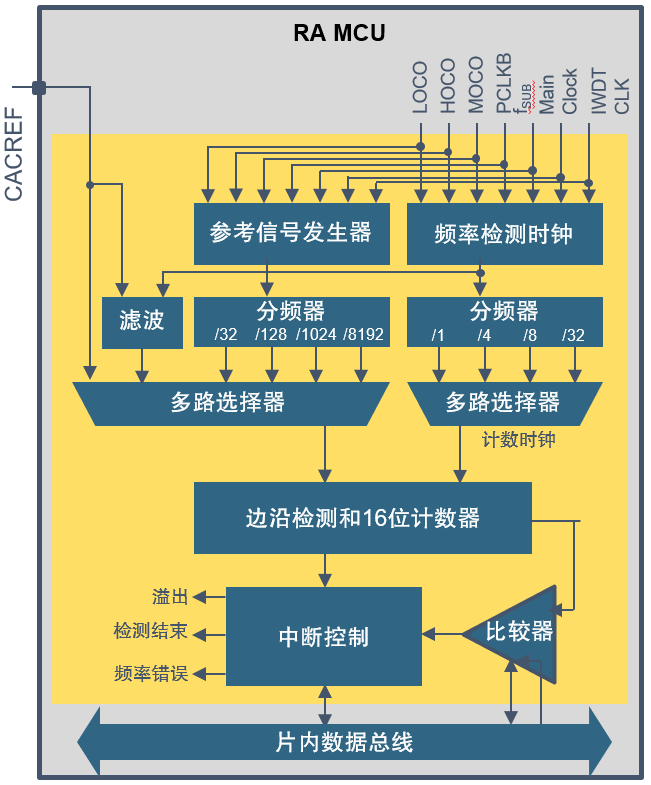

2130 本篇文章我们将向您介绍RA微控制器系列中一个不太常见和不太容易理解的外设,即时钟频率精度测量电路(CAC)。时钟频率精度测量电路旨在使我们能够通过将RA微控制器上可用的许多内部和外部时钟源相互对比,检查它们的精度,并在比较结果出现意外偏差时指示出来。

2023-08-08 02:54:30 280

280

在芯片设计中,为了便于定位故障,有时候需要确认部分时钟频率是否正确,需要部分debug手段。常见的方式是:将时钟信号引到芯片管脚,通过仪器测量。这类方式必须要测量仪器,并且需要熟练使用,耗时较长。还有一种简单的方式,通过时钟计数的方式判断时钟频率是否正确。

2023-09-20 14:17:06 385

385

fpga与dsp通讯怎样同步时钟频率?dsp和fpga通信如何测试? 在FPGA与DSP通讯时,同步时钟频率非常重要,因为不同的设备有不同的时钟频率,如果两者的时钟频率不同步,会导致通讯数据的错误

2023-10-18 15:28:13 1060

1060 双路LVDS信号和单路的时钟频率有什么关系?是一个时钟内传输两个像素的数据吗? 双路LVDS信号是一种在高速数据传输上应用广泛的接口,它利用微小的电压摆动来传输数据。在双路LVDS信号中,数据被分成

2023-10-18 15:38:22 972

972 电子发烧友网站提供《时钟和频率合成的应用领域.pdf》资料免费下载

2023-11-27 10:41:13 2

2 前面给小伙伴介绍过串口发送和接收异常可能的一些原因,其中就有说到时钟频率对于异步通讯的重要性。而我们通过程序去配置的时钟都是理论值,那如果想要获得内部一些时钟频率的实际值,需要怎样做呢?

2024-01-20 09:29:10 279

279

晶振频率和时钟频率本质上有何区别呢?时钟频率有什么作用? 晶振频率和时钟频率是两个相关但又有所不同的概念。下面我们将逐一介绍这两个概念的含义、区别和作用。 首先,我们来了解晶振频率。晶振是一种

2024-01-24 16:11:35 307

307 四个单片机能共用一个晶振时钟频率来工作吗? 四个单片机共用一个晶振时钟频率来工作是可能的。在实际应用中,由于资源的限制和成本的考虑,使用共享时钟频率可以减少系统中使用的晶振数量,有效地降低了系统

2024-01-31 11:31:45 521

521

电子发烧友App

电子发烧友App

评论