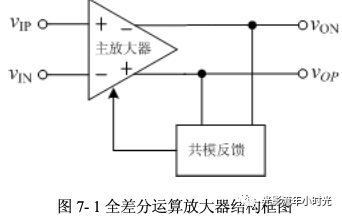

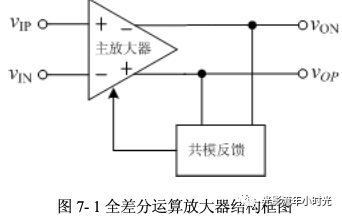

全差分运算放大器就是一种具有差分输入,差分输出结构的运算放大器。

2023-09-25 17:34:56 3116

3116

这种全差分放大器能不能使用G=+1高速运算放大器作为buffer使用,增加AD8132的负载能力

2023-11-20 07:52:37

信号,也可以输入共模信号,共模信号大部分来自噪声,最核心的愿景是:共模被抵消,差模被放大。四、输入电压范围(Vin或Vcm)运算放大器输入范围比较复杂,理论上来讲,同相端和反相端模拟输入在电源的正轨到

2021-12-07 07:00:00

描述差分运算放大器板运算放大器在配置为“差分”模式时可用于许多有趣的事情——包括模拟计算器、简单的平衡麦克风前置放大器和原始组件曲线跟踪器。

2022-06-28 07:20:14

平衡的电路,两个集电极电压之间的零差。这被称为共模操作,当输入为零时,放大器的共模增益为输出增益。运算放大器还具有一个低阻抗的输出(尽管有一个输出带有一个额外的差分输出),该输出以一个公共接地端为基准

2020-12-25 09:05:21

运算放大器共模抑制(CMR)的问题出在哪里呢?我们该怎么去解决这个问题?

2021-04-07 06:55:35

信号,也可以输入共模信号,共模信号大部分来自噪声,最核心的愿景是:共模被抵消,差模被放大。四、输入电压范围(Vin或Vcm)运算放大器输入范围比较复杂,理论上来讲,同相端和反相端模拟输入在电源的正轨到

2021-08-25 07:00:00

运算放大器的电路结构运算放大器的内部电路结构如下所示。一般由输入段、增益段、输出段等3段电路构成。输入段由差分放大段构成,用于放大两个引脚间的电压差。 另外,同相信号成分(引脚间无电位差,输入相等

2019-05-27 02:48:52

地”的,当使用单端输入信号时,就会产生共模输入信号,即使使用高共模抑制比的运算放大器,也还是会有共模输出的。 所以,一般在使用时,都会尽量采用反相输入接法。 (2)正相是振荡器,反相才能稳定放大器

2019-07-21 22:54:12

范围从-45℃到125℃零漂移运放GS833X系列高精密零漂移运算放大器采用台积电先进的CMOS工艺及全新的斩波电路结构设计,可提供极低的输入失调电压(10μV,最大值)同时随时间推移和温度变化输入

2020-04-27 10:35:17

运算放大器有哪几类?折叠式共源共栅全差分运算放大器会受到哪些影响?

2021-04-07 06:29:07

RF设计领域,回归到了全差分结构,也开启了在差分信号链接口中的新应用领域。如何得心应手地应用运算放大器,快速、准确地设计满足需求的电路系统,是工程师们必须认真面对的问题。本书出自全球领先的半导体公司

2017-06-09 17:38:49

衡量运算放大器对作用在两个输入端的相同交流信号的抑制能力,是差模开环增益除以共模开环增益的函数。CMRAC通常定义在特定频率和整个直流共模电压范围:4. 增益带宽积 (GBW) 增益带宽积AOL

2009-09-25 10:42:49

类配置的低失真结合在一起。 摘要标准的运算放大器架构由三个相互连接的子电路组成:差分输入级,高增益级和输出级。741运算放大器的输入级具有一个差分对和一个有源负载。高增益级包括一个射极跟随器,一个有源负载的共射极放大器和一个补偿电容器。输出级是AB类放大器。

2020-09-16 10:19:24

类配置的低失真结合在一起。 摘要标准的运算放大器架构由三个相互连接的子电路组成:差分输入级,高增益级和输出级。741运算放大器的输入级具有一个差分对和一个有源负载。高增益级包括一个射极跟随器,一个有源负载的共射极放大器和一个补偿电容器。输出级是AB类放大器。

2020-09-23 09:49:22

还是有微小的差模信号,只是一般仪器测不出来,可是,这样一来,由于“虚短”就人为(因为虚短是深度负反馈的结果,是人为的)的增大了两输入端的共模信号,这样就对运算放大器的性能构成挑战。为什么运算放大器要这么

2019-06-19 04:20:05

非ppm放大器类型运算放大器的误差源输入共模抑制和偏置误差

2021-02-05 06:17:26

运算放大器这类集成运算放大器的特点是差模输入阻抗非常高,输入偏置电流非常小,一般Rid>1GΩ~1TΩ,一般为几皮安到几十皮安。实现这些指标的主要措施是利用场效应管高输入阻抗的特点,用场效应管组成

2019-09-26 16:40:31

本帖最后由 gk320830 于 2015-3-5 02:30 编辑

运算放大器经典应用资料特点:反相端为虚地,所以共模输入可视为0,对运放共模抑制比要求低输出电阻小,带负载能力强要求放大倍数

2011-12-19 14:26:00

VOUT下限为50 mV。显然,给定运算放大器的内部设计会影响该输出共模动态范围,必要时,器件本身的设计应当最大程度地减小VSAT(HI)和VSAT(LO),以便实现最大输出动态范围。某些类型的运算放大器

2014-08-13 15:34:22

为50 mV。 显然,给定运算放大器的内部设计会影响该输出共模动态范围,必要时,器件本身的设计应当最大程度地减小VSAT(HI)和VSAT(LO),以便实现最大输出动态范围。某些类型的运算放大器就采用

2018-09-21 14:50:51

采用运算放大器的基准电压源

2019-10-29 09:01:22

采用运算放大器的基准电压源

2019-10-31 09:02:27

本帖最后由 gk320830 于 2015-3-9 06:26 编辑

高速运算放大器产品型号工作电压±15(V)工作电压±5(V)工作电压5(V)最小稳定增益(V/V)带宽@Acl(MHz

2012-08-02 13:22:30

这种全差分放大器能不能使用G=+1高速运算放大器作为buffer使用,增加AD8132的负载能力附件无标题.jpg84.1 KB

2019-01-15 10:43:40

特征除非另有说明,否则在TA=+25°C,VS=+5V,RL=25kΩ时连接至VS/2。应用程序信息OPA336系列运算放大器采用最先进的0.6微米CMOS工艺制造。它们具有单位增益稳定,适用于广泛

2020-09-27 17:38:18

应用的理想选择,尤其是在遇到高源阻抗的场合。OPAx132运算放大器易于使用,并且不存在常见FET输入运算放大器中常见的相位反转和过载问题。输入共源共栅电路提供优良的共模抑制,并在其宽输入电压范围内保持低

2020-09-22 16:36:06

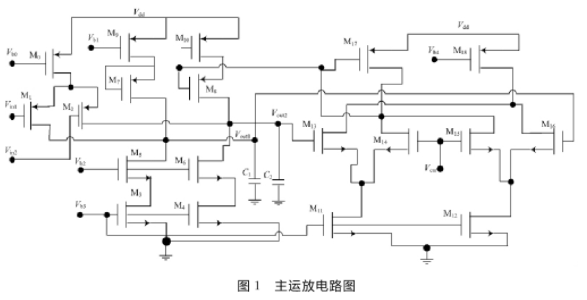

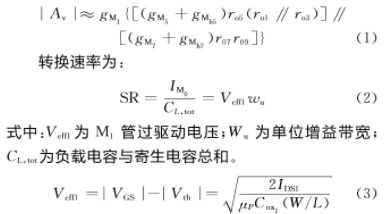

尾电流源架构,运算放大器主体部分单条支路上多达6个晶体管,造成偏置困难、工作不稳定的问题。因此,必须采用折叠式输入设计,本团队对运算放大器主体部分做了下图改进。

5.4 Cascode补偿提高带宽

2023-09-01 13:42:42

)或沿相同方向(同相)摆动,因此从两个集电极之间获取的输出电压信号为一个完美平衡的电路,两个集电极电压之间的零差。这被称为共模操作,当输入为零时,放大器的共模增益为输出增益。运算放大器还具有一个低阻抗

2021-02-20 09:15:44

的最高速度时,运算放大器不太可能会用作比较器,因此,通常只需注意从运算放大器的信号摆幅驱动 ECL逻辑电平,因杂散电容造成的额外速度损失并不重要。只需采用三个电阻即可,如图 2所示。 图2:驱动ECL

2018-10-31 22:32:44

运算放大器的精度。目前温度漂移参数可达0.15ppm。通过改变标准的硅工艺,我们可以设计通用运算放大器和高速运算放大器。典型的例子是LM324。 在标准硅工艺中采用JFET工艺的运算放大器主要是将

2023-02-14 15:40:39

。 OTA的设计 1、OTA结构 在2.5 V的电源电压下,虽然套筒式共源共栅结构具有高速、高频、低功耗的特点,但由于套筒式结构的输出摆幅低,不太适合低压下的设计。因此折叠式共源共栅的运放结构是一个

2018-10-08 15:47:53

双电源方案,但是双电源方案在实际操作中很麻烦,也容易出错,所以需要找一个单电源供电的差分运算放大器电路。实现方案INA321是一款既可以双电源供电又可以单电源供电的芯片。基本结构很简单,如下图所示...

2021-11-11 08:07:04

和精确(可调)增益;但是,在需要全差分输出信号时,它就无能为力了。人们已经使用一些方法,用标准组件实现全差分仪表放大器。但是,它们有着各自的缺点。图1. 经典仪表放大器一种技术是使用运算放大器驱动

2021-10-15 06:30:00

输出。这样的运算放大器被称为理想运算放大器。一般希望运算放大器具有高输入电阻、低输出电阻,尽量设计为接近理想运算放大器的电路结构。运算放大器按其放大率放大引脚间的电压差,因此输出电压表示如下。当

2019-04-23 22:49:51

输出。这样的运算放大器被称为理想运算放大器。一般希望运算放大器具有高输入电阻、低输出电阻,尽量设计为接近理想运算放大器的电路结构。运算放大器按其放大率放大引脚间的电压差,因此输出电压表示如下。当

2019-05-26 23:36:35

仪[/td]表放大器与运算放大器的区别是什么?仪表放大器是一种具有差分输入和相对参考端单端输出的闭环增益单元。大多数情况下,仪表放大器的两个输入端阻抗平衡并且阻值很高,典型值≥109 Ω。其输入偏置

2011-11-18 22:02:54

初学者向各位请教一些问题!

1.仪表放大器和普通运算放大器有什么不同呢?二者在组建电路上有什么区别呢?

2.使用仪表放大器对差分输入信号自身的性能有什么要求吗?(比如共模电压要到一定值,这是

2023-11-20 07:56:29

电流、输入输出全摆幅的CMOS运算放大器。同时还具有低工作电压,宽工作温度范围及低输入偏置电流等特点,这使得该系列运算放大器,非常适合在传感放大器,电池供电设备以及消费类设备中使用。图1

2019-04-08 09:33:51

最近在设计全差分折叠型共源共栅运放的时候,有一个问题想不明白,加入偏置电压后,调节管子让每个管子都处于饱和状态,并且输出处在了VDD/2。但是我发现只要偏置电压改变一点点哪怕1mv,静态工作点就会有很大的改变,这是为什么呢,好奇怪,有没有老哥为我解惑

2022-09-27 00:29:12

也没有同时流过两个R2电阻,所以放大器A1和A2将作为单位增益跟随器(缓冲器)工作。由于放大器A1和A2的输出端的输入电压在三个电阻器网络上出现差异,只需改变R1的值就可以改变电路的差分增益。差分运算放大器

2020-12-30 09:18:53

低压共源共栅结构是什么?具有最小余度电压的共源共栅电流源是什么?

2021-09-29 06:47:22

引起的失调电压降至最小。图2. 满摆幅输入放大器的共模输入电压从一个电源摆幅过渡到另一个电源摆幅时,输入偏置电流的极性和大小都可能变化。图3给出了典型运算放大器中保持反相和同相结构阻抗匹配的方法。反相

2020-11-20 10:03:54

号就属于这种情况。根据前面的假设条件,在电阻失配的情况下,这个电路就不再是一个真正的差分放大器,VO会随着共模分量而变化。 小结 运算放大器,如果选取恰当的外部元件,它能够构成各种运算电路,如放大、加、减、微分和积分等运算电路。运算放大器实现数学运算的能力,是将高增益与负反馈结合起来的结果。

2021-02-20 16:21:09

是一种广泛应用的运放结构。 由于所设计的电路应用于电源芯片系统中,基于速度等方面综合考虑,选择的是一个折叠式共源共栅运算放大器,另外由于运放在基准中是用作负反馈,所以选用单端输出的折叠运放。具体电路如下

2018-10-09 14:42:54

DC2319A-A,LTC6363的演示电路,是一款低功耗,低噪声差分运算放大器,具有轨到轨输出摆幅和良好的直流精度。放大器可以被配置为处理全差分输入信号或将单端输入信号转换为差分输出信号。 DC2319A的差分输出可配置一阶RC网络,以驱动ADC的差分输入

2019-05-17 09:11:23

的最佳输入共模电压间不一致程度的增加而大幅降低。 图2:二级放大器电路图。 宽带差分运算放大器的主要劣势在于其增益通常都很有限,且其增益级别也许在内部已经预设。根据应用的不同,可能需要为设计添加

2011-07-28 09:32:59

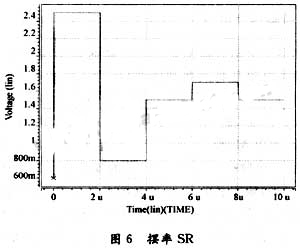

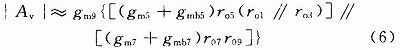

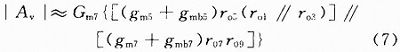

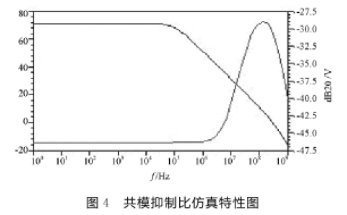

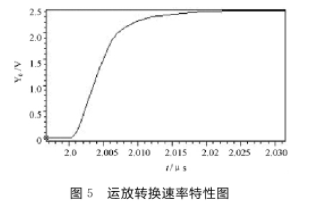

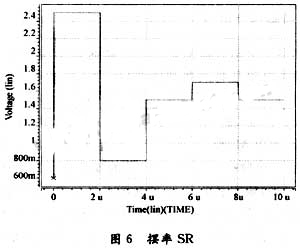

本文介绍的运放是一种采用TSMC 0.18 μm Mixed Signal SALICIDE(1P6M,1.8V/3.3V)CMOS工艺的折叠共源共栅运放,并对其进行了DC,AC及瞬态分析,最后与设计指标进行比较。

2021-04-14 06:59:22

电流反馈和电压反馈运算放大器的基本原理提高运算放大器速度和带宽的有效途径高速运算放大器使用过程中的稳定性解析

2021-04-23 06:22:22

TI高精度实验室-运算放大器-第七节-共模抑制和电源抑制抑制可能是一件好事,特别是在共模或电源电压错误的情况下。 本系列视频介绍了如何改变运算放大器的共模电压或电源电压,从而在交流和直流两端引入误差

2021-12-30 06:50:21

我有一个源极跟随器(共漏极)配置的NMOS晶体管,但具有从输出到输入的反馈。它被用作功率级,因为负载的功率很高。如何用运算放大器代替电压源?

2024-03-01 07:26:44

时,SFDR为76 dB,精度达0.012%,完全满足12 bit要求。本文运用增益增强型折叠式运算放大器,以获得较高的增益和带宽。同时采用栅压自举开关,并通过对电路中的开关组合优化,极大的提高了电路

2021-04-20 06:45:33

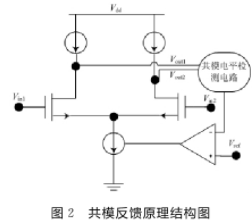

如何设计用于运算放大器的共模反馈电路?共模反馈电路的设计要点有哪些?全差分运算放大器的共模反馈原理是什么?

2021-04-20 06:17:09

共源共栅电感的工作机理是什么?怎么实现共源共栅CMOS功率放大器的设计?

2021-06-18 06:53:41

实现低于 1uV/ºC 的失调漂移,而 CMOS 的输入级则提供高达 5uV/ºC 的失调漂移。在 CMOS 输入运算放大器中实现极低失调的挑战在于阀值电压之间的差异(输入差分对)以及栅-源电压与阀值

2018-09-13 10:08:21

很麻烦,也容易出错,所以需要找一个单电源供电的差分运算放大器电路。实现方案INA321是一款既可以双电源供电又可以单电源供电的芯片。基本结构很简单,如下图所示:其中,电路的增益是由R2和R1的比值决定

2019-12-11 17:38:07

求一款实现IR接近检测的高速运算放大器

2021-04-25 09:00:00

本文设计的带共模反馈的两级高增益运算放大器结构分两级,第一级为套筒式运算放大器,用以达到高增益的目的;第二级采用共源级电路结构,以增大输出摆幅。另外还引入了共模反馈以提高共模抑制比。

2021-04-14 06:55:14

本文设计的带共模反馈的两级高增益运算放大器结构分两级,第一级为套筒式运算放大器,用以达到高增益的目的;第二级采用共源级电路结构,以增大输出摆幅。另外还引入了共模反馈以提高共模抑制比。该方案不仅

2021-04-22 06:08:31

求微弱电流检测用的共模电压范围最大值大于65V的运算放大器或仪表放大器

2023-11-14 07:21:08

用于精密放大器的匹配电阻网络适用于全差分运算放大器,配置为VOUT / VIN = 0.2

2019-11-06 08:53:34

折叠共源共栅比较器怎么修改为迟滞比较器

2021-06-24 07:36:52

初学者向各位请教一些问题!1.仪表放大器和普通运算放大器有什么不同呢?二者在组建电路上有什么区别呢?2.使用仪表放大器对差分输入信号自身的性能有什么要求吗?(比如共模电压要到一定值,这是为什么呢

2018-08-19 07:02:41

怎么设计一种单级全差分增益增强的折叠共源共栅运算放大器?

2021-04-20 06:26:29

CMOS运算放大器结构具有哪些特点?如何去设计CMOS运算放大器?怎样对CMOS运算放大器进行仿真测试?

2021-04-21 07:21:39

。通用运算放大器为我们提供了一个坚实的基础以开发专用的元件。所有运算放大器旨在在这些领域实现好的性能:大开环增益、共模抑制和电源抑制。高输入阻抗和低输出阻抗也是关键要求。Precision

2018-10-22 08:57:48

,在中国构建了与罗姆日本同样的集开发、生产、销售于一体的一条龙体制。BU7475HFV/BU7475SHFV是ROHM推出的超低消耗电流的CMOS运算放大器。是在单芯片中集成了输入输出全摆幅和接地检测

2019-04-19 04:47:53

集成运算放大器电子教案教学基本要求教 学 基 本 要 求主 要 知 识 点熟练掌握正确理解一般了解集成电路中元器件的特点及集成运放大典型结构√差分放大电路的类型与特点√差分放大电路分析计算方法

2009-09-16 09:12:40

分析了准浮栅晶体管PMOS 的工作原理、电学特性和等效电路,设计了一种电路结构简单的共模反馈电路(CMFB),实现了一个低压低功耗的差分运算放大器。采用Chrt0.35umCMOS 工艺

2009-11-27 11:39:23 8

8 本文设计了一种低压低功耗CMOS 折叠-共源共栅运算放大器。该运放的输入级采用折叠-共源共栅结构,可以优化输入共模范围,提高增益;由于采用AB 类推挽输出级,实现了全摆幅输

2009-12-14 10:37:19 29

29 设计了一种用在高精度音频Σ-Δ A/D转换器中的高增益CMOS全差分运算放大器。该运算放大器采用了套筒式共源共栅结构和开关电容共模反馈电路。通过分析和优化电路性能参数,实现了

2010-07-29 17:23:00 51

51 0.6μm CMOS工艺全差分运算放大器的设计

0 引言 运算放大器是数据采样电路中的关键部分,如流水线模数转换器等。在此类设计中,速度和精度是两个

2009-12-08 17:19:51 1632

1632 高速型运算放大器是什么意思

高速型运算放大器的定义

2010-03-09 15:51:14 2516

2516 折叠共源共栅运算放大器原理及设计

1 引言

本文介绍的运放是一种采用TSMC 0.18 μm Mixed Signal SALICIDE(1P6M,1.8V/3.3V)CMOS工艺的折叠共源共栅运放,并对其进行了DC

2010-03-12 15:05:24 10224

10224

电子发烧友为您提供了李福乐的全差分运算放大器电子书,介绍了全差分 运算放大器 的基本知识,如对于全差分放大器,其输出是差分方式且输出共模电压可以独立于差分电压设置。对

2011-07-18 16:54:32 0

0 设计并讨论了一种高单位增益带宽cmos全差分运算放大器。由于折叠共源共栅结构电路具有相对高的单位增益带宽以及开关电容共模反馈电路稳定性好、对运放频率特性影响小等优点,故

2011-07-31 21:51:57 115

115 本文设计了一种用于高速ADC中的高速高增益的全差分CMOS运算放大器。主运放采用带开关电容共模反馈的折叠式共源共栅结构,利用增益提高和三支路电流基准技术实现一个可用于12~14

2012-06-06 13:08:28 42

42 设计了一种用于高速ADC中的高速高增益的全差分CMOS运算放大器。主运放采用带开关电容共模反馈的折叠式共源共栅结构,利用增益提高和三支路电流基准技术实现一个可用于12~14 bit精度

2012-06-07 14:21:36 38

38 恒跨导轨对轨CMOS运算放大器的设计_赵双

2017-01-07 22:14:03 2

2 是有很用的。 这种灵活性允许在 CMOS

工艺中发展高性能无缓冲运算放大器。 目前, 这样的放大器已被广泛用于无线电通信的集成电路中。 介绍了一种折叠共源

共栅的运算放大器, 采用 TSMC 0. 18 混合信号双阱 CMOS 工艺库, 用 HSpice W 2005. 03 进行设计仿真, 最后与设计指标

2022-07-08 16:32:35 21

21 基于 chartered 0.35 m 工艺,采用 PMOS 管作为输入管的折叠式共源共栅结构,设计了一种采用增益提高技术的两级运算放大器。利用 Cadence 公司的spectre 对电路进行仿真

2017-11-04 10:40:17 29

29 CMOS运算放大器的基本分类1、单级差分运算放大器(电流镜做负载的差分放大器)2、套筒式共源共栅CMOS运算放大器(单级)3、折叠共源共栅CMOS运算放大器(单级)4、两级CMOS运算放大器

5、Rail-to-Rail CMOS运算放大器6、Chopper CMOS运算放大器 运放的概念、组成与电路结构

2018-11-07 10:10:57 89

89 我的论文题目是《CMOS 运算放大器的设计和优化》。我们可以知道无论在数 字还是模拟电路中,运算放大器运用之广泛是显而易见的。

2021-04-13 09:32:44 15

15 浅析采用高速运算放大器进行低失真设计

2022-02-11 15:28:18 10

10 电子发烧友网站提供《差分运算放大器板.zip》资料免费下载

2022-07-04 10:27:11 1

1 电子发烧友网站提供《全差分运算放大器开源分享.zip》资料免费下载

2022-07-26 15:06:11 5

5

![]()

![]()

电子发烧友App

电子发烧友App

评论