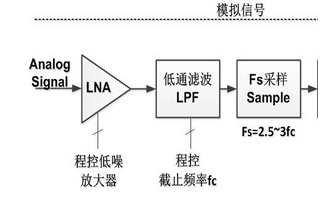

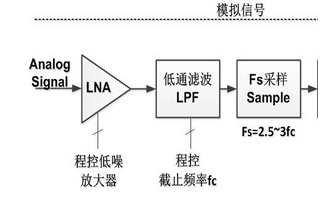

实际中,信号往往是无线带宽的,如何保证带宽有限?所以,我们在模拟信号输入端要加一个低通滤波器,使信号变成带宽有限,再使用2.5~3倍的最高信号频率进行采样。关于此我们下面将模拟数字转换过程将会看到。

2018-02-26 09:13:00 22038

22038

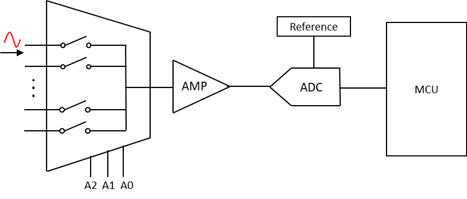

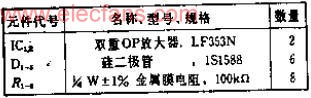

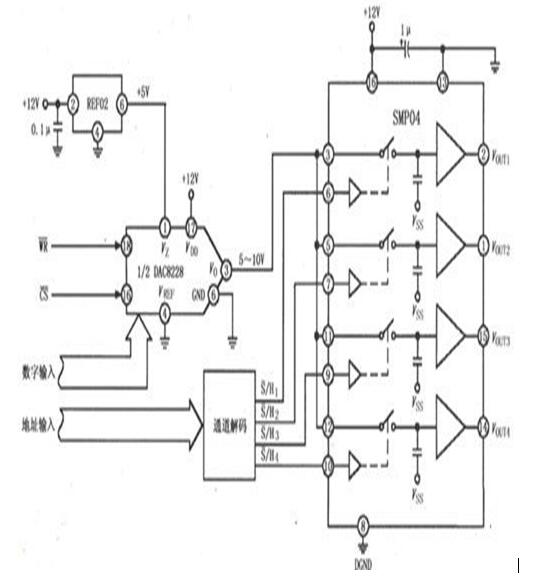

有些应用需要对一组模拟电压的采样进行保持,至少有两种传统方法可以满足这种要求。最常见的办法是将一个经典的模拟累加器与一个 采样保持 放大器级联。如图1所示。 经典的模拟

2012-04-01 10:51:11 6926

6926

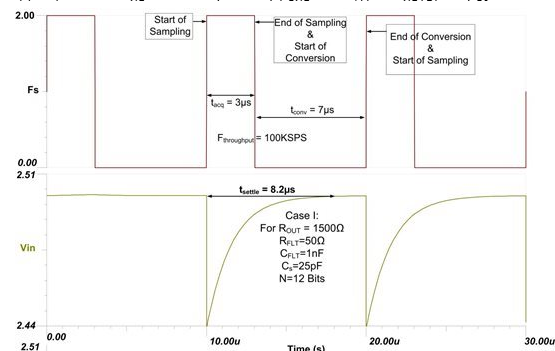

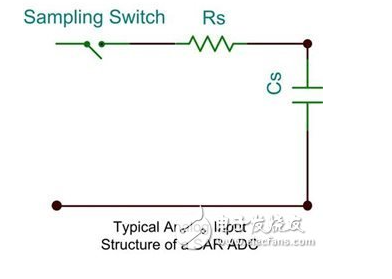

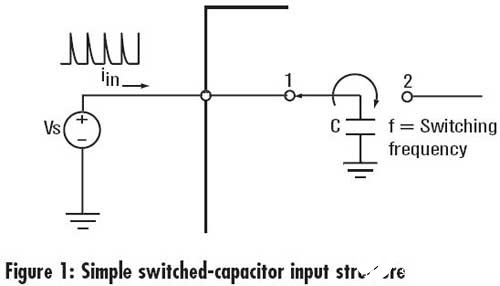

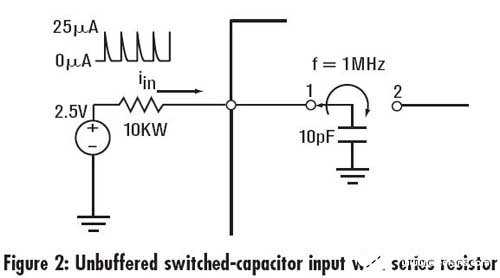

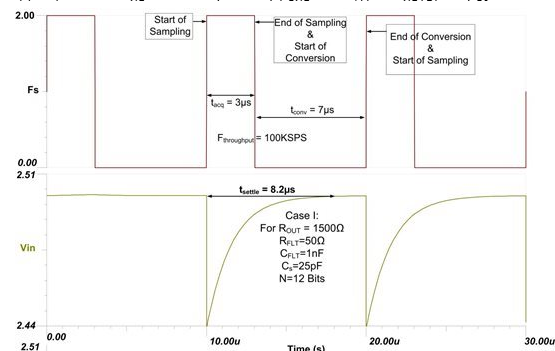

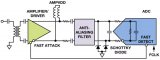

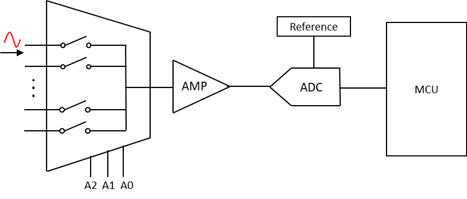

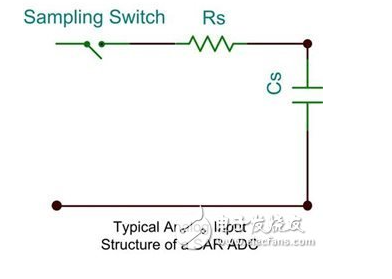

ADC的采样过程和模拟输入结构来了解驱动器的要求。 SAR ADC的模拟输入是一个采样开关、一个电阻器和采样电容器的组合。图1显示针对一个SAR ADC的模拟输入结构。 图1 采样开关在一定的时间周期tACQ(采集时间)内关闭以获得输入信号,并在转换过程期间打开。

2018-04-16 09:23:31 5899

5899

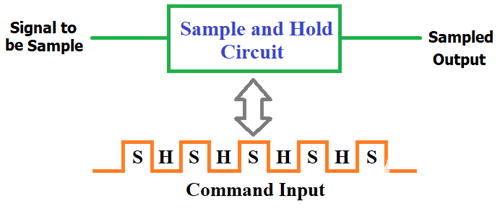

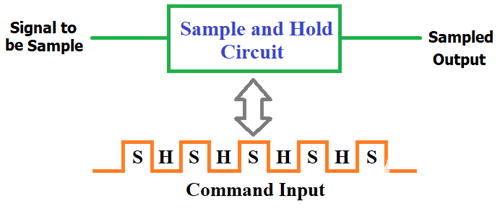

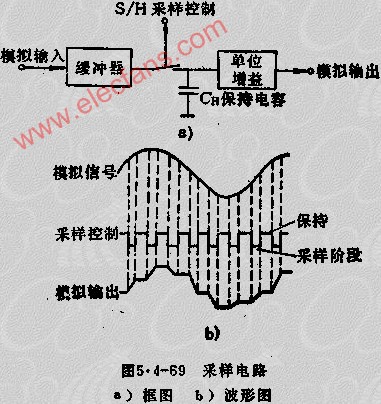

采样保持电路从模拟输入信号中获取样本并保持特定时间段,然后输出输入信号的采样部分。该电路仅对几微秒的输入信号进行采样。

2022-11-08 17:29:18 6704

6704

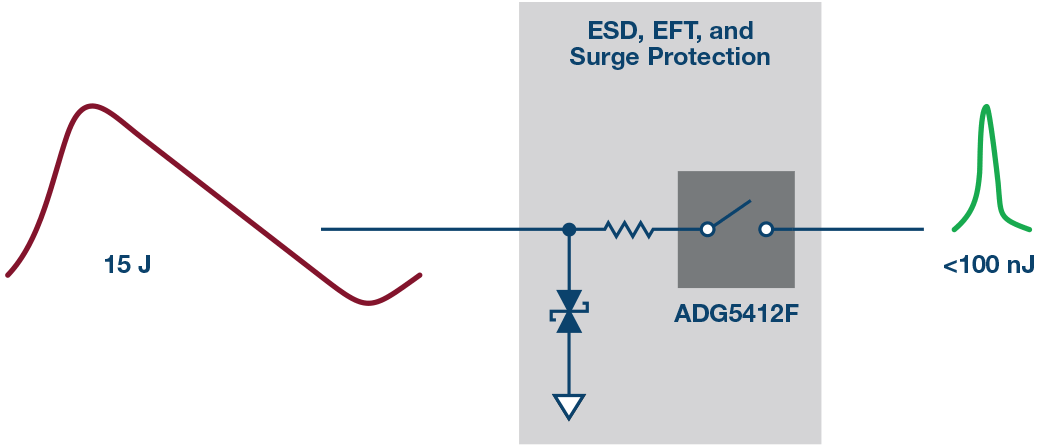

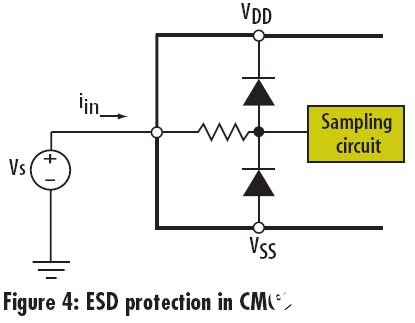

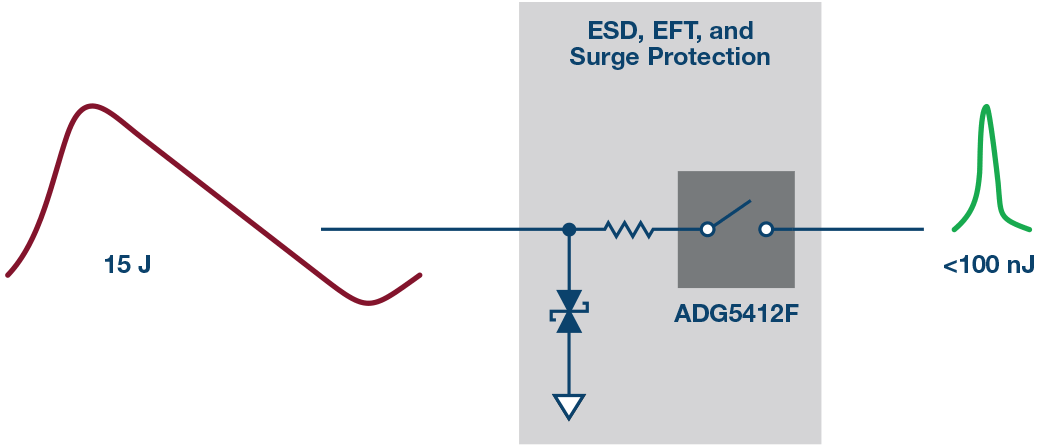

与系统模拟输入和输出节点交互作用的外置高压瞬变可能破坏系统中未采用充分保护措施的集成电路(IC)。现代IC的模拟输入和输出引脚通常采用了高压静电放电(ESD)瞬变保护措施。人体模型(HBM)、机器

2019-08-12 08:13:42

)采样频率大于2倍信号最高频率后可以无失真的恢复出原始信号实际中,信号往往是无线带宽的,如何保证带宽有限?所以,我们在模拟信号输入端要加一个低通滤波器,使信号变成带宽有限,再使用2.5~3倍的最高信号

2018-09-14 14:38:47

在其中选择各种信号以及信号的输入或输出状态;2. 采样时钟:设置采样时钟的源、频率以及采集或生成的采样数量;在多态VI选择中,可以在其中选择各种采样方式; 3. 开始任务:2. 读取:在程序中,采集

2019-04-23 09:40:04

,你就可以为你的应用考虑正确的系统结构。仪器结构的选择测试设备结构有四种主要类型:1、独立仪器。最精度最灵敏的独立仪器是台式仪器。它们是传统的仪器加上许多新的改进的性能,例如图形显示、按键选择功能、菜单

2011-09-22 11:06:33

器件即可用于多种应用。 SAR ADC还有另外一种优势:获取模拟输入信号的“快照”。SAR结构只对单一时刻进行采样(即“抓取”)。(我们随后将解释这种快照与Δ-Σ ADC的区别,后者对模拟数据进行多次过

2018-08-28 14:41:33

采样电路中运放输入多个电阻串联的作用

2017-11-22 23:44:38

信号存储器。在模拟信号输入通道中,是否需要加采样/保持器,取决于模拟信号的变化频率和 A/D 转换的孔径时间。对快速过程信号,在最大孔径误差超过允许值时,必须在 A/D 转换器前加采样/保持器,如对10Hz

2018-01-08 14:23:45

2us后就变为低电平,从datasheet中时序表格中,Tconv时间最小值是3.45us,典型值为4us,采样转换明显不正常,请问可能是什么原因造成???? SOS

2018-08-10 07:33:53

尊敬的ADI 技术人员:

你们好!最近参考电路笔记CN-0251,设计了一款对标准模拟信号0~10V,4~20ma 进行采样。

发现采集数据不稳定。模拟前端信号,输入0~10V,通过AD8275

2023-11-20 07:28:46

1、单独使用A通道或者B通道输入时,采样输出正常,但是单独使用B时输出有毛刺影响。但是同时对A、B两路输入时,输出完全不正常,请问这是什么原因造成的呢?当同时输入模拟输入A、B两路时,如何通过D7

2018-12-14 09:04:49

上就会出现噪声。将采样的时间延长也无法消除串扰。

想请教一下各路专家,造成串扰的原因和如何消除串扰,谢谢。

2023-12-18 08:27:39

DSP***的AD采样口输入的模拟电压是稳定不变的,然后采样回去以后,结果寄存器的值一直波动这是为什么呢?

2019-04-18 00:24:33

Matlab中的顺序结构及选择结构分别是如何构成的?

2021-11-19 07:11:23

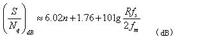

采样时钟考量在高性能采样数据系统中,应使用低相位噪声晶体振荡器产生ADC(或DAC)采样时钟,因为采样时钟抖动会调制模拟输入/输出信号,并提高噪声和失真底。采样时钟发生器应与高噪声数字电路隔离

2014-11-20 10:58:30

你好!因为项目的原因,我需要选择一个ADC芯片,希望ADC达到的要求包括:16路模拟单端输入支持8个通道的模拟差分输入采样精度16位采样速率250 kS/s

2019-02-26 10:59:44

求助程序:设计一个8路模拟量输入的巡回检测系统,使用查询的方法采样数据

设计一个8路模拟量输入的巡回检测系统,使用查询的方法采样数据,采样的数据存放在片内RAM的8个单元中,汇编 C语言都可以,记得是是“查询”,非“中断”哦,小弟跪解

2010-12-02 22:04:32

简介与系统模拟输入和输出节点交互作用的外置高压瞬变可能破坏系统中未采用充分保护措施的集成电路(IC)。现代IC的模拟输入和输出引脚通常采用了高压静电放电(ESD)瞬变保护措施。人体模型(HBM

2019-09-26 09:58:52

AD7606简介:AD7606/AD7606-6/AD7606-4为16位同步采样模数数据采集系统(DAS),分别有 8、6、4个采集通道。片上集成模拟输入箝位保护、二阶抗混叠滤波器、跟踪保持放大器

2018-11-01 09:25:42

事件结构中选择双击文件列表,系统会自动选择双击的那项,然后进行索引选择那个文件是吗?尝试了一下是这样但不知道原理,有没有人能解释一下,谢谢!

2015-04-20 16:00:39

我们经常想要模拟入射到周期性结构中的电磁波(光、微波),例如衍射光栅、超材料,或频率选择表面。

2019-08-26 06:01:13

使用AD9637-80进行中频多通道采样时,单片通道与通道之间的幅度误差达到6dB(同等输入功率下),模拟前端电路采样变压器耦合(数据手册19页,图47),变压器采样的是mini公司的TC1-1T+

2023-12-15 08:23:16

。选择二极管类型及其参数时必须作更全面的考虑。图8. 前端电路中的TVS二极管保护导致削波信号 使用肖特基二极管保护射频采样ADC输入当带宽和采样速率达到GHz和GSPS级别时,射频采样ADC可以简化

2018-09-21 14:38:04

我需要对两个模拟电压信号进行采样并保存数据(TDMS格式),因为要使用matlab对数据进行处理所以用excel打开tdms文件(安装了一个excel插件)。但是打开excel之后数据只有两列。即

2014-07-31 09:54:36

读到的数据就出现削顶;

RANGE引脚接低电平, 输入模拟范围超过±2.5v左右时 ,则读到的数据就出现削顶;

请问什么原因会造成这样?

数据采用两路串行读取. 原理图如下.

RANGE引脚的电平在P4处通过短路帽选择.

2023-12-14 06:11:42

的一部分。数据采集系统的其他部分也可增加其灵活性,包括信号输入接口、参考电压接口、用于ADC的时钟和采样系统以及用于转换后ADC输出数据的数据管理。 通常情况下,模拟信号输入接口共享一个通用输入输出(I/O

2017-12-19 17:10:08

:FPGA芯片区、多路选择与A/D采样电路、时钟电源区、PROM代码下载电路等几部分。结构示意如图1所示。FPGA芯片特点分析及资源分配本系统中的FPGA是采用Altera公司的EP1C20F400。该系

2011-08-23 10:15:34

通用模拟输入是工厂自动化普遍使用的单元电路,灵活测量模拟电压/电流信号以及RTD、TC成为组装过程中不可或缺的功能。工业4.0在工业结构、分布试管理、智能化控制方面带来了巨大变化,其高度 可配置性

2019-03-25 21:47:18

通用模拟输入是工厂自动化普遍使用的单元电路,灵活测量模拟电压/电流信号以及RTD、TC成为组装过程中不可或缺的功能。工业4.0在工业结构、分布试管理、智能化控制方面带来了巨大变化,其高度 可配置性

2022-03-16 11:23:20

你好我想在运行期间模拟列输入引脚读取多个ADC值。请分享C代码更改模拟列输入引脚。请找到附件JPG。最好的问候迪帕克阿格里ADCJPG35.7 K

2019-10-29 07:32:06

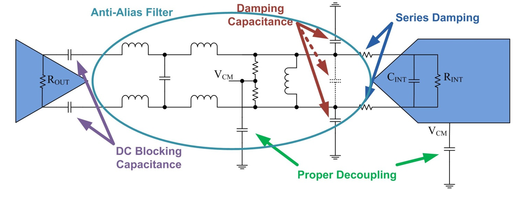

经常在缓冲器和 ADC 输入之间使用耦合 RC 滤波器网络 (LPF2),以最大限度地减少从 ADC 采样瞬态反射到缓冲器中的干扰。模拟输入端较长的 RC 时间常数会减慢这些干扰的稳定。因此,LPF2

2022-04-12 17:45:54

正常工作性能。AD9680按照数据手册中的建议进行控制,但输入如图10所示进行修改。模拟输入频率变化范围为10 MHz至2 GHz。CJ0的超低数值应当不会对ADC的SNR和SFDR性能造成影响。图

2018-11-01 11:25:01

的资源需求如表1。可以看出,如果采用传统的结构,考虑了ADC、参考芯片和运放调理电路,整个系统成本比较高。表1:使用8通道MUX实现64通道模拟采样的系统资源ADC参考芯片运放调理电路MUXMCU与ADC通信接口MCU控制MUX I/O口88…

2022-11-04 06:05:37

条件结构中,在选择真的时候显示输出控件,假的时候显示输入控件,如何实现?

2014-11-18 08:50:22

漏电流会对AD采样的精度造成什么影响?输入电压误差计算补偿公式是什么?

2021-09-30 07:04:35

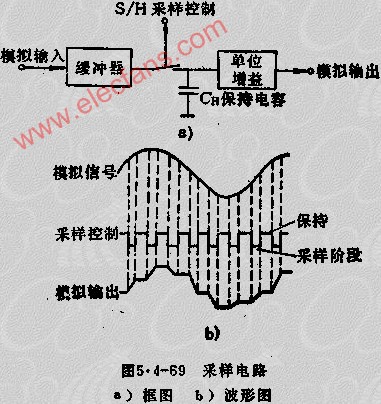

的间隔由采样频率决定,频率越高采样得到的信号越接近原始信号。但较高的采样频率会使得数据量增加,同时对系统的转换速度要求变高。一般选择采样频率为原始信号最高频率的3-5倍。

▍保持

采集模拟信号后,需花时间

2023-08-15 14:06:48

时间采样实现2.1 系统硬件实现框图系统的总体框图如图2,FPGA 控制的等效采样时钟连接到ADC 器件的时钟部分,ADC 器件在时钟的控制下对宽带模拟信号进行采样,采集到的数据传送到FPGA 中

2020-10-21 16:43:20

)采样频率大于2倍信号最高频率后可以无失真的恢复出原始信号实际中,信号往往是无线带宽的,如何保证带宽有限?所以,我们在模拟信号输入端要加一个低通滤波器,使信号变成带宽有限,再使用2.5~3倍的最高信号

2015-11-26 16:22:01

简介与系统模拟输入和输出节点交互作用的外置高压瞬变可能破坏系统中未采用充分保护措施的集成电路(IC)。现代IC的模拟输入和输出引脚通常采用了高压静电放电(ESD)瞬变保护措施。人体模型(HBM

2018-10-23 11:48:14

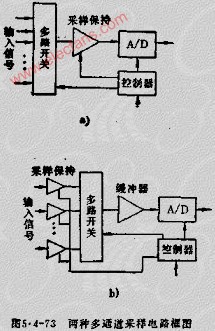

;⑤ 数字信号和模拟信号。(2)按输入通道结构划分有:① 单通道信号采集系统;② 多通道信号采集系统。(3)按系统性能划分有:① 高速数据采集系统与中、低速数据采集系统;② 集中式系统与分布式系统

2018-01-04 17:04:51

系统电源供电是:24V开关电源-->DC-DC(12V)-->7805-->AMS117-3.3示波器测试AMS1117纹波峰峰值:180MV某个管脚进行ADC采样外部电压,ADC

2019-01-11 09:37:11

请问CS1238进行ADC采样的时候,模拟电压的输入范围是多少?

2020-08-27 18:08:09

通用的输入采样结构有哪几种?每种输入采样结构对系统其它部分有什么影响?

2021-04-22 06:20:56

等效时间采样中应用的ADC,应该注意哪些问题呢?一般采样速率有何限制?对于ADC的模拟输入带宽呢?

2018-11-26 09:46:09

;当Vc为保持电平时,开关S断开,输出电压Vo保持在模拟开关断开瞬间的输入信号值。高输入阻抗的缓冲放大器的作用是把CH和负载隔离,否则保持阶段在CH上的电荷会通过负载放掉,无法实现保持功能。二、采样/保持器的基本结构1、串联型2、反馈型3、电容校正型来源:CSDN

2011-07-28 10:21:06

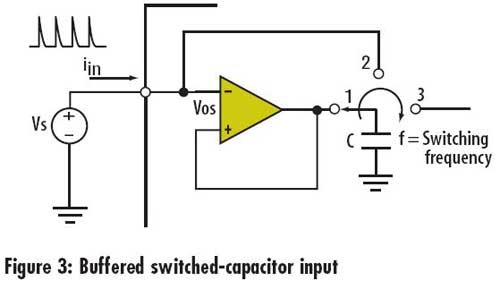

采用高速模数转换器(ADC)的系统设计非常困难,对于输入有两类ADC架构可供选择:缓冲型和无缓冲型。

缓冲和无缓冲架构的特征

高线性度缓冲器,但需要更高的功率;

更易设计输入网络与高阻抗缓冲器接口

2023-12-18 07:42:00

来源 网络采用高速模数转换器(ADC)的系统设计非常困难,对于输入有两类ADC架构可供选择:缓冲型和无缓冲型。 缓冲和无缓冲架构的特征 缓冲架构的基本特征 * 高线性度缓冲器,但需要更高的功率

2018-01-23 16:01:44

采用高速模数转换器(ADC)的系统设计非常困难,对于输入有两类ADC架构可供选择:缓冲型和无缓冲型。 缓冲和无缓冲架构的特征缓冲架构的基本特征高线性度缓冲器,但需要更高的功率;更易设计输入网络与高

2018-09-17 15:38:24

采用高速模数转换器(ADC)的系统设计非常困难,对于输入有两类ADC架构可供选择:缓冲型和无缓冲型。缓冲和无缓冲架构的特征缓冲架构的基本特征*高线性度缓冲器,但需要更高的功率;*更易设计输入网络与高

2018-10-18 11:23:57

提出了一个欠采样中频收发器的体系结构,它在中频数字化以前先通过欠采样将中频频率变到一个较低的频率。该结构在ADC 之前不需要镜像抑制滤波器且只有一条模拟路径,通过

2009-08-10 08:57:32 24

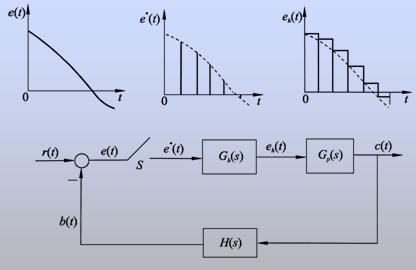

24 本文针对离散状态时滞系统,首先将其变形为无时滞形式,设计出最优控制器;然后运用离散提升技术对输入进行多采样,得到扩展的离散系统模型,再运用最优控制技术对扩展系

2009-08-10 10:53:15 16

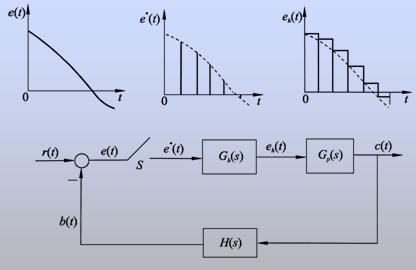

16 采样系统典型结构图

2009-01-08 14:19:46 1407

1407

什么是过采样

过采样是使用远大于奈奎斯特采样频率的频率对输入信号进行采样。设数字音频系统原来的采样频率为fs,通常为44.1kHz或48kHz

2009-05-04 19:27:55 4258

4258

模拟前端(AFE),模拟前端(AFE)系统的结构

模拟前端处理的对象是信号源给出的模拟电视、模拟声音信号,其主要功能包括以下几个方面:

2010-03-22 16:59:58 3026

3026 3路模拟输入“或”峰值选择电路

电路的功能

本电路是一种输入单极

2010-05-05 15:30:23 811

811

采样电路的概述

采样电路,具有一个模拟信号输入,一个控制信号输入和一个模拟信号输出。该电路的作用是在某个规定的时刻接收输入电压,并在输出端

2010-05-23 17:36:09 2735

2735

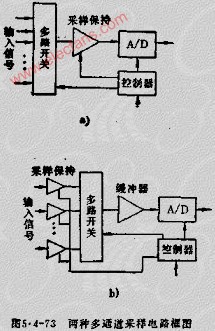

多通道采样电路结构

由于输入信号的数目,输入信号的电平和采样速度快慢的不同,多通道采样电路的结构不

2010-05-23 18:54:51 958

958

电子发烧友为您提供微处理温度控制模拟VI定时结构的输入节点信息,欢迎您的浏览!

2011-06-20 09:22:21 870

870

介绍了单片机为核心构成的测控系统中,模拟电压采样测量及MD转换方法。详细介绍了AD转换芯片 ADC0809 的内部结构作时序及其使用方法,并给出了基于ADC0809构成的测控系统的硬件接口

2011-07-26 17:34:14 519

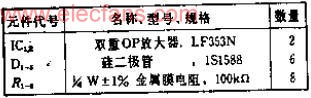

519 将一个经典的模拟累加器与一个采样保持放大器级联对一组模拟电压的采样进行保持。经典的模拟累加器是一个运放加上至少三只精密电阻。这些电阻的值应尽可能低,以避免影响累加

2012-04-01 10:53:12 4864

4864

ADC转换就是输入模拟的信号量,单片机转换成数字量。读取数字量必须等转换完成后,完成一个通道的读取叫做采样周期。采样周期一般来说=转换时间+读取时间。转换时间=采样时间+12.5个时钟周期。采样时间是你通过寄存器告诉STM32采样模拟量的时间,设置越长越精确。

2017-11-14 14:52:57 30137

30137 采样速率是指单位时间内,对输入信号进行采样的速度。对模拟输入信号的采样次数称为采样速率,也称为数字化率。本文主要详细介绍了ad7705最大采样速率以及它的参数和结构等。

2017-11-16 15:43:43 17733

17733

任何高性能ADC,尤其是射频采样ADC,输入或前端的设计对于实现所需的系统级性能而言很关键。很多情况下,射频采样ADC可以对几百MHz的信号带宽进行数字量化。前端可以是有源(使用放大器)也可以

2017-11-22 17:46:05 1009

1009

采样示波器也是非常常用的电子仪器,有四大功能: 1)高带宽示波器功能; 2)时域反射计TDR功能; 3)光眼图分析仪功能; 4)抖动分析仪功能。 采样示波器是高精度测试仪器,仪器结构原理图如图1所示

2017-11-23 05:44:01 947

947

本文设计的数据采集卡如图2所示。A/D转换器AD73360是一个包含6路模拟信号输入通道的器件,每路通道均包含独自的信号调理器、可编程放大器和16位的A/D转换部分。这样可实现对多路模拟信号的同时

2018-06-15 11:20:00 4365

4365

随着数字化的普及和技术的发展,A/D转换器的应用无处不见。在目前使用的众多 CMOS A/D转换器中,一种常用解决方案是使用 开关电容结构实现输入采样。在这种最基本的结构中,输入部分由一只体积相对

2018-05-11 11:57:00 10054

10054

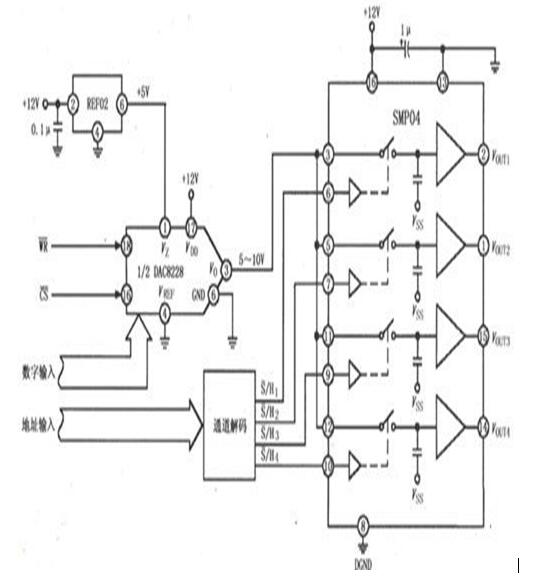

本参考设计展示了一种基于顺序多路选择采样保持缓冲器的低成本、高速、小型、高分辨率的PLC 模拟输出模块设计。

2018-05-11 15:43:16 6

6 关键词:SMP04 , 采样保持放大器 , 多路输出 , 选择器 如图所示为SMP04用做多路输出选择器,与***、D/A转换器构成的四路数字-模拟转换电路。数字信号输入模数转换器DAC8228

2019-01-31 07:46:01 272

272 输入系统的有正有负的模拟信号在AD采样前,会加上了直流偏置变成全正信号才输入AD的,所以在AD采样后送给FPGA的信号是无符号数。

2019-08-11 11:43:39 2821

2821 采样保持器是一种用逻辑电平控制其工作状态的器件,是计算机系统模拟量输入通道中的一种模拟量存储装置。

2020-01-15 11:42:16 18179

18179 采样保持电路能够跟踪或者保持输入模拟信号的电平值。在理想状况下,当处于采样状态时,采样保持电路的输出信号跟随输入信号变化而变化。

2020-03-31 16:48:01 1306

1306

任何高性能ADC,尤其是射频采样ADC,输入或前端的设计对于实现所需的系统级性能而言很关键。很多情况下,射频采样 ADC可以对几百MHz的信号带宽进行数字量化。前端可以是有源(使用放大器)也可以

2020-09-29 10:44:00 0

0 来源:罗姆半导体社区 模拟系统设计不仅需要选择正确的IC元件,还必须准确地预测这些元件在系统内的相互影响。从这点来看,模数转换器的设计是一个巨大挑战,因为它具有必须在系统级加以考虑的各种不同的输入

2022-11-15 15:52:12 428

428 AN-284:用模拟输入/输出端口实现无限采样保持电路

2021-04-22 16:19:39 12

12 路

常用的MUX的通道数是2路、8路和16路,在一些特殊应用,需要更多路的采样通道,比如64通道。对于64通道的模拟信号采样,如果采用8通道的MUX,方案整体上的资源需求如表1。可以看出,如果采用传统的结构

2022-01-12 15:28:17 929

929

一个逐次逼近寄存器 (SAR) 模数转换器 (ADC) 通常需要一个驱动器来驱动其模拟输入,以获得所需的精度效果。但是在较低数据吞吐量和较低分辨率应用中,你也许不需要驱动器。让我们来看一看SAR ADC的采样过程和模拟输入结构来了解驱动器的要求。

2022-01-28 09:32:00 2769

2769

在A/D转换器中,因为输入的模拟信号在时间上式连续的,而输出的数字信号代码是离散的。所以A/D转换器在进行转换时,必须在一系列选定的瞬间(时间轴上的一些规定点上)对输入的模拟信号采样保持,然后再

2021-11-11 12:36:05 3

3 一种拓展模拟采样通道数的方法

2022-10-28 12:00:19 0

0 选择电容时,根据电容的用途进行选择,比如储能、滤波、旁路、去偶、负载、高频、低频等。比如集成电路电源输入端与地之间通常接个电容,该电容属于旁路电容,其作用是将电源的高频杂波过滤,消除电源输入的杂波对芯片造成影响。

2022-12-07 15:03:53 837

837 与系统模拟输入和输出节点相互作用的外部高压瞬变如果没有得到充分保护,可能会损坏系统内的集成电路(IC)。现代IC的模拟输入和输出引脚通常具有高压静电放电(ESD)瞬变保护。人体模型 (HBM)、机器

2023-01-03 13:54:10 623

623

。 实际中,信号往往是无线带宽的,如何保证带宽有限?所以,我们在模拟信号输入端要加一个低通滤波器,使信号变成带宽有限,再使用2.5~3倍的最高信号频率进行采样。关于此我们下面将模拟数字转换过程将会看到。 虽说是不能小于等于2倍,但选2倍是不是很好呢,理论

2023-06-04 10:55:02 347

347

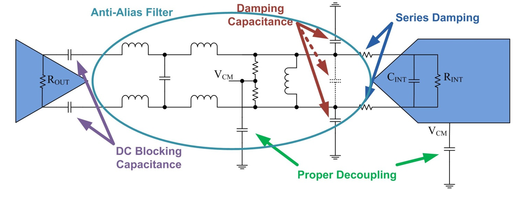

抗混叠滤波器用于帮助防止噪声和谐波从转换器中的其他奈奎斯特区混叠回目标频带。这有助于降低整体系统噪声,并过滤任何可能从系统其他位置耦合到模拟输入端的噪声。阻尼电容与串联阻尼电阻一起有助于减少从ADC开关电容输入采样网络“反冲”的电流瞬变。

2023-06-30 17:02:16 419

419

什么是数字滤波器的采样速率?和输入信号的频率有什么关系? 数字滤波器的采样速率是指数字滤波器输入信号的采样频率,也称为采样率,通常用赫兹(Hz)表示。在数字信号处理中,为了实现对模拟信号的数字化

2023-10-20 15:02:30 1385

1385 参数,它是指非常小的直流电流,通常指电路的输入项,用来控制电路的放大器的初始偏置电流。虽然它很小,但它却可以对电源采样调理电路产生重要影响。 为什么存在输入偏置电流? 在操作放大器中,输入偏置电流是由晶体管内部结构不完美造成的。因为晶体管的物理特性和加工过程,晶

2023-10-29 11:45:46 1211

1211 整定(调参)。 采样周期选择 采样周期指的是 PID控制中实际值的采样时间间隔,其越短,效果越趋于连续,但对硬件资源的占用也越高。在实际的应用中,我们可以使用理论或者经验方法来确定采样周期: ① 理论方法:香农采样定理。 这个定理可以用来确

2023-11-14 17:12:52 901

901

电子发烧友App

电子发烧友App

评论