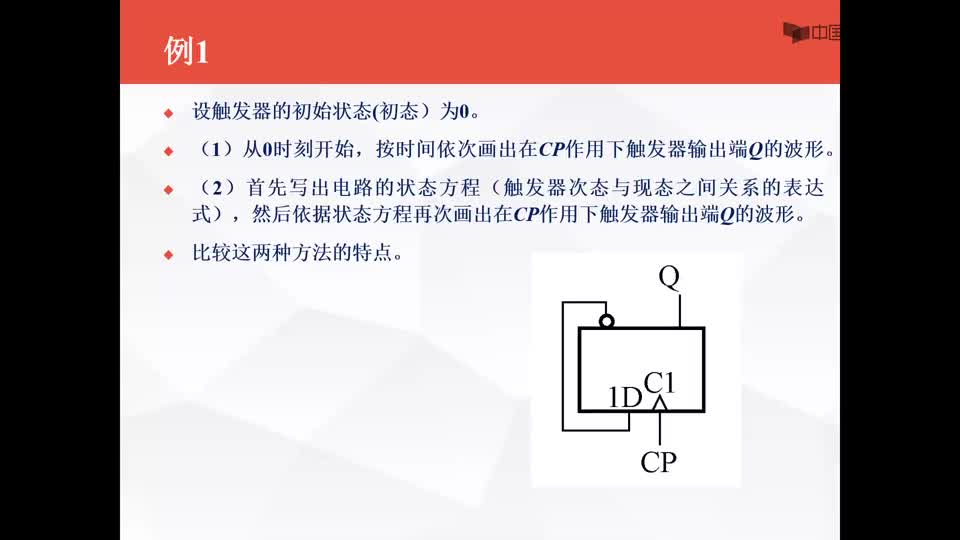

上例图中A将D触发器的D端和Q相连,即可组成二分频电路,如果把三个D触发器串行相连,如图所示,则经过一

2010-09-20 03:40:48 12045

12045

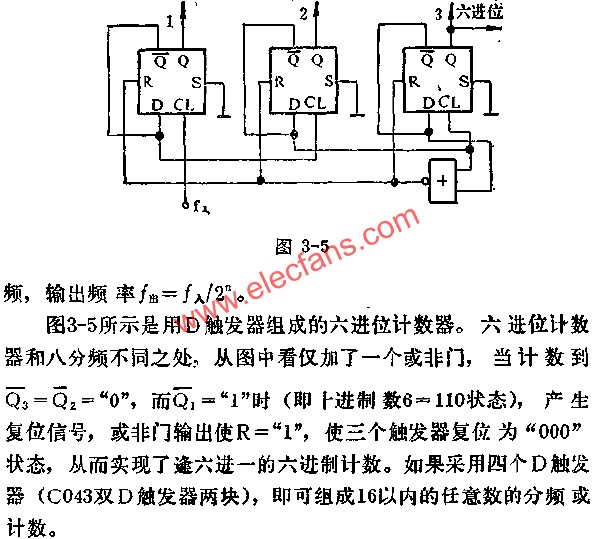

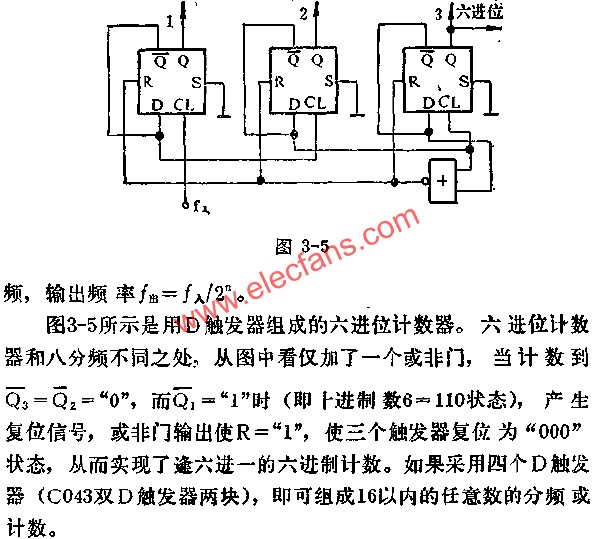

由3 个D 触发器和少量逻辑门构成, 采用了同步工作模式, 其原理是由吞脉冲计数原理产生2 个占空比不同的五分频信号A 和B

2011-11-25 15:16:42 30810

30810

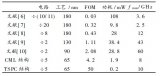

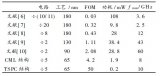

基于4/5双模SCL分频结构设计了一个高速、低压、低功耗的32/33双模前置分频器。该设计基于TSMC90nm1P9M CMOS工艺,利用Mentor Graphics Eldo工具仿真,结果表明该

2010-05-28 13:37:48

概述:CD4060是一款14级二进制串行计数/分频器,它是由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。所有的计数器位均为主从触发器。

2021-04-08 07:40:14

7w74D触发器的功能是什么?怎么控制?

2014-05-05 13:31:57

,呵呵。。。上半年,由于Boss项目,学习了FPGA,学的有点急,也断断续续的,才过几个月,似乎知识已经远去,打开电脑,速览以前的资料,记忆又回来了。。。简单记录下这道题,权当回忆。。。//基本D触发器

2012-02-22 13:54:40

本帖最后由 gk320830 于 2015-3-7 11:16 编辑

Ti的D触发器SN74LVC2G74,想做一个按键开关机电路,即二分频电路,但是调试过程中老是有问题,请大家帮忙分析分析

2013-10-30 15:44:27

D触发器实现二分频电路(D触发器构成的2分频电路)

2020-03-02 11:05:49

D触发器组成的_2N_1_2分频电路,几种奇数分频电路设计

2012-05-23 19:34:41

做了一个仿真:key_in作为D触发器的输入,led_out作为触发器输出,时钟周期20ns,key_in每10ns随机变化一次,这样的设置下,key_in信号的变化沿有时会和时钟上升沿重合,根据

2022-01-25 22:41:02

深亚微米的CMOS工艺制造高速分频器。由于CMOS器件的价格低廉,因而高速CMOS分频器有着广阔的市场前景。那分频电路由什么构成?你们知道2.4GHz动态CMOS分频器设计难吗?

2021-04-07 06:17:39

分频器EDA设计代码···仅供参考···

2013-12-09 12:26:46

不变。所以,触发器可以记忆1位二值信号。根据逻辑功能的不同,触发器可以分为RS触发器、D触发器、JK触发器、T和T′触发器;按照结构形式的不同,又可分为基本RS触发器、同步触发器、主从触发器和边沿触发器。

2009-09-16 16:06:45

触发器实验1)熟悉常用触发器的逻辑功能及测试方法。2)了解触发器逻辑功能的转换。三.实验内容及步骤 (1) 基本RS触发器逻辑功能测试(2) JK触发器逻辑功能测试(3) D触发器逻辑功能的测试

2009-03-20 10:01:05

按逻辑功能不同分为:RS触发器、D触发器、JK触发器、T触发器。按触发方式不同分为:电平触发器、边沿触发器和主从触发器。按电路结构不同分为:基本RS触发器和钟控触发器。按存储数据原理不同分为:静态

2012-06-18 11:42:43

,也就是说先有时钟上升沿才有q的变化。如果下一个时钟上升沿没有到来,那么q的值就保持不变。因此,q的值是在时钟上升沿之后一点点变化。这就是D触发器,我们所有的FPGA电路都是基于这个结构来进行

2018-09-20 15:09:45

如图, 将j-k触发器用D触发器代替,刚入门 求教

2014-01-09 20:56:31

NB6L239MNEVB / D,SONET时钟分频器评估板。 NB6L239是差分接收器到差分LVPECL时钟分频器。电路板功能输出启用输出控制

2019-02-20 09:29:49

。 NB7V32M产生输入时钟的2分频输出副本,工作频率高达10GHz,抖动最小。复位引脚在上升沿置位。上电时,内部触发器将达到随机状态,复位允许系统中多个NB7V32M同步。 16mA差分CML输出提供匹配的内部50欧姆端接,当外部接收器以50欧姆端接至VCC时,可确保400mV输出摆幅

2019-02-20 09:41:47

jk触发器设计d触发器,根据原理图实现模8加1计数器,来源于西电慕课貌似这个软件只有5.0和5.12两个版本。在win10下拖曳器件会发生残影的现象,而且无法修改连线。虽然有自动连线功能但感觉线连

2021-07-22 08:39:47

求助谁能教设计一个D触发器

2014-12-24 22:54:35

方式不同分为:电平触发器、边沿触发器和脉冲触发器。按电路结构不同分为:基本RS触发器和钟控触发器。按存储数据原理不同分为:静态触发器和动态触发器。按构成触发器的基本器件不同分为:双极型触发器和MOS型

2019-12-25 17:09:20

`如图所示,图中第一个触发器D接第二个触发器的非Q端,这个时序图,整不明白啊,我的看法是:当第一个时钟信号高电平来的时候,第一个触发器的输出状态Q是不能判断的啊,因为D接在第二个触发器的非Q端。求大佬指点一下 这个图,是如何工作的?`

2019-01-16 11:50:35

双D型触发器构成的振荡器电路实致上是一个可以灵活控制的波形信号发生器,其结构为图1所示的一个由双D型触发器构成的振荡器。该振荡器的起振、停止可以控制,输出波形的相位和占空比也可以调节,其工作波形如图2所示。图2 波形发生器工作逻辑图

2009-05-25 00:41:49

触发器没有使用相同的时钟信号,需要分析哪些触发器时钟有效哪些无效分析步骤和同步时序电路一样,不过要加上时钟信号有关D触发器的例题抄自慕课上的一个题目,注意第二个触发器反相输出端同时连接到复位端JK

2021-09-06 08:20:26

74LS273最小TTL八角D型带透明触发器4013B标准CMOS双D型触发器40174B标准CMOS具有主复位功能的六角D型触发器使用D型触发器进行频分D型触发器的一个主要用途是用作分频器。如果将D

2021-02-03 08:00:00

时输出恒为0;当Setn和 Clrn都为高电平时,输出Q在时钟信号CLK的上升沿处被赋予输入D的值。图5.1是带异步置位和清零端的正边沿触发的D触发器的电路结构图,该逻辑电路的行为分析如下:原作者:语雀

2022-07-04 16:01:57

本帖最后由 weihu_lu 于 2014-6-19 16:25 编辑

作者:卢威虎1、前言 分频器是FPGA设计中使用频率非常高的基本单元之一。尽管目前在大部分设计中还广泛使用集成锁相环(如

2014-06-19 16:15:28

【摘要】:介绍了基于FPGA的任意分频系数的分频器的设计,该分频器能实现分频系数和占空比均可以调节的3类分频:整数分频、小数分频和分数分频。所有分频均通过VHDL语言进行了编译并且给出了仿真图。本

2010-04-26 16:09:01

双模前置小数分频原理是什么?如何对小数分频器进行仿真测试?

2021-04-29 07:29:41

触发器的逻辑功能教学难点 与非门组成的基本RS触发器的逻辑功能授课方法 讲授法教具仪器 教案教学过程、内容分析、授课提纲组织教学

2009-04-02 11:58:41

想要通过1路方波来产生4路相差90°的方波信号,目前单转差已经完成,但是差分再转IQ就不知道用什么方法了。因为频率很低,听说可以用D触发器2分频实现,但是具体要怎么弄呢,感觉只能分频,没法实现

2021-06-24 07:03:25

如何用D触发器实现2分频 原理在线等

2016-07-03 19:37:58

本帖最后由 gk320830 于 2015-3-5 20:47 编辑

如何用JK触发器构成D触发器 电路图来人给个图吧..

2011-11-14 15:21:03

NB7V33MMNGEVB,差分时钟分频器评估板。 NB7V33M是一个4分频时钟分频器,具有异步复位功能。差分时钟输入包含内部50欧姆端接电阻,可接受LVPECL,CML和LVDS逻辑电平

2019-02-21 09:44:22

单片机内部有大量寄存器, 寄存器是一种能够存储数据的电路, 由触发器构成。1.触发器触发器是一种具有记忆存储功能的电路, 由门电路组成。 常见的触发器包括: RS 触发器、 D 触发器和 JK触发器

2022-01-20 07:13:51

要设计小数分频PLL,基本架构已经确定:使用基于MASH111的DSM,双模预分频器+PScounter实现。现在遇到的问题是,不知道怎么把小数分频控制字经过DSM后的输出与整数分频控制字结合起来去控制(双模分频器+PScounter)可编程分频器此前没做过小数分频PLL,求助大佬们点拨一二

2021-06-24 07:20:38

的加法计数器设计实现。(3)实验内容:Ⅰ. 用VHDL设计一个数控分频器,利用QuartusⅡ进行编辑输入、编译及时序仿真。仿真时输入不同的预置值D,给出如图6-1的时序波形。图6-1 当给出不同输入值

2009-10-11 09:24:45

用Qn(t)表示现态函数,用Qn+1(t)表示次态函数。它们统称为状态函数,一个时序电路的主要特征是由状态函数给出的。三:时序电路的特征时序电路中记忆功能是靠触发器来实现的,我们设计和分析时序电路

2018-08-23 10:36:20

,也就是说先有时钟上升沿才有q的变化。如果下一个时钟上升沿没有到来,那么q的值就保持不变。因此,q的值是在时钟上升沿之后一点点变化。这就是D触发器,我们所有的FPGA电路都是基于这个结构来进行

2019-01-17 17:24:19

RT有没有比555定时器好的纯粹单稳态触发器封装还小点的

2013-03-18 11:58:04

Jack Kilby)和D(延迟)。典型的触发器包括零个、一个或两个输入信号,以及时钟信号和输出信号。一些触发器还包括一个重置当前输出的明确输入信号。第一个电子触发器是在1919年由

2019-06-20 04:20:50

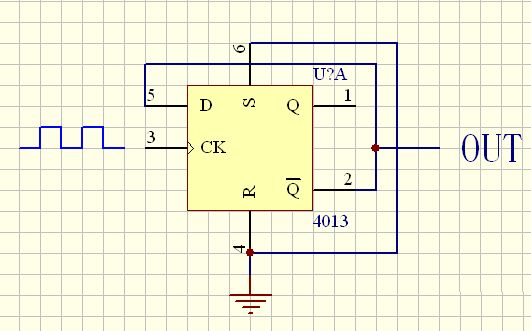

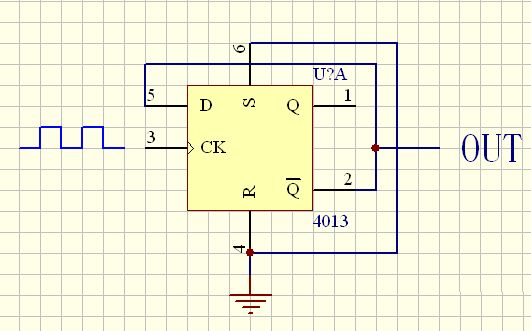

用CD4013双D触发器做的脉冲4分频器

2021-05-13 07:25:00

系统时钟,从而减少动态功耗。* 以高于或低于处理器的频率运行外设的状态机。* 设置发送/接收外设帧的波特率。本文阐述了目前SOC中各种可配置时钟分频器逻辑的实施方案,强调了各自的问题、优势及局限性。可配

2012-12-11 14:43:20

重新点亮。 7、接下来由于U1D已经处于锁定状态,输出端11脚的电平不再发生变化,D触发器也处于锁定状态,输出维持高电平。发光二极管维持导通。 注意: 本例属于数字电路的分析,分析过程比较简单,但是用文字描述比较繁琐,有发现描述错误的地方,还请指正。原作者:电子懒人

2023-03-20 15:33:48

电路为什么要有触发器这种结构?为什么要用时钟同步起来呢?一个乘法器如果不设计成触发的会是什么状态?最近在想电路同步异步的时候想到这个问题。

2016-12-08 17:41:52

D触发器结构的五分频器逻辑电路

2019-09-11 11:29:19

PWM预分频器、分频器和定时器的分辨率是多少?

2020-12-07 06:07:09

请问一下D触发器怎样实现四分频呢?

2023-05-10 14:34:08

本帖最后由 一只耳朵怪 于 2018-5-24 17:48 编辑

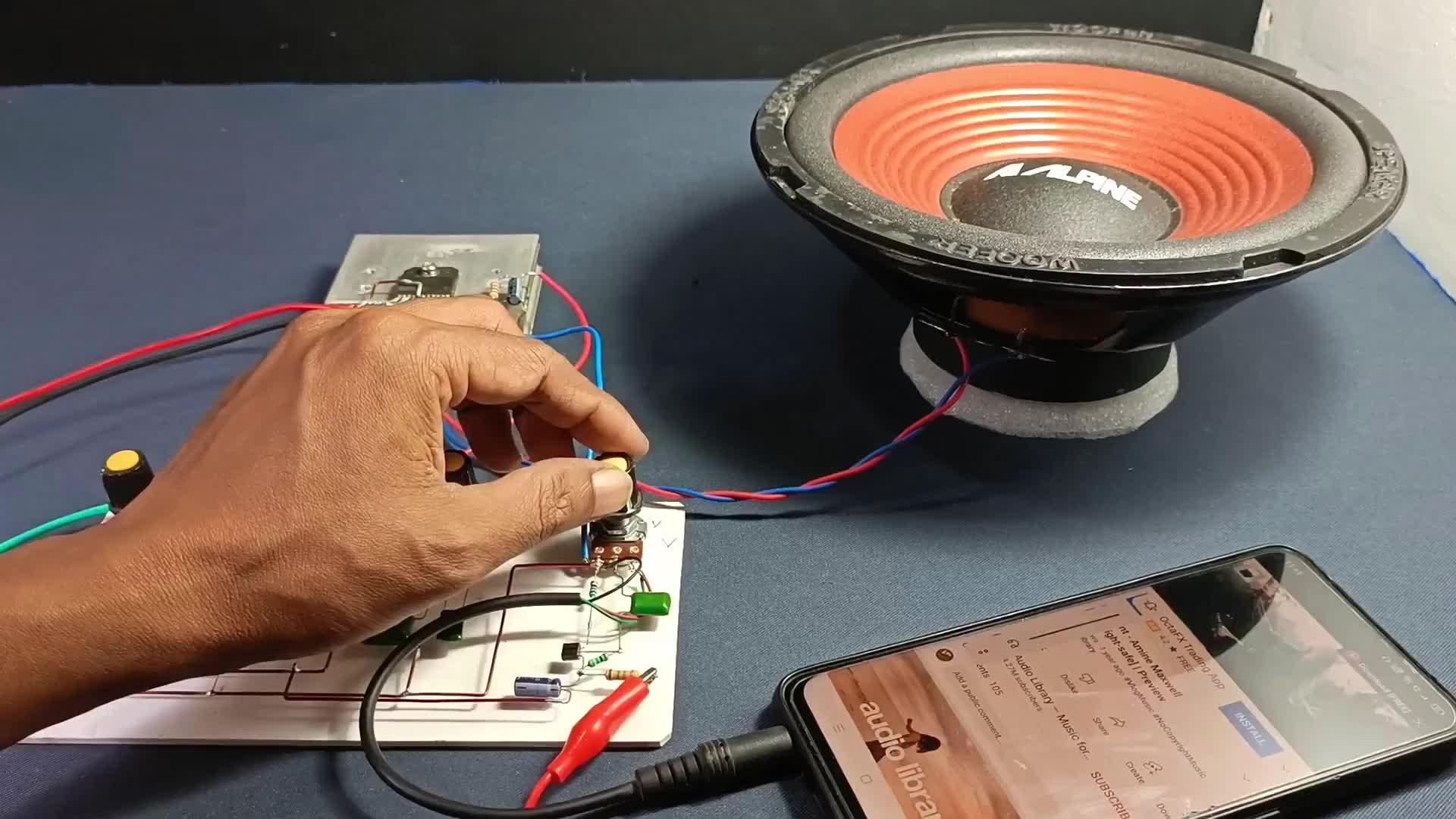

我想用D触发器做一个二分频电路,但是输出信号一直是1V,请问是什么地方出错了?谢谢。

2018-05-24 17:44:03

电平触发的D触发器型号有哪些?大部分都是边沿触发的,现在要用到电平触发器,不知道具体型号没法买到

2019-02-28 14:32:13

电平触发器和边沿触发器符号

2019-10-18 09:01:09

,我在我的项目中使用分频器IP内核,错误似乎取决于分频器输入和输出的宽度。如果我使用16位输出和16位小数输出,我得到正确的结果:切片逻辑分布:使用的LUT触发器对的数量:850带未使用的触发器的数量

2020-07-16 11:53:30

锁存器的工作原理是什么?锁存器的动态特性及其应用有哪些?触发器的工作原理是什么?触发器的电路结构是如何构成的?

2021-11-03 06:48:50

提出了一种通用的可编程双模分频器,电路主要由3 部分组成: 9/8 预分频器,8 位可编程计数器和ΣΔ调制器构成。通过打开或者关断ΣΔ 调制器的输出来实现分数和整数分频两种工作

2010-04-23 08:39:35 30

30 1、掌握锁存器、触发器的电路结构和工作原理;

2、熟练掌握SR触发器、JK触发器、D触发器及T 触发器的逻辑功能;

3、正确理解锁存器、触发器的动态特性

2010-08-18 16:39:35 0

0 cd4013双d触发器

CD4013双D触发器做的脉冲4分频器应用

-----------------------------. ┌─────

2008-01-09 23:48:45 4808

4808

具有奇次和偶次分频的分频器

2009-04-11 10:22:12 880

880

由R-S触发器构成的分频器

2009-04-11 10:28:43 961

961

D触发器实现二分频电路(D触发器构成的2分频电路)&

2009-06-12 13:58:56 75438

75438

d触发器构成2分频电路

2009-06-22 07:36:33 7781

7781

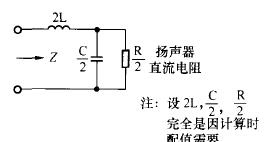

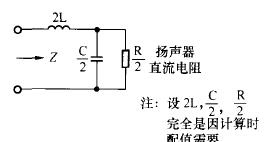

二阶分频器低通单元电路

二阶(双元件)低通分频器电路结构如图1所示。

2009-12-21 18:48:26 3121

3121

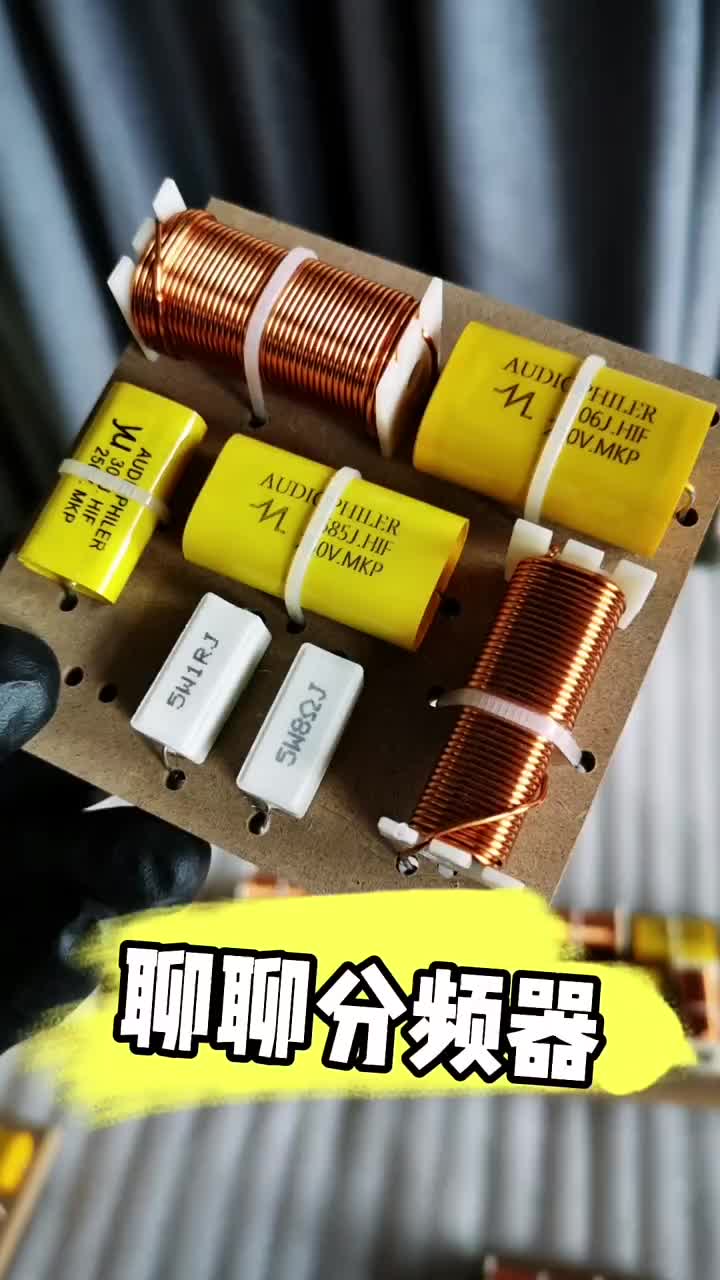

什么是分频器 分频器介绍

分频器是指将不同频段的声音信号区分开来,分别给于放大,然后送到相应频段的扬声器中再进行重放

2010-02-05 17:51:10 3676

3676 本文采用动态TSPC结构,利用TSMC 90nm 1P9M 1.2VCMOS工艺,设计了一个适用于WLAN IEEE802.11a标准的双模前置分频器,具有高速、低压、低功耗的特点。

2011-03-29 10:56:07 1401

1401

前置分频器是PLL中重要的部分。本文在研究和分析国内外3G系统结构基础上,选定零中频结构收发信机中本振PLL反馈回路上分频模块作为研究对象,实现射频模式下准确小数级分频。

2011-06-15 09:56:02 2511

2511

本内容介绍了采用新触发器的高速CMOS 前置分频器 ,欢迎大家下载

2011-07-26 18:05:25 37

37 分析了应用于倍频电路的预置可逆分频器的工作原理,推导了触发器的驱动函数。并建立了基于simulink 和FPGA 的分频器模型,实验结果表明分频器可以实现预置模和可逆分频功能,满足倍

2011-08-17 16:50:45 1896

1896

介绍了一种基于FPGA的双模前置小数分频器的分频原理及电路设计,并用VHDL编程实现分频器的仿真.

2011-11-29 16:43:06 48

48 。模拟分频器可由注进锁定等结构实现,一般具有工作频率高、功耗低等优点,但是分频范围较小,芯片面积较大。数字分频器基于触发器结构,一般分频范围较宽,芯片面积较小,但相对于模拟分频器其工作频率较低,功耗较大。这里采用

2017-11-17 15:54:22 8

8 采用基于D 触发器结构的五分频器逻辑框图如图1所示。图1 由3 个D 触发器和少量逻辑门构成, 采用了同步工作模式, 其原理是由吞脉冲计数原理产生2 个占空比不同的五分频信号A 和B, 然后对时

2018-04-18 14:04:00 8533

8533

中,压控振荡器(VCO)和前置分频器(Prescaler)是工作在最高频率的两个模块,它们是限制 PLL工作频率的主要瓶颈,因此提高前置分频器的工作速度是解决限制PLL工作频率上限的一个关键因素。

2017-12-10 03:30:01 1725

1725

分频器分为主动式、被动式、脉冲分频器三种。主动式电子分音器的原理就是要把适当频率讯号传给适当的单体,被动式分音器“功能、用途”是介于扩大器与喇叭之间,由于单一喇叭无法达到“全频段响应”,脉冲分频器利用汉稳态电路的计数功能实现分频的电路,又称为数字分频器。

2018-01-10 15:36:20 10793

10793 本文首先介绍了什么是分频器,其次阐述了音箱箱体及音箱分频器结构和原理,最后介绍了音箱分频器特点和作用。

2018-05-25 17:47:16 11406

11406

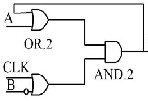

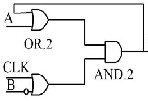

为f1的脉冲信号输入时,电路输出为频率f2的方波,分频系数为: N=f1/f2,其中N是偶数。 门G1和G2构成触发器。输入脉冲只对禁止门起作用,使触发器改变状态。最简单的情况是N=2,这样,每个输入脉冲改变触发器状态一次。对于较高的分频系数N,可以不用外加电容,因为CMOS门有5pF的固

2018-10-03 18:28:02 1856

1856 ,计数器的“借位”输出除驱动触发器SN7476外,还作为SN74193的寄存输入脉冲。五位二进制数加在D0、D1、D2、D3、D4输入端,由它确定分频系数(2~32)。其中,D0是最低位。当D0=1时,多路调制器输出脉冲的相位则根据触发器的状态确定。触发器Q输出为“0”时,多路调制器的输出与钟

2018-10-03 18:34:01 589

589 关键词:S8424 , 分频器 , 分频系数 如图所示为分频系数可变的分频电路。该分频器由R-S触发器、门电路和二-八进制拨盘开关组成,可以进行1~8分频。图中的8058是二-八进制拨盘开关

2018-10-03 18:37:02 427

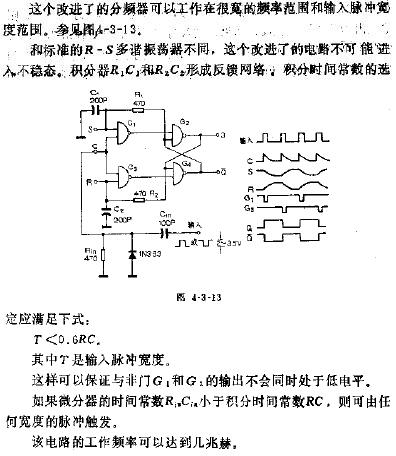

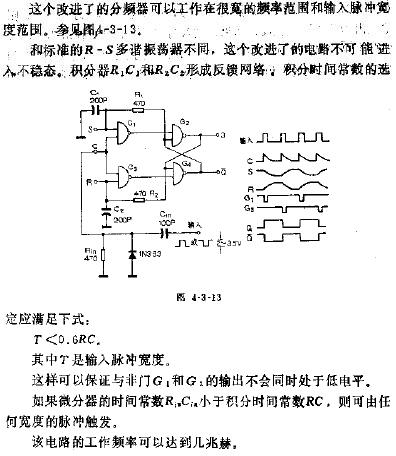

427 关键词:R-S触发器 , SN7442 , 分频器 如图所示为由R-S触发器构成的分频电路。该电路可以工作在很宽的频率范围和输入脉冲宽度范围。与标准的R-S多谐振荡器相比,该电路进行改进后,不可能

2018-10-08 09:00:01 419

419 论文分析了双模前置小数分频器的分频原理和电路实现。结合脉冲删除技术,提出了一种适于硬件电路实现的任意小数分频的设计方案 ,用 VerilogHDL语 言编程 ,在 QuartusII下对 此方案进 行 了仿 真 ,并用 Cyclone 系 列 的 EP1C12Q240C8芯 片来 实 现 。

2019-08-02 08:00:00 5

5 计算机的时钟节拍、频率分频、数据传输的帧同步等等。计数器可以通过级联多个RS触发器来实现,其中每个触发器的输出作为下一个触发器的输入。 频率分频器 RS触发器可以用于构建频率分频器电路。频率分频器可以将一个输入信号的频率减小为

2023-11-17 16:03:44 751

751

电子发烧友App

电子发烧友App

评论