资料介绍

电子产品中数字信号处理(DSP)芯片的使用率正急剧增加。现场可编程门阵列(FPGA)可支持数百万个门,并以DSP为中心,这种特性使其性能比标准的DSP芯片有了大幅提升。此外,FPGA还可进行中小型批量生产,能支持非常强大的原型设计与验证技术,以实现DSP算法的实时仿真。但为FPGA和ASIC创建可移植性算法IP也面临着诸多挑战与要求。

本文将介绍如何通过ESL综合技术大幅缩短在FPGA或ASIC上实现算法所需的时间,并简化相关工作。

FPGA和ASIC之间RTL移植所面临的挑战

尽管RTL支持逻辑级的移植性,但却不支持架构层移植。如果将同一RTL在不同的目标器件上实现,会导致结果不够理想;在不同目标器件中,综合结果可能在功能上正确,但却根本没有优化。

如何选择算法架构取决于一个基本问题,即满足算法的采样率和吞吐能力要求,需要进行多少流水线、并行和串行优化处理。此外,FIR、FFT、正弦、余弦、除法等基本的DSP功能根据目标技术的不同,有着不同的优化实现要求。比如,FIR滤波器的直接形式与转置形式(transposed form)就是一个很好的例子,一种适用于特定的FPGA器件,而另一种则更适用于ASIC技术。

根据FPGA和ASIC的不同要求,我们往往需要不同的架构。众所周知,FPGA器件倾向于以寄存器为中心,而许多ASIC到FPGA移植指南也建议增加流水线设计,对所有端口进行寄存,并将组合逻辑分解为较小的部分。这样的设计在ASIC上实现就会增加面积,但这是满足FPGA时序要求所必需的。

如果以ASIC为目标,我们往往需要完全相反的做法。这时我们建议将寄存器最小化,以尽可能减小占用面积与功耗。我们可以采用时分复用和资源共享的办法来提高时钟速度,从而最小化乘法器及其他浪费资源的操作。消费类及无线产品市场领域中的近期设计趋势就是仔细平衡上述做法的结果。

ASIC RTL和FPGA RTL之间不可避免的差别之一在于存储器的使用。就FPGA而言,器件内置了标准存储器。根据FPGA工具流程和厂商的不同,我们需要特定的编码风格来描述存储阵列和存储器。高质量FPGA综合工具会自动将RTL代码映射到存储器上实现。不过,在ASIC领域中,IP和制造库厂商(fab library vendor)的存储器选项多种多样,用户要根据具体的配置选择和编辑存储器,并在RTL设计中进行例化。

许多文章和资料都介绍了在 FPGA 和 ASIC 之间转移 IP 的编码风格及移植技术问题。在不同器件类型之间移植实施方案,需要进行大量的编码与验证工作,并拥有精湛的的专业技术。

如果首先用FPGA进行原型设计,再移植为ASIC设计,那么还要面临更多的挑战。在需要实时刺激和实际速度验证的情况下,就会出现上述问题。为了满足上述要求,我们应当保证仿真模型之间的位和采样准确度,特别是FPGA实现和ASIC模型不能出问题。这要求我们做大量工作,尤其是实现方案不同或经常变化时更应如此。此外,我们还必须手动修改、比较和调试测试工具。

ESL 综合解决方案

ESL 综合解决方案能提供强大的性,有助于解决上述诸多问题。

● 使用电子系统层级 (ESL) 模型,支持高级架构与硬件抽象;

● 根据用户定义的采样率进行自动优化;

● 用户选择目标技术;

● 为多速率设计提供原生支持。

图1 从统一 ESL 模型快速实现设计方案

利用上述特性,DSP 综合引擎可根据用户定义的约束条件在了解目标的基础上进行整个系统优化,对不同的 RTL进行综合。这些为优化架构和特定编码风格而定的RTL 随后可进入标准化的逻辑综合流程。

利用ESL综合技术,我们可以在一个高度抽象的层面完成设计工作,这不仅提高了可移植性,缩短了开发时间,而且还提高了工程设计的工作效率。除了保持RTL级的IP之外,我们还能在算法模型层保持IP,从而提高可移植性以及算法开发人员的工作效率。

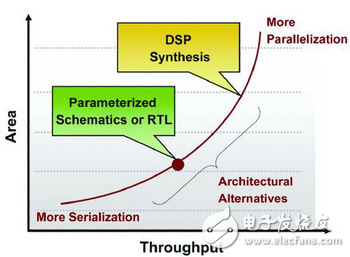

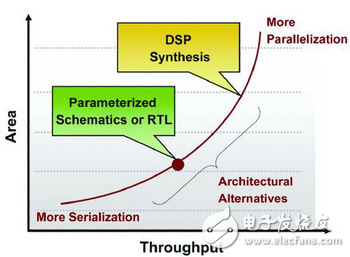

如图1所示,DSP综合技术使用户能通过统一的算法模型快速生成并实现多种不同实施方案。FPGA可使用完全并行的流水线架构,也可像ASIC一样采用占用面积更小的串联架构。此外,不同实施方案能自动保持位和采样的准确度,并通过标准化的RTL仿真工具实现完整的验证路径。与此形成对比的是,参数化的原理图输入法,和那些需要用户在了解面积、延迟特性之前就确定具体架构的RTL方法,其移植到新的实施目标时往往需要进行大量的修改。

本文将介绍如何通过ESL综合技术大幅缩短在FPGA或ASIC上实现算法所需的时间,并简化相关工作。

FPGA和ASIC之间RTL移植所面临的挑战

尽管RTL支持逻辑级的移植性,但却不支持架构层移植。如果将同一RTL在不同的目标器件上实现,会导致结果不够理想;在不同目标器件中,综合结果可能在功能上正确,但却根本没有优化。

如何选择算法架构取决于一个基本问题,即满足算法的采样率和吞吐能力要求,需要进行多少流水线、并行和串行优化处理。此外,FIR、FFT、正弦、余弦、除法等基本的DSP功能根据目标技术的不同,有着不同的优化实现要求。比如,FIR滤波器的直接形式与转置形式(transposed form)就是一个很好的例子,一种适用于特定的FPGA器件,而另一种则更适用于ASIC技术。

根据FPGA和ASIC的不同要求,我们往往需要不同的架构。众所周知,FPGA器件倾向于以寄存器为中心,而许多ASIC到FPGA移植指南也建议增加流水线设计,对所有端口进行寄存,并将组合逻辑分解为较小的部分。这样的设计在ASIC上实现就会增加面积,但这是满足FPGA时序要求所必需的。

如果以ASIC为目标,我们往往需要完全相反的做法。这时我们建议将寄存器最小化,以尽可能减小占用面积与功耗。我们可以采用时分复用和资源共享的办法来提高时钟速度,从而最小化乘法器及其他浪费资源的操作。消费类及无线产品市场领域中的近期设计趋势就是仔细平衡上述做法的结果。

ASIC RTL和FPGA RTL之间不可避免的差别之一在于存储器的使用。就FPGA而言,器件内置了标准存储器。根据FPGA工具流程和厂商的不同,我们需要特定的编码风格来描述存储阵列和存储器。高质量FPGA综合工具会自动将RTL代码映射到存储器上实现。不过,在ASIC领域中,IP和制造库厂商(fab library vendor)的存储器选项多种多样,用户要根据具体的配置选择和编辑存储器,并在RTL设计中进行例化。

许多文章和资料都介绍了在 FPGA 和 ASIC 之间转移 IP 的编码风格及移植技术问题。在不同器件类型之间移植实施方案,需要进行大量的编码与验证工作,并拥有精湛的的专业技术。

如果首先用FPGA进行原型设计,再移植为ASIC设计,那么还要面临更多的挑战。在需要实时刺激和实际速度验证的情况下,就会出现上述问题。为了满足上述要求,我们应当保证仿真模型之间的位和采样准确度,特别是FPGA实现和ASIC模型不能出问题。这要求我们做大量工作,尤其是实现方案不同或经常变化时更应如此。此外,我们还必须手动修改、比较和调试测试工具。

ESL 综合解决方案

ESL 综合解决方案能提供强大的性,有助于解决上述诸多问题。

● 使用电子系统层级 (ESL) 模型,支持高级架构与硬件抽象;

● 根据用户定义的采样率进行自动优化;

● 用户选择目标技术;

● 为多速率设计提供原生支持。

图1 从统一 ESL 模型快速实现设计方案

利用上述特性,DSP 综合引擎可根据用户定义的约束条件在了解目标的基础上进行整个系统优化,对不同的 RTL进行综合。这些为优化架构和特定编码风格而定的RTL 随后可进入标准化的逻辑综合流程。

利用ESL综合技术,我们可以在一个高度抽象的层面完成设计工作,这不仅提高了可移植性,缩短了开发时间,而且还提高了工程设计的工作效率。除了保持RTL级的IP之外,我们还能在算法模型层保持IP,从而提高可移植性以及算法开发人员的工作效率。

如图1所示,DSP综合技术使用户能通过统一的算法模型快速生成并实现多种不同实施方案。FPGA可使用完全并行的流水线架构,也可像ASIC一样采用占用面积更小的串联架构。此外,不同实施方案能自动保持位和采样的准确度,并通过标准化的RTL仿真工具实现完整的验证路径。与此形成对比的是,参数化的原理图输入法,和那些需要用户在了解面积、延迟特性之前就确定具体架构的RTL方法,其移植到新的实施目标时往往需要进行大量的修改。

下载该资料的人也在下载

下载该资料的人还在阅读

更多 >

- 综合能源解决方案(空调+储能) 28次下载

- 基于DSP的开关功率放大器控制方案 17次下载

- 如何提高WINCC组态的效率 41次下载

- 手机电源管理设计系统方案的综合考虑资料下载 29次下载

- 终端区管制运行效率的集成综合评估模型 5次下载

- ESR,ESL,如何影响电容?资料下载 16次下载

- 如何提高功率因数校正的效率从待机到满负荷的详细解决方案概述 9次下载

- 基于诸智云的工业物联网解决方案详细资料免费下载 24次下载

- 便携式DSP解决方案中不同电源的比较 9次下载

- 基于DSP的电源解决方案 0次下载

- TI手提超声系统DSP解决方案 7次下载

- 航电数据通信综合解决方案 26次下载

- TI DSP行业应用解决方案 59次下载

- 基于GPS/GPRS网络的综合物流调度管理应用方案 22次下载

- 基于ESL方法的DSP微处理器行为模型设计 18次下载

- 高效率、易管理的智能照明解决方案 388次阅读

- 如何通过提高效率来提高CATV放大器的下行带宽和上行容量 1786次阅读

- 综合电源解决方案TPS84621RUQ的性能特性及应用 2256次阅读

- 如何才能提高隔离式电源的效率 1046次阅读

- 实现ARM和DSP或协处理器的通信和协同工作,有什么解决方案和实现指南 1401次阅读

- SMT贴片厂如何来提高加工生产效率 3629次阅读

- 信息娱乐系统中基于SAF775D芯片的音频解决方案 1.2w次阅读

- 采用SystemC ESL设计的九个理由 4549次阅读

- 提高太阳能逆变器设计的效率 2547次阅读

- 关于多电压轨FPGA和DSP应用的电源解决方案全解 978次阅读

- 教你如何提高LED的发光效率 2.4w次阅读

- 满足多种需求的DSP架构解决方案 2193次阅读

- 一种用AD7858提高DSP采样精度的新方法 1551次阅读

- 一种基于DSP的视频监控系统解决方案 3225次阅读

- 高清电视芯片的综合优化设计 1201次阅读

下载排行

本周

- 1东芝BiCD集成电路硅单片TB67S109AFNAG数据手册

- 1.93 MB | 5次下载 | 免费

- 2SP3060A/30120A/30160A/30320A/30520A系列数字合成扫频仪使用说明书

- 4.16 MB | 3次下载 | 1 积分

- 3具有双通道 DC-DC转换器、由串行接口控制的9通道电机驱动器TPIC2010数据表

- 1.15MB | 2次下载 | 免费

- 4USB Type-C PD快充协议智能触发芯片FS312B数据手册

- 0.75 MB | 1次下载 | 免费

- 5USB Type_C PD快充协议智能触发芯片FS8025B数据手册

- 1.29 MB | 1次下载 | 免费

- 6触摸按键PCB 设计要点V01

- 1.42 MB | 1次下载 | 免费

- 7超低噪声、高 PSRR、低压降线性稳压器 (LDO)TPS7H1111-SP和TPS111-SEP数据表

- 4.05MB | 1次下载 | 免费

- 8DC-DC电路(Buck)的设计与仿真

- 0.60 MB | 1次下载 | 2 积分

本月

- 1DCDC原理详解

- 0.98 MB | 65次下载 | 免费

- 2allegro快速入门教程

- 1.98 MB | 36次下载 | 免费

- 3FU-7(807)胆机原理图

- 11.93 MB | 25次下载 | 1 积分

- 4用于汽车应用的高压电源管理IC TPS65311-Q1数据表

- 1.05MB | 22次下载 | 免费

- 5电子元件基础知识介绍

- 8.76 MB | 15次下载 | 2 积分

- 6华为海思Ascend 310芯片的资料说明

- 0.12 MB | 10次下载 | 10 积分

- 7GD32F10x系列MCU用户手册

- 11.5MB | 9次下载 | 免费

- 86A 输出电流同步降压稳压器TPS65286数据表

- 2.05MB | 6次下载 | 免费

总榜

- 1matlab软件下载入口

- 未知 | 935083次下载 | 免费

- 2开源硬件-PMP21529.1-4 开关降压/升压双向直流/直流转换器 PCB layout 设计

- 1.48MB | 420045次下载 | 免费

- 3Altium DXP2002下载入口

- 未知 | 233067次下载 | 免费

- 4电路仿真软件multisim 10.0免费下载

- 340992 | 191308次下载 | 免费

- 5十天学会AVR单片机与C语言视频教程 下载

- 158M | 183308次下载 | 免费

- 6labview8.5下载

- 未知 | 81567次下载 | 免费

- 7Keil工具MDK-Arm免费下载

- 0.02 MB | 73785次下载 | 免费

- 8NI LabVIEW中实现3D视觉的工具和技术

- 未知 | 70088次下载 | 免费

电子发烧友App

电子发烧友App

创作

创作 发文章

发文章 发帖

发帖  提问

提问  发资料

发资料 发视频

发视频 上传资料赚积分

上传资料赚积分

评论