1、在总线连接的结构上。总线上挂有多个设备,设备于总线以高阻的形式连接。这样在设备不占用总线时自动释放总线(放弃对总线的使用),以方便其他设备获得总线的使用权。

2、大部分单片机I/O使用时都可以设置为高阻输入,如陵阳,AVR等等。高阻输入(类似于CMOS输入阻抗)可以认为输入电阻是无穷大的,认为I/O对前级影响极小,而且不产生电流(不衰减),而且在一定程度上也增加了芯片的抗电压冲击能力。

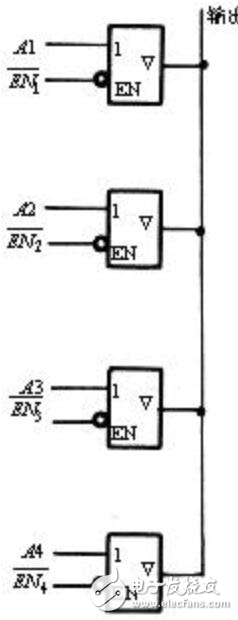

将74LS125的四个三态门的输出端接在一起,形成总线形式。如图所示。再将四个三态门电路的输入端分别接上不同的信号,然后将四个三态门的控制端分别依次接上低电平的控制信号,用示波器观察输出端的输出波形,并绘出相应波形。(注意:当一个控制端接上低电平时,其他的控制端必需接到高电平。)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

总线

+关注

关注

10文章

2706浏览量

87211 -

三态门

+关注

关注

0文章

30浏览量

18677

发布评论请先 登录

相关推荐

具有可配置电压转换和三态输出的8位双电源总线收发器SN74LVC8T245数据表

电子发烧友网站提供《具有可配置电压转换和三态输出的8位双电源总线收发器SN74LVC8T245数据表.pdf》资料免费下载

发表于 03-01 09:30

•0次下载

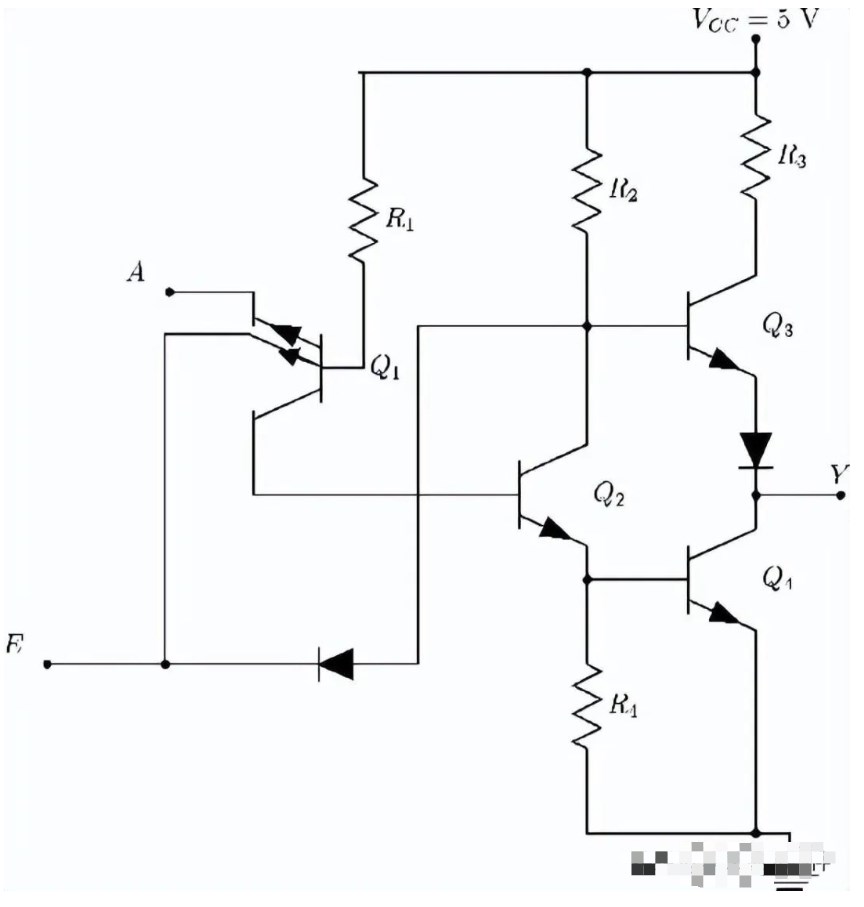

TTL三态门输出电路优点 TTL三态门输出电路图

TTL三态门输出电路是一种重要的接口元件,它能够提供三种输出状态:高电平、低电平和高阻态。这种电路在实现数字系统之间的连接和数据传输时起着至关重要的作用。

集电极开路输出的优缺点分析

1、集电极开路输出上拉电阻电路为什么会速度降低和噪声变大?在此基础出引出了三态门?

2、多集电极开路上拉电阻输出实现了线或结构,有高为低,全低为高。那么什么电路结构可以实现线与结构,射极跟随,推挽,互补或者其他简单输出电路?

发表于 01-28 16:32

XC7SH125总线缓冲器/线路驱动器;三态产品数据表资料

电子发烧友网站提供《XC7SH125总线缓冲器/线路驱动器;三态产品数据表资料.pdf》资料免费下载

发表于 01-05 09:40

•0次下载

51端口的结构及工作原理介绍

与上图相同的电路组成。下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器: 在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出

发表于 10-07 06:58

三态输出的缓冲器有哪些用途?

三态输出的缓冲器有哪些用途? 三态输出缓冲器是一种电子元件,其主要作用是将一个输入信号转换成一个可以控制多个输出设备的信号。这种缓冲器可以被用于一系列的应用,包括数码电路、计算机、消费电子设备、通信

ttl电路中推拉输出,集电极开路输出,三态输出有何不同?

ttl电路中推拉输出,集电极开路输出,三态输出有何不同? TTL电路是一种常见的数字逻辑电路,在电路中经常出现推拉输出、集电极开路输出、三态输出这些术语。这些输出方式在不同的电路中具有不同的意义

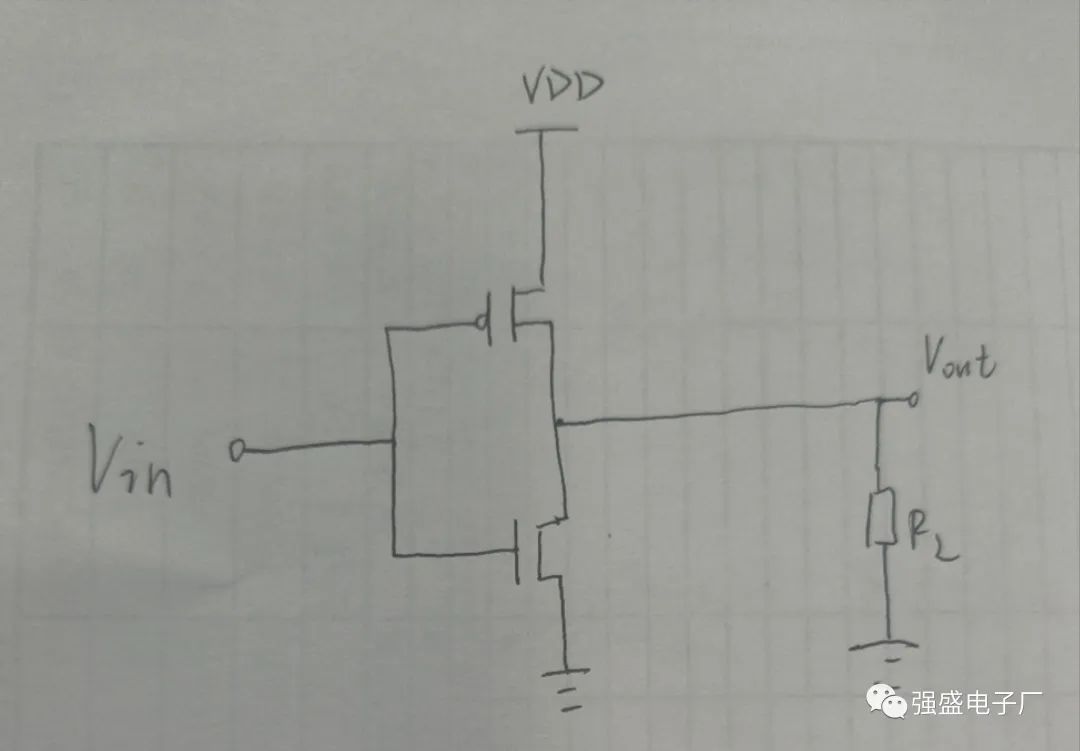

什么是三态电路?在FPGA上如何使用三态电路作为IO呢?

一般来说,我们认为CMOS数字电路的输出的稳定状态只有2种,就是逻辑0和逻辑1,从模拟信号量来说,就是0V和VDD。

发表于 08-01 16:32

•2514次阅读

Versal HDIO OBUFT和IOBUF三态时序影响

本文着重探讨 HDIO OBUFT 和 IOBUF 用例。如果含三态控制 (OBUFT/IOBUF) 的 HDIO 输出缓冲器的上电电压为 3.3 V 或 2.5 V 并且 Data(数据)控制信号与 Tristate(三态)控制信号的切换时间彼此相近,则可能会受到

推挽输出、开漏输出、三态输出原理详解

2020年在学校调单片机的时候,我第一次接触数字控制器的输入输出信号。当查阅其输入、输出描述时,推挽输出、开漏输出、三态输出这些概念我真的非常难以理解,为什么起这么奇怪的名字?不就是高低电平、高阻这么几个玩意吗?搞这么复杂。

三态门的应用

三态门的应用

评论