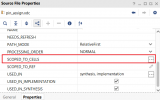

XDC 是 Xilinx Design Constraints 的简写,但其基础语法来源于业界统一的约束规范SDC(最早由 Synopsys 公司提出,故名 Synopsys Design Constraints)。XDC 在本质上就是 Tcl 语言,但其仅支持基本的 Tcl 语法如变量、列表和运算符等等,对其它复杂的循环以及文件 I/O 等语法可以通过在 Vivado 中 source 一个 Tcl 文件的方式来补充。观看视频,了解和学习有关XDC约束,包括时序,以及物理约束相关知识。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

32文章

1794浏览量

130514 -

语言

+关注

关注

1文章

97浏览量

24038 -

时序

+关注

关注

5文章

356浏览量

36955

发布评论请先 登录

相关推荐

FPGA物理约束之布局约束

在进行布局约束前,通常会对现有设计进行设计实现(Implementation)编译。在完成第一次设计实现编译后,工程设计通常会不断更新迭代,此时对于设计中一些固定不变的逻辑,设计者希望它们的编译结果

FPGA物理约束之布线约束

IS_ROUTE_FIXED命令用于指定网络的所有布线进行固定约束。进入Implemented页面后,Netlist窗口如图1所示,其中Nets文件展开后可以看到工程中所有的布线网络。

如何给每个RM添加约束?

在常规非DFX(DynamicFunction eXchange)的Vivado设计中,我们可能会碰到给某一个指定的模块添加特定的约束。这时一个简单的方法就是将这些约束单独写在一个.xdc或.tcl

FPGA时序约束之衍生时钟约束和时钟分组约束

在FPGA设计中,时序约束对于电路性能和可靠性非常重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的主时钟约束。

发表于 06-12 17:29

•1423次阅读

FPGA主时钟约束详解 Vivado添加时序约束方法

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

发表于 06-06 18:27

•7019次阅读

XDC约束及物理约束的介绍

XDC约束及物理约束的介绍

评论