在像PCIE这样的高频环境中,传送线在信号线上驱动电压变化时会出现阻抗,信号线的宽度和到接地的距离都会影响其阻抗,所以在设计PCB时需要参考PCIE总线规范,特别要注意考虑信号阻抗匹配。以下供设计PCB时作为参考:

● 插卡从金手指边缘到PCIE芯片管脚的走线长度应限制在4英寸(约100mm毫米)以内。超过该长度后需要使用高频差分传输线,我们可以提供延长300mm以上的技术方案。

● PCIE的PERPN,PETPN,PECKPN是三个差分对线,其中PECKPN是100MHz频率的差分信号线,需要注意保护,前两对是2.5GHz频率的差分信号线,更需要注意保护。

● 差分对线中的两条走线要同步布线。如果走线要转弯,那么两条走线应该同步转弯,并且转弯要避免锐角、直角,而应该使用弧线或者钝角转弯。

● 差分对线走线过程中尽量避免使用VIA过孔,如果一定要通过过孔换层,那么两条走线应该同步做过孔,并且应该在靠近信号对线过孔处放置GND地信号过孔,条件允许时适当增加周边GND地信号过孔数量。

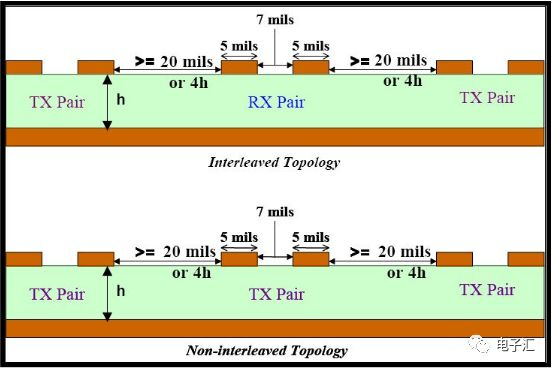

● 差分对线中的两条走线的长度差应该控制在5mil之内,最大10mil(约0.25mm)。PCB走线的线宽建议是7mil(约0.18mm),两条走线的净间距建议是7mil。有关线宽和线间距的详细分析请参考PCIE规范。

● 两对差分对线之间的距离(例如PER对与PECK对)、或者差分对线和其它非PCIE信号的距离,建议不小于20mil(约0.5mm),以减少相互之间的串扰和电磁干扰(EMI)的影响。建议在两对差分对线之间用GND地线隔离,例如,从左向右是:GND、PECK对线、GND、PER对线、GND、PET对线、GND。

● PCIE芯片,尤其是PCIE信号线的PCB反面,应该尽量避免走高频信号线,最好全GND地铺铜。例如,CH367芯片的SCL信号线、IORD信号线是相对的高频信号线,建议不要穿越PCIE芯片走线。

● PCIE需要在发送端(PETPN)和对方的接收端之间进行交流耦合,差分对的两个交流耦合电容必须有相同的封装尺寸,位置要对称,并且要摆放在靠近金手指这边。建议选择容量为0.1uF的高频电容,封装尺寸推荐使用0402,另外0603也可以接受,但是不允许使用直插封装的电容。

● 在设计PCB时,应该在PCIE芯片的每对电源引脚(VCC18GND、VCC33GND)附近放置一个容量为0.1uF左右的高频退耦电容,离芯片的距离不能太远。另外,整个芯片的VCC18和VCC33各需要一个容量不小于10uF的钽电容进行中低频退耦。

● 由于PCB过孔(VIA)电阻较大并且容易受长期高温老化影响而不稳定,为了减少其消耗的电压降,考虑到VCC18VCC33与GND之间的数百mA电流,建议连接PCIE芯片的电源或者GND走线上的过孔使用大过孔、双过孔或者使用双回路电源(两条路径)。

● 部分芯片组和主板支持PCIE板卡带电热插拔,为了支持带电热插拔,板卡设计时需要做两点额外处理:

一是设计电路原理图时,请在PCIE芯片的PERST#引脚信号线与GND之间跨接一个1000pF的贴片电容;

二是设计PCB时,请将PCIE的PERST#引脚信号的金手指设计为与PRSNT1#长度差不多的短金手指。

-

pcb

+关注

关注

4220文章

22472浏览量

385741 -

总线

+关注

关注

10文章

2706浏览量

87206 -

PCIe

+关注

关注

13文章

1083浏览量

80823

原文标题:[讨论]PCIE总线规范范例:PCI-Express板卡PCB设计

文章出处:【微信号:gh_f97d2589983b,微信公众号:高速射频百花潭】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何进行PCI-Express的一致性测试和分析

PCIE总线规范范例:PCI-Express板卡PCB设计

基于PCI-Express的高速数据交换设计及应用

PCI Express插槽,什么是PCI Express插槽

基于Virtex5的PCI-Express总线接口设计

PCI-Express插槽

从PCI、PCI-X到PCI-Express之间的连接

PCIE-PCB设计规范

PCIe及PCB设计要求

PCIE总线规范范例:PCI-Express板卡PCB设计

PCIE总线规范范例:PCI-Express板卡PCB设计

评论