引言

发电机组的功率-频率特性和励磁-无功(电压)特性是影响电力系统安全经济运行的最 重要的两组物理量。电力系统的频率主要取决于原动机的出力,系统频率变化是由于发电机 的负荷与原动机输入功率之间失去平衡所致。当频率下降较多时,对系统运行极为不利,甚 至造成系统崩溃的严重后果。因此精确快速测量发电机的转速关系到整个模拟系统动态性 能,是发电机原动系统中至关重要的一个参数。

目前常用的数字测速方法M\T法,本系统为了测量发电机的功角,必须在转轴上套一个 有两个齿的齿轮(由于动模实验室的发电机是两对磁极每分1500转),在每个测速周期内, 同时计取光电脉冲个数m1和时标脉冲个数m2。测速周期Td =Te+ΔT。其中Te是固定部分,而 ΔT是指从Te结束到下一个光电脉冲到来这段时间。用下式可以计算转速n。

n=A *m1/m2 (1)

A 是常数。

从上面的分析可以看出,采用M/T法测速,遇到的最大问题就是测速周期的不固定。ΔT 是不固定的,在原动机高速时ΔT较短,而在原动机低速时ΔT就会变得较长, 从而整个测速 周期也变得较长。这样就带来了两方面的问题。①由于低速运行时测速周期的变长,使得控 制周期变长,速度采样值长时间得不到更新,控制效果变差, 容易出现“爬行”等现象。②由于 低速运行时测速周期变长,使得时标脉冲的计数周期变长,如果不采用较长位数的计数器计取时标脉冲, 就会发生溢出。也就是说,一定位数长度的时标脉冲计数器对应着一定的可测 得的最低转速,要测出很低的转速,就需要很长位数的时标脉冲计数器,在式(1)中,m2是多字 节的数,计算式(1)需要做多字节的除法,增大了实时控制中的软件开销。该文提出了一种全 新的锁相测速方法,采用这种方法,无论原动机高速运行还是低速运行,都可以获得一个始终 跟随原动机转速值的14位的并行的测速结果,测速周期短,测量精度高。

1.1锁相环基本介绍

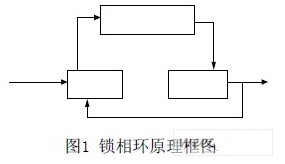

锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统 叫做锁相环,简称PLL(Phase Lock Loop )。其主要由相位比较器(PC)、压控振荡器(VCO)。 低通滤波器三部分组成,如图1所示。

压控振荡器的输出 Uo 接至相位比较器的一个输入端,其输出频率的高低由低通滤波器 上建立起来的平均电压 Ud 大小决定。施加于相位比较器另一个输入端的外部输入信号U i 与 来自压控振荡器的输出信号o U 相比较,比较结果产生的误差输出电压 U ψ正比于U i 和Uo 两 个信号的相位差,经过低通滤波器滤除高频分量后,得到一个平均值电压 Ud 。这个平均值 电压 U d朝着减小VCO输出频率和输入频率之差的方向变化,直至VCO输出频率和输入信号 频率获得一致。这时两个信号的频率相同,两相位差保持恒定(即同步)称作相位锁定。

当锁相环入锁时,VCO可在某一范围内自动跟踪输入信号的变化,如果输入信号频率 在锁相环的捕捉范围内发生变化,锁相环能捕捉到输人信号频率,并强迫VCO锁定在这个 频率上。

1.2锁相测速原理

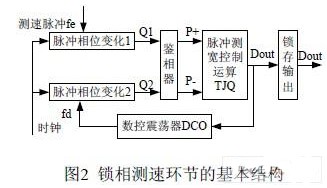

锁相测速环节的基本结构如图2示。

在图2中,来自光电传感器方波整形电路的脉冲fe与来自数字控制振荡器DCO的脉冲fd分 别经过“脉冲相位变换器1”和“脉冲相位变换器2”变换成相位信号Q1和Q2。Q1与Q2的相位 差由“鉴相器”鉴得,如果Q1超前于Q2,相位差由P+的脉冲宽度表示;如果Q1滞后于Q2,相位 差由P-的脉冲宽度表示。环节TJQ的作用是测量P+或P-的脉冲宽度,并且在锁相环中充当调节 器,使得锁相环能够迅速锁定。在锁定的情况下,Q1和Q2的相位差或者为零,或者为恒定值,这 时必有fe=fd。由于TJQ输出的数据Dout与数控振荡器DCO的输出脉冲频率fd成正比,将Dout锁存 输出,即可跟踪光电脉冲编码器的输出脉冲的频率fe,从而跟踪原动机的转速。

1.3锁相测速环路的调节算法的研究

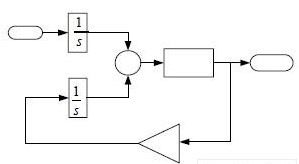

锁相测速环节的动态结构如图3。

“脉冲相位变换”表示为积分环节;“数字控制振荡器DCO”表示为比例环节,比例系数 是KF(采用2500线的光电脉冲编码器,其输出脉冲经过4倍频处理。原动机的最高转速为 3000r/min,光电编码器的输出频率fe的最大值是2500×4×50=500kHz,所以DCO的最大输出振 荡频率也是500kHz,测速输出的是14位并行数据,所以,DCO环节的系数KF=500/214)。在原动机 稳态运行时,光电脉冲编码器输出的脉冲信号的频率恒定,由于测速环路的被控对象中含有 一个积分环节,所以,在这种情况下,“调节器TJQ”中只需采用比例算法就可以实现对输入信 号频率的准确测量。但是,作为动模实验室原动机仿真,原动机的启动、制动、升速、降速是 频繁发生的,光电脉冲的频率在不断的变化。在这样的变化过程中,仍然要求锁相测速环节能 够快速跟踪和准确测量输入的光电脉冲信号的频率。“调节器”仅仅采用比例算法就不够了, 必须引入频率前馈,采用复合控制,才能对变化的输入光电脉冲信号的频率进行准确测量。

2.测速实验及结论

原动机仿真系统锁相测环路试验包括稳态和动态两个方面。

由表1的测量结果可以看出,在整个测量的频率范围内,具有很好的测速(测频) 精度和 线性度。表1中给出的最低的122.1Hz的输入频率是通过对标准的500kHz的频率进行4096 分 频而得到的,如果脉冲编码器的分辨率为10000P/r,其对应的电机转速为0173 r/ min。这完全 满足原动仿真系统跟踪的要求。

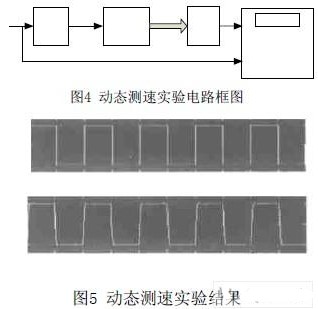

动态测速实验主要是测试“锁相测速装置”对于变化的输入频率信号的跟踪响应特性, 实验这样设计:被测的频率是由“压/频变换器”产生,用输入的电压信号Vi控制“压/频变换 器”的输出频率。锁相测速环节的输出经由D/A转换器再还原成输出电压信号VO ,用虚拟仪器 (存储示波器)观测VO 对于Vi的响应。动态测速实验电路框图如图4所示,实验结果如图5所示。

在图4所示的实验装置上,输入的Vi信号是频率为100Hz,幅值为2V的方波,V/F变换器的增益 是50kHz/V。也就是说,当输入的Vi信号是高电平时,V/F变换器输出100kHz的频率信号,经过 锁相测速装置,得出测速结果,再经过D/A转换器将测速结果还原成输出信号VO。从图5可以看 出,VO 能够较好地跟随Vi的变化,这说明“锁相测速环节”有较好的动态响应特性。

论文创新点:硬件由传动的机械齿轮测速改为红外光电测速,软件实现方法由原来的T 法改为锁相环跟踪测速方法。实现了原动机低速时的高精度快速测量。在本系统中改变了传统测速方法测量周期长的不足,将锁相环技术应用本系统,能 实时跟随原动机转子的转速,改善了系统的控制性能。

-

pll

+关注

关注

6文章

740浏览量

134572 -

频率

+关注

关注

4文章

1272浏览量

58484 -

发电机

+关注

关注

26文章

1485浏览量

66579

发布评论请先 登录

相关推荐

利用锁相环技术对原动机转子速度变化的进行测量

利用锁相环技术对原动机转子速度变化的进行测量

评论