声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1602文章

21309浏览量

593132 -

IO

+关注

关注

0文章

396浏览量

38508 -

Altera

+关注

关注

37文章

771浏览量

153306

发布评论请先 登录

相关推荐

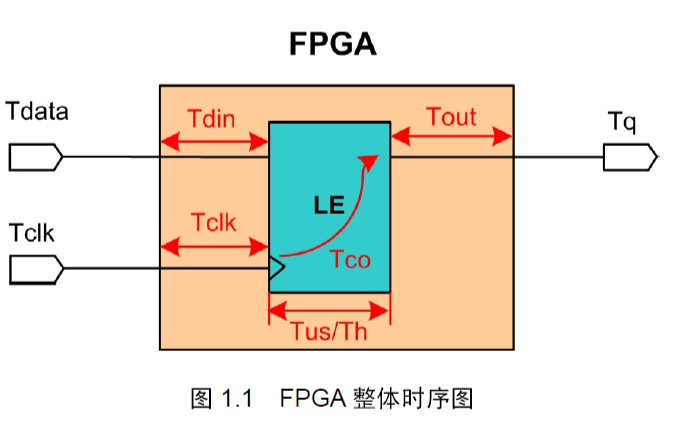

FPGA的IO约束如何使用

set_input_delay属于时序约束中的IO约束,我之前的时序约束教程中,有一篇关于set_input_delay的文章,但里面写的并不是很详细,今天我们就来详细分析一下,这

发表于 09-06 09:22

•1692次阅读

如何有效的管理FPGA设计中的时序问题

如何有效的管理FPGA设计中的时序问题当FPGA设计面临到高级接口的设计问题时,EMA的TimingDesigner可以简化这些设计问题,并

发表于 04-14 17:03

FPGA静态时序分析——IO口时序(Input Delay /output Delay)

FPGA静态时序分析——IO口时序(Input Delay /output Delay)1.1概述 在高速系统中

发表于 04-25 15:42

FPGA高级时序综合教程

FPGA高级时序综合教程The UCF FileUCF =用户约束文件( User Constraints File )可以用文本编辑器和XilinxConstraints Editor (GUI

发表于 08-11 11:28

FPGA的高级学习计划

换、流水线操作及数据同步等;第三阶段 时序理论基本模型;时序理论基本参数;如何解决时序中的问题:关键路径的处理;跨时钟域的处理:异步电路同步化;亚稳态的出现及解决方法;利用Quarut

发表于 09-13 20:07

大西瓜FPGA--FPGA设计高级篇--时序分析技巧

时序分析是FPGA设计的必备技能之一,特别是对于高速逻辑设计更需要时序分析,经过基础的FPGA是基于时序的逻辑器件,每一个时钟周期对于

发表于 02-26 09:42

如何有效的管理FPGA设计中的时序问题

如何有效的管理FPGA设计中的时序问题

当FPGA设计面临到高级接口的设计问题时,EMA的TimingDesigner可以简化这些设计问题,并提供对几乎所有接口的预先精确控制。从简单

发表于 04-15 14:19

•673次阅读

FPGA中IO口的时序分析详细说明

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束利序例外约束才能实现PCB板级的时序收敛。因此,

发表于 01-13 17:13

•11次下载

关于 FPGA 中的高级 IO 时序

关于 FPGA 中的高级 IO 时序

评论