声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

adi

+关注

关注

143文章

45773浏览量

240048 -

时钟

+关注

关注

10文章

1479浏览量

130304 -

仿真工具

+关注

关注

0文章

31浏览量

10690

发布评论请先 登录

相关推荐

电路板上clk是什么用的材料

电路板上的CLK是时钟信号线,用于同步各个电子器件的工作节奏。时钟信号告诉电子设备何时进行特定的操作,保证设备内部各功能模块的协调工作。本文将详细介绍电路板上CLK的用途、材料以及其工

芯片中的clk引脚是什么意思

Clk引脚在芯片中是时钟信号的输入引脚。时钟信号在数字电路中起着非常重要的作用,它用于同步芯片内各个模块的操作,确保它们按照正确的时间序列执行任务。 时钟信号的输入通常由外部晶振或振荡

【基于Lattice MXO2的小脚丫FPGA核心板】02ModelSim仿真

`timescale 1ns / 100ps#设定仿真的时间基准为1ns

module LED_shining_tb;#模块名称

parameter CLK_PERIOD = 10; #设定仿真使用到的

发表于 02-29 08:25

康谋产品 | 为ADAS/AD开创的次世代AutoGI仿真工具

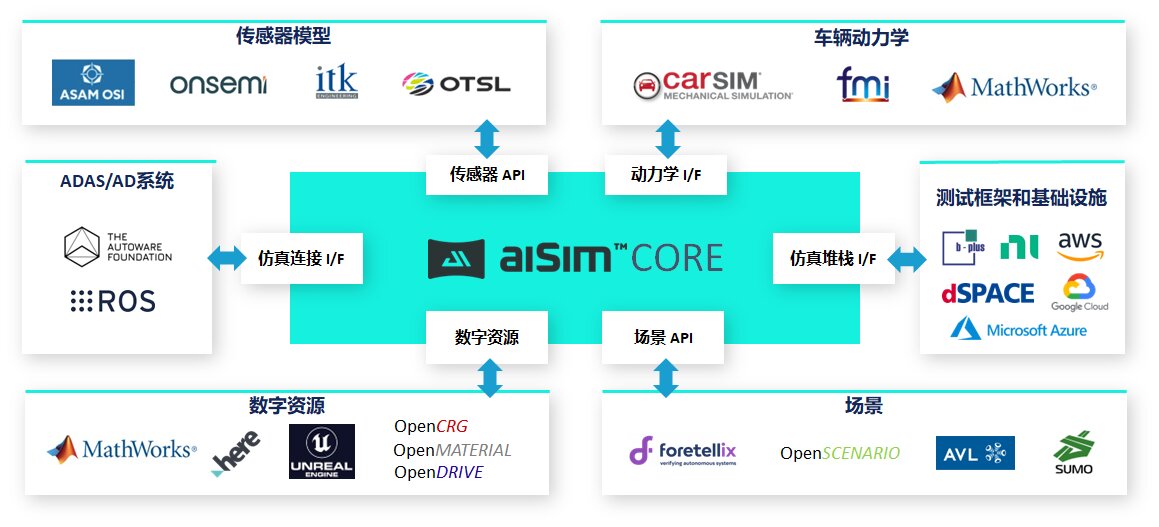

康谋aiSim5作为开创性ADAS/AD仿真模拟工具,配备高度优化的传感器模拟,提供确定且可重复的环境模拟支持,为下一代仿真工具设定了新的标准。

热仿真工具Ansys Discovery的使用案例

初期想法,并专注于设计流程的改善和验证。它消除了传统仿真工具在可用性和速度方面的阻碍,利用 Ansys 旗舰求解器来满足所有的高精确度和高保真需求,从而使每个工程师都能做出更正确的方案。

请问AD9122内部时钟HB1_CLK、HB2_CLK、HB3_CLK的频率是多少呢?

AD9122的内部时钟HB1_CLK、HB2_CLK、HB3_CLK的频率是多少呢?

发表于 12-21 06:51

AD9515的CLK与CLKB这两个引脚接差分时钟时哪个接CLK+,哪个接CLK-?

时钟芯片AD9515的CLK与CLKB这两个引脚接差分时钟时哪个接CLK+,哪个接CLK-,还是两个怎样接都无所谓?

我看到AD9233的

发表于 12-12 07:23

FPGA设计之Verilog中clk为什么要用posedge而不用negedge?

Verilog是一种硬件描述语言,用于描述数字电路的行为和特性。在Verilog中,时钟信号(clk)和线路是非常重要的,它用于同步电路中的各个模块,确保它们在同一时刻执行。

发表于 10-10 15:41

•1232次阅读

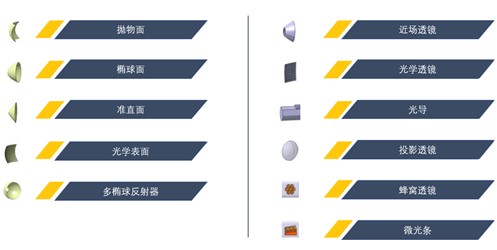

SPEOS—光学产品设计及仿真工具

、照明设备等领域。SPEOS软件内嵌ISO和CIE国际标准,可整合结构进行光机系统的设计,依据人眼视觉特征和材料真实光学属性进行场景仿真,能够在产品设计阶段对方案的可行性进行验证,在设计前期发现、反馈和处理问题,使光学设计以高效快捷

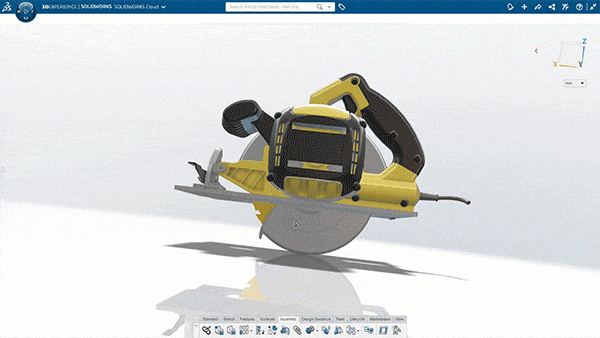

SOLIDWORKS仿真计算是什么意思?

SOLIDWORKS仿真计算是指利用SOLIDWORKS软件进行工程设计和分析时所使用的计算方法和技术。SOLIDWORKS是一款流行的三维计算机辅助设计(CAD)软件,它提供了丰富的工具和功能,使工程师能够创建和模拟各种

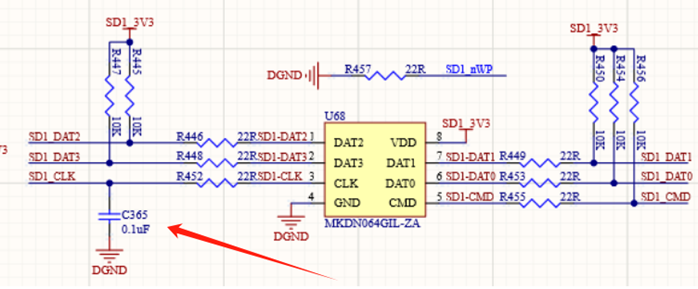

ADIsim CLK™_精确、快捷、易用的时钟产品辅助设计及仿真工具

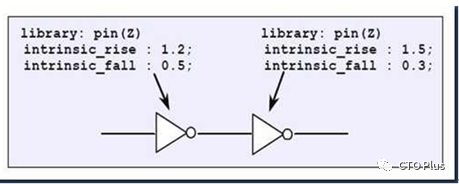

ADIsim CLK™_精确、快捷、易用的时钟产品辅助设计及仿真工具

评论