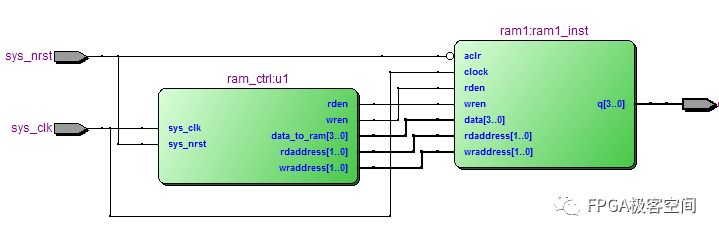

FPGA中RAM的使用探索。以4bitX4为例,数据位宽为4,深度为4。

第一种方式,直接调用4bitX4的RAM。编写控制逻辑对齐进行读写。

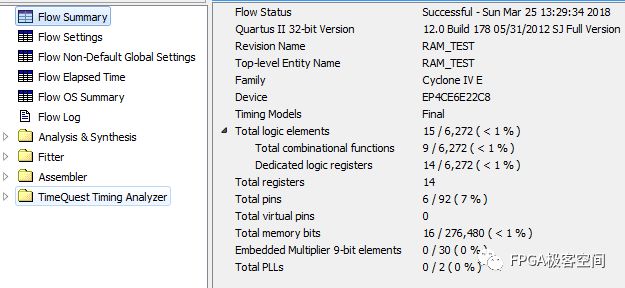

quartus ii 下的编译,资源消耗情况。

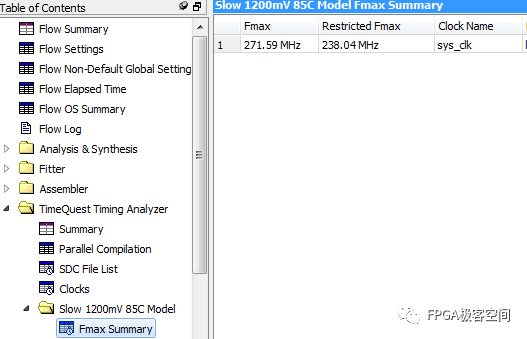

85C模型下的时钟频率。

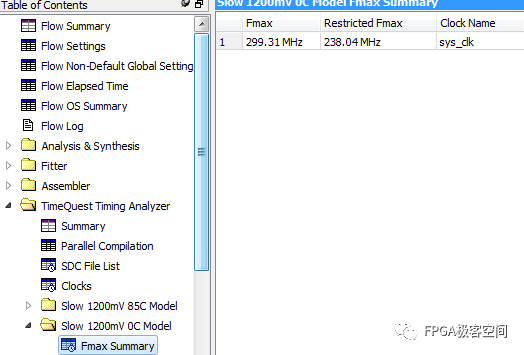

0C模型下的时钟频率。

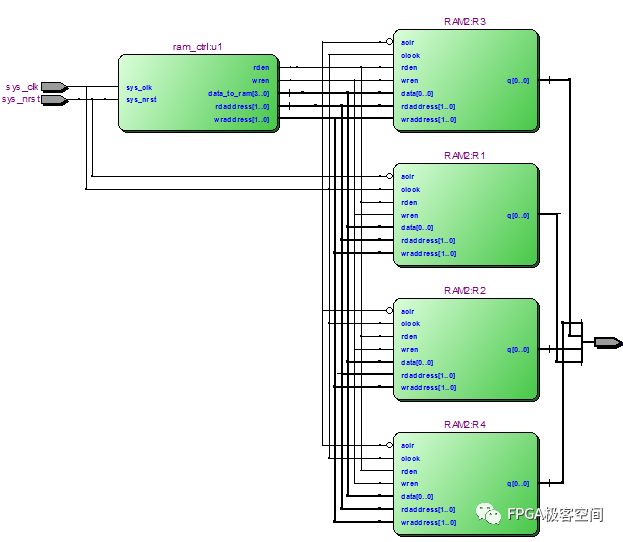

第二种方式,调用1bitX4的RAM,例化4次。编写控制逻辑对齐进行读写。

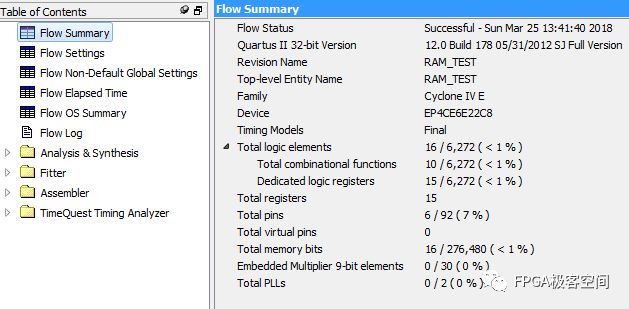

quartus ii 下的编译,资源消耗情况。

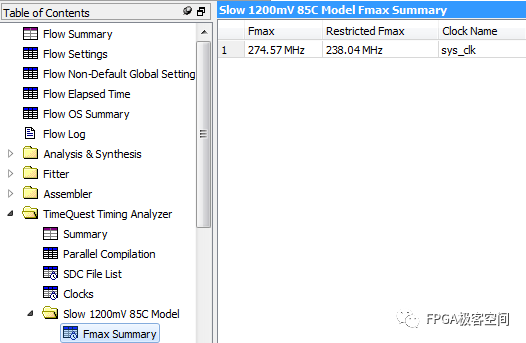

85C模型下的时钟频率。

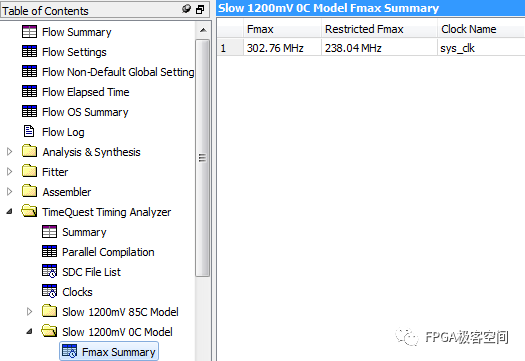

0C模型下的时钟频率。

从上述两种情况来看,两种RAM的使用方式,最终使用资源比较接近,方案二稍多,而从时序模型综合结果看,方案二的时钟频率明显比方案一高。在高速情况下,建议使用方案二。同样在位宽较宽情况下,可使用生成块语句进行例化,减少顶层对同一模块的例化数,是比较方便的。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1602文章

21317浏览量

593153 -

RAM

+关注

关注

7文章

1320浏览量

113704

原文标题:FPGA中RAM使用探索

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

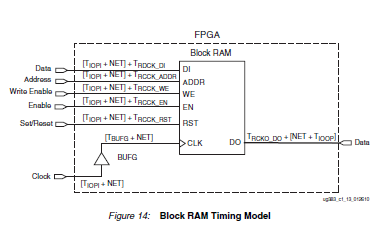

FPGA中块RAM的分布和特性

在选择FPGA时,关注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因为它们是FPGA架构中的两个核心资源,对于设计的性能和资源利用至关重要。

基于FPGA的双口RAM实现及应用

的应用。采用FPGA技术构造双口RAM,实现高速信号采集系统中的海量数据存储和时钟匹配。功能仿真验证该设计的正确性,该设计能减小电路设计的复杂性,增强设计的灵活性和资源的可配置性能,降

发表于 04-24 09:44

在FPGA中的RAM有与其他产品有什么不同?

实现了不同的逻辑功能。查找表(Look-Up-Table) 简称为LUT,LUT 本质上就是一个RAM。目前FPGA 中多使用4 输入的LUT,所以每一个LUT 可以看成一个有4 位地址线的 的

发表于 08-23 09:14

如何实现ASIC RAM替换为FPGA RAM?

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一个单独的奇偶校验写使能位,但在FPGA RAM

发表于 04-24 09:37

如何读出LUT中RAM的上电值?

你好,在我们的研究中,我们正在探索FPGA器件上SRAM的上电状态的固有随机性。因此,我们现在正试图在启动后从aVirtex-5器件读出分配的RAM值。但是,根据“Virtex-5

发表于 06-18 09:26

基于FPGA的双口RAM实现及应用

为了在高速采集时不丢失数据,在数据采集系统和CPU之间设置一个数据暂存区。介绍双口RAM的存储原理及其在数字系统中的应用。采用FPGA技术构造双口RAM,实现高速信号采集

发表于 02-11 11:20

•69次下载

基于Actel FPGA的双端口RAM设计

基于Actel FPGA 的双端口RAM 设计双端口RAM 芯片主要应用于高速率、高可靠性、对实时性要求高的场合,如实现DSP与PCI 总线芯片之间的数据交换接口电路等。但普通双端口RAM

发表于 11-15 17:44

•82次下载

Spartan-6 FPGA块RAM的技术参考资料免费下载

本指南是描述所有Spartan-6 FPGA中可用的Spartan®6 FPGA块RAM的技术参考。块RAM用于高效的数据存储或缓冲,用于高

发表于 02-15 16:38

•13次下载

使用FPGA调用RAM资源的详细说明

FPGA可以调用分布式RAM和块RAM两种RAM,当我们编写verilog代码的时候如果合理的编写就可以使我们想要的RAM被综合成BRAM(

发表于 12-30 16:27

•9次下载

如何使用FPGA内部的RAM以及程序对该RAM的数据读写操作

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该

FPGA在一个时钟周期可以读取多个RAM数据吗?

FPGA在一个时钟周期可以读取多个RAM数据吗?如何理解FPGA中存放程序的RAM? FPGA在一个时钟周期可以读取多个

fpga双口ram的使用

FPGA双口RAM的使用主要涉及配置和使用双端口RAM模块。双端口RAM的特点是有两组独立的端口,可以对同一存储块进行读写操作,从而实现并行访问。

技术控:FPGA中RAM使用技巧探索

技术控:FPGA中RAM使用技巧探索

评论