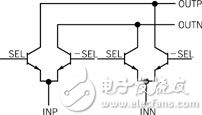

只要把两个 DAC 交错接入一个单元,你就可以有效地使一个 DAC 的采样速率增加一倍。轮流更新每个 DAC,并切换到合适的输出端,就可以使整个系统的有效吞吐率加倍。在复用这些 DAC 的输出时使用高质量的高速开关,这对系统总体性能是至关重要的。本设计实例中的电流型 DAC 考虑到输出开关的电流导引实施。电流导引使用的两个差分晶体管对,以四象限乘法器的形式交叉耦合(图 1)。在这种结构中,晶体管的饱和电压最小,电压摆幅很小,而开关速度很高。

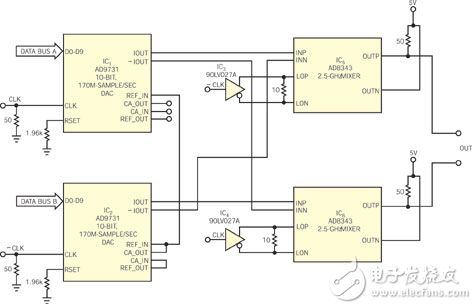

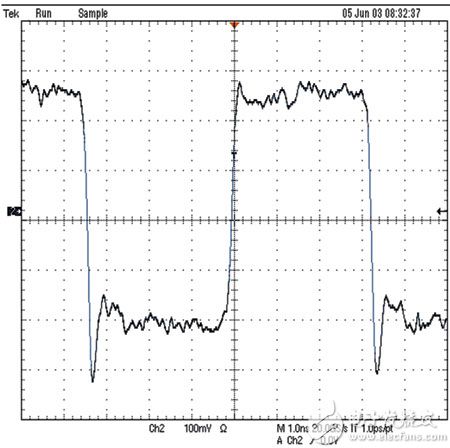

2.5GHz 的AD8343 型混频器包含一个可用高速电流型开关的完整四象限乘法器结构。AD8343 内部的偏置电路把发射极直流电压设定为大约 1.2V,而发射极直流电压又反过来设定 DAC 输出端必需的依从电压。只是在基极连线上有一个最小驱动信号时,发射极才以虚拟的交流接地出现。这些节点的电压摆幅减小,可将寄生电容的影响减小到最低程度。本设计实例使用两个 AD8343 混频器作为高速开关,以便复用来自两个 AD9731 型DAC 的差分输出电流(图 2)。在混频器的输出侧,终端电阻器为电源留出了直流路径,为电流—电压转换做好了准备,并表现为 50Ω 单端反向终端阻抗。这种配置允许该电路通过两根 50Ω 同轴电缆来驱动位于远处的 100Ω 差分负载。LO 输入端的低电平时钟信号来自终端阻抗为10Ω的高速 LVDS 缓冲器。大约 ±3.5mA 的 p-p 驱动器在 LO 输入端产生大约 70mV p-p 驱动电压。图 3 表明该电路提供的输出上升时间和下降时间快于 200 ps。

图2, “像打乒乓球一样”轮流更新两个 DAC 的输出,可以有效地使吞吐率加倍。

作者:Randall Carver ,Analog Devices,Geensboro,NC

-

开关

+关注

关注

20文章

3307浏览量

97479 -

dac

+关注

关注

44文章

2680浏览量

196372 -

混频器

+关注

关注

10文章

859浏览量

49407

发布评论请先 登录

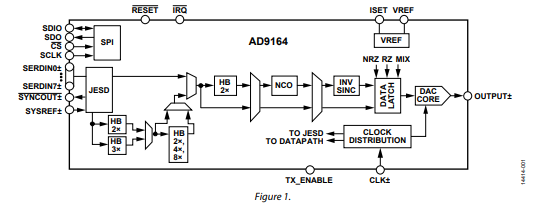

AD9164 16位、12 GSPS、RF DAC和直接数字频率合成器技术手册

两个DAC交错接入一个单元,可以有效地使一个DAC的采样速率增加一倍

两个DAC交错接入一个单元,可以有效地使一个DAC的采样速率增加一倍

评论