卡内基梅隆大学的Kevin K. Chang发表了一篇亮眼、出色的博士论文——《理解和改进基于DRAM的内存系统的延迟》(Understanding and Improving the Latency of DRAM-Based Memory Systems),解决了DRAM问题,并提出了一些新的架构改进办法,以在DRAM延迟方面做出实质性的改进。

三个问题

Kevin将DRAM延迟问题分成四个部分,笔者将在这里总结其中三个:

·低效的批量数据移动。

·DRAM刷新干扰。当DRAM正在刷新时,它不能全部被访问。

·单元格(Cell)潜伏期的变化——由于制造变异性。

至于第四个问题:延迟所带来的影响,有兴趣的朋友可以一起讨论。

1.低效的批量数据移动

在内存和存储代价高昂的时候,数据移动被限制在一个寄存器大小的块中,或者最多是来自磁盘的512字节块。但如今,在存储容量达千兆字节的存储空间和海量内存的情况下,海量数据移动变得越来越普遍。

但数据移动的架构——从内存到CPU,再到有限的内存总线——都没有改变。Chang的建议是一种新型的、高带宽的存储器子阵列之间的数据通路,利用几个隔离晶体管在同一存储器中的子阵列之间创建宽——8192位宽——并行总线。

2.DRAM刷新干扰

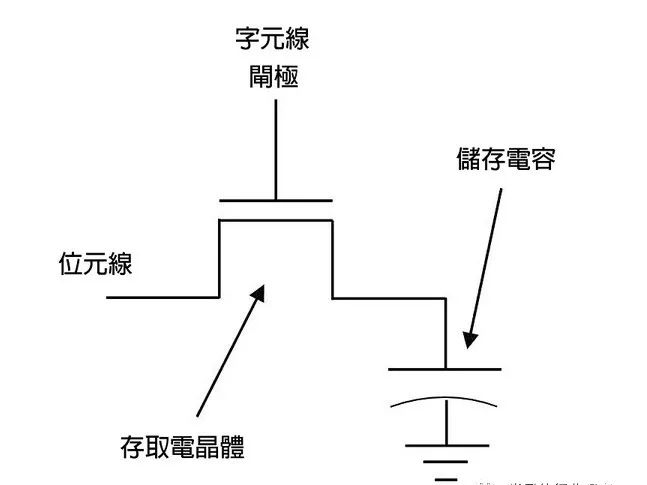

DRAM内存单元需要刷新以保存数据,这就是为什么它被称为动态RAM。DRAM刷新是成队列,而不是一次性刷新的,因为这样做需要太多的能耗。但是,当一个队列被刷新时,它不能被访问,这会造成延迟。

DRAM的延迟正在变高,因为随着芯片密度的增加,需要更新更多的队列,32Gb的芯片上可能降低将近20%的性能。

Chang提出了两种机制,即通过对bank和子阵列的内存访问进行并行刷新来隐藏刷新延迟。一个是使用无序的per-bank刷新,使内存控制器可以指定一个空闲的bank来刷新,而不是常规的严格循环顺序。第二种策略是写-刷新操作并行化,使刷新延迟和写延迟重叠。

在他的测试中,使用8核CPU,这些策略提高了超过27%的加权内存性能。

3.单元格延迟变化

得益于制造工艺的提升,记忆单元格可以有大量性能提升,随着密度的增加而增加。但是DRAM被指定以最慢的单元的速度可靠运行,这意味着如果使用最快的单元格,就会有显著的性能上升。

Chang在论文中提出了两种利用这种变化的机制,获得的速度提升从13%提高到了几乎20%。

探索与优化

在系统架构中,探索瓶颈和修复瓶颈的工作是没有终点的。过去20年内,DRAM一度被认为难有进步,但我们看到,其延迟水平也会被改变。

随着越来越多的晶体管、专业指令集和诸如此类的性能的提高,降低DRAM延迟也将成为性能改进的主要目标。

-

DRAM

+关注

关注

40文章

2177浏览量

182005 -

延迟

+关注

关注

1文章

69浏览量

13379

原文标题:20年难有进步,DRAM延迟问题得到优化

文章出处:【微信号:cunchujie,微信公众号:存储界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

[分享]直接总线式DRAM的信号连接

DRAM内存原理

【内存知识】DRAM芯片工作原理

NUC8i7BEH DRAM频率不稳定

FPGA DRAM数据错位

DRAM存储原理和特点

DRAM芯片中的记忆单元分析

钰创科技开发全新的DRAM架构

DRAM的架构/标准/特点/未来展望

Kevin K. Chang:解决了DRAM问题 提出新的架构改进DRAM延迟问题

Kevin K. Chang:解决了DRAM问题 提出新的架构改进DRAM延迟问题

评论