一、引言

为了提高传输速率和传输距离,计算机行业和通信行业越来越多的采用高速串行总线。在芯片之间、板卡之间、背板和业务板之间实现高速互联。这些高速串行总线的速率从以往USB2.0、LVDS以及FireWire1394的几百Mbps到今天的PCI-Express G1/G2、SATA G1/G2 、XAUI/2XAUI、XFI的几个Gbps乃至10Gbps。计算机以及通信行业的PCB客户对差分走线的阻抗控制要求越来越高。这使PCB生产商以及高速PCB设计人员所面临的前所未有的挑战。本文结合PCB行业公认的测试标准IPCTM-650手册,重点讨论真差分TDR测试方法的原理以及特点。

二、IPC-TM-650手册以及PCB特征阻抗测试背景

IPC-TM-650测试手册是一套非常全面的PCB行业测试规范,从PCB的机械特性、化学特性、物理特性、电气特性、环境特性等各方面给出了非常详尽的测试方法以及测试要求。其中PCB板电气特性要求在第2.5节中描述,而其中的2.5.5.7a,则全面的介绍了PCB特征阻抗测试方法和对相应的测试仪器要求,重点包括单端走线和差分走线的阻抗测试。

三、TDR的基本原理及IPC-TM-650对TDR设备的基本要求

3.1 TDR的基本原理

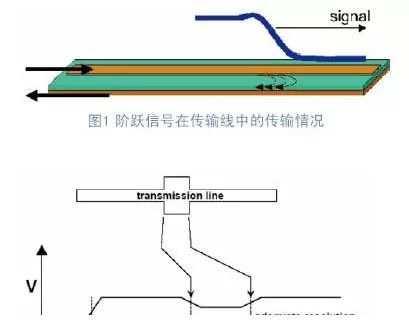

图1是一个阶跃信号在传输线(如PCB的走线)上传输时的示意图。而传输线是通过电介质与GND分隔的,就像无数个微小的电容的并联。电信号到达某个位置时,就会令该位置上的电压产生变化,就像是给电容充电。因此,传输线在此位置上是有对地的电流回路的,因此就有阻抗的存在。但是该阻抗只有阶跃信号自身才能“感觉到”,这就是我们所说的特征阻抗。

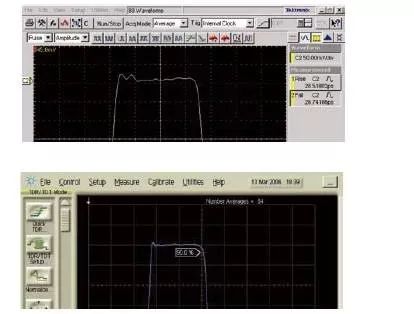

当传输线上出现阻抗不连续的现象时,在阻抗变化的地方阶跃信号就会产生反射的现象,如果将反射信号进行取样并显示在示波器的屏幕上,就会得出如图2所示的波形,从波形中我们可以看出一条被测试的传输线在不同位置上的阻抗变化。同时我们可以比较图2中的两个波形。这是使用两台分辨率不同的TDR设备在测试同一条传输线时获得的测试结果。对于传输线阻抗变化的反映一个明显而另一个不明显。TDR设备感知传输线阻抗不连续的分辨率取决于TDR设备所发出的阶跃信号上升时间的快慢,上升时间快所获得的分辨率就高。而TDR设备的上升时间往往和测试系统的带宽紧密相关,带宽高的测试系统有更快的上升时间。

从另外一个角度来考虑,TDR设备的系统带宽限制了TDR测试的分辨率。在IPC-TM-650测试手册中对TDR设备的上升时间是按照系统上升时间(tsys)来定义的。当我们要测量一台TDR设备的系统上升时间时,我们可以短路一台TDR设备的输出,此时可以测出该TDR设备的(tsys)(上升时间以及下降时间)。例如图3的TDR设备的系统上升时间就高达28ps左右。

图4是另一台TDR设备的系统上升/下降时间的测试结果,系统的上升/下降时间在38ps~40ps之间。可见不同的TDR设备在系统上升/下降时间上是有很大的区别的,由此带来的就是传输线阻抗测试分辨率的很大不同。

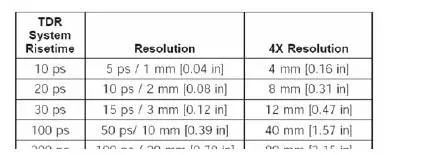

系统上升时间和分辨率的关系可以用下列的公式来描述:

Resolution= (tsys*V)/2,V为电信号在被测试传输线上的传输速率。

为了方便测试者了解TDR测试的分辨率以及PCB板走线的最小测试长度,在IPC-TM-650测试手册的表4-1(图5)中给出了速查数据。

3.2 IPC-TM-650手册对差分TDR设备的基本要求

IPC-TM-650测试手册是一套非常全面的PCB行业测试规范,从PCB的机械特性、化学特性、物理特性、电气特性、环境特性等各方面给出了非常详尽的测试方法以及测试要求。在以往的IPC-TM-650手册中,对PCB差分TDR测试的要求较为宽松。手册中允许测试者根据TDR测试设备的情况使用两种不同的方法。

方法一:当测试者拥有差分TDR测试设备时,测试设备同时打出两个幅度相等、方向相反的阶跃脉冲,并通过这对差分信号的相互作用直接测出差分走线的阻抗。

方法二:当测试者没有差分TDR测试设备时,测试设备在差分走线(A线与B线)时,先在A线上打出阶跃信号,测试A阶跃信号在A线上的反射特性记作AA,同时测出A阶跃信号在B线上的感应信号,记录为BA。随后,在B线上打出阶跃信号,测试B阶跃信号在B线上的反射特性记作BB,同时测出B阶跃信号在A线上的感应信号,记录为AB。通过对获得的AA、AB、BB、BA四个数值进行计算可以得出差分走线的阻抗。该方法又叫做“Super-Position”。

但是在(2004年3月版)IPC-TM-650手册中,仅仅保留了方法一中的真差分TDR测试描述。而不再有方法二的“伪差分”TDR测试方法的描述。

-

pcb

+关注

关注

4220文章

22472浏览量

385747

原文标题:PCB差分走线的阻抗控制技术(一)

文章出处:【微信号:mcugeek,微信公众号:MCU开发加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

自学PCB差分走线的阻抗控制技术(上篇)

自学PCB差分走线的阻抗控制技术(上篇)

评论