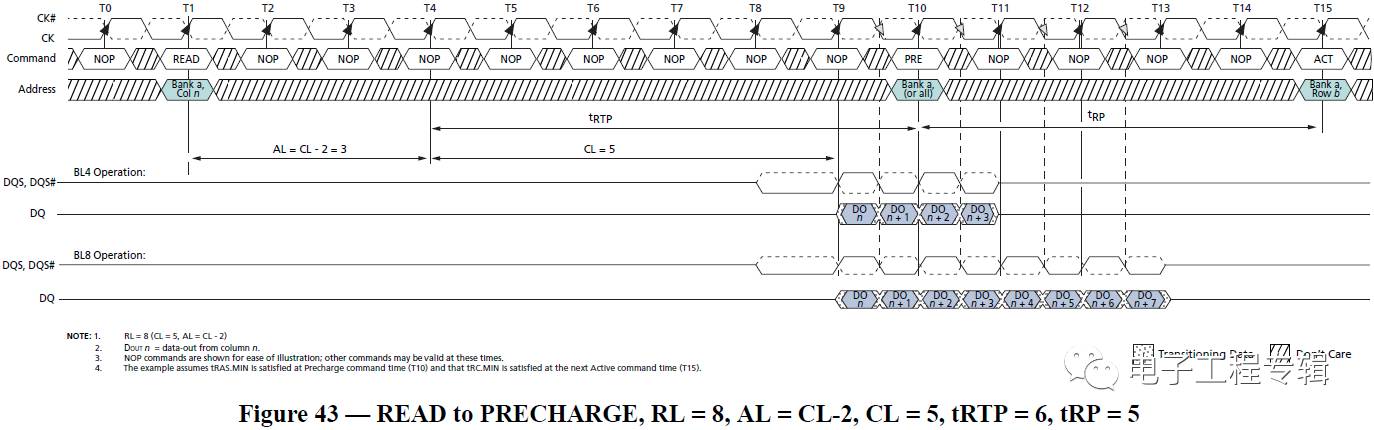

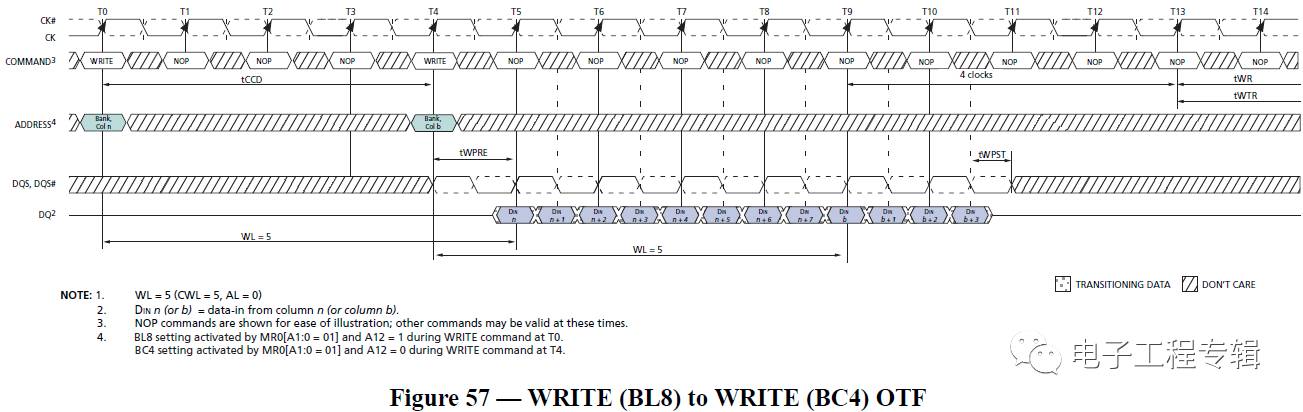

DDR3是目前DDR的主流产品,DDR3的读写分离作为DDR最基本也是最常用的部分,本文主要阐述DDR3读写分离的方法。最开始的DDR, 芯片采用的是TSOP封装,管脚露在芯片两侧的,测试起来相当方便;但是,DDRII和III就不一样了,它采用的是BGA封装,所有焊点是藏在芯片的底部的,测试起来非常不便,一般需要提前预留测试点。在DDR读写burst分析之前,首先得把read burst和write burst分离出来,读写双向的数据全部都搁在DQS和DQ上。那么,DDR的手册中,留下了那些线索供我们进行都写的分离呢?要实现DDR的快速的便捷的分离,在读写分离之前,我们必须得知道DDR读写信号之间的特征差异。首先,看看SPEC里面的定义:

方法一:preamble的差异在每次的burst之前,DQS会从高阻态切换到一段负脉冲,然后才开始正常的读写。这段负脉冲,我们叫做preamble(preamble实际上是在读写前,DQS提前通知DRAM芯片或者是controller的信号)。一般说来,读数据DQS的preamble宽度要大于写数据。对于DDR3,情况就更简单了。因为在DDR3中,读数据的preamble是负脉冲,写数据的preamble是正脉冲。

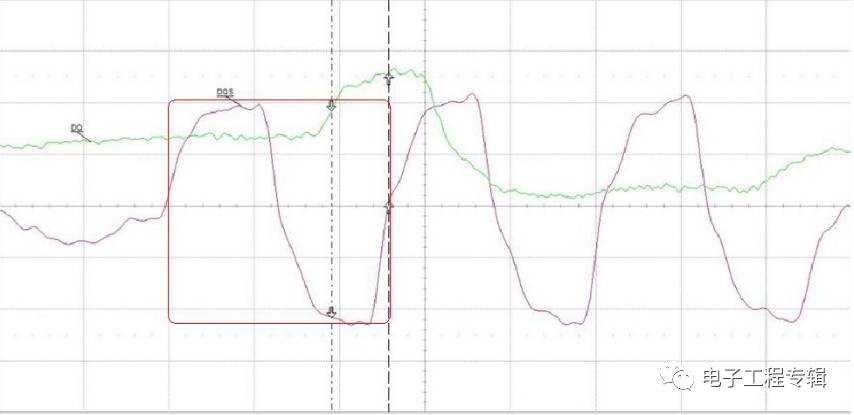

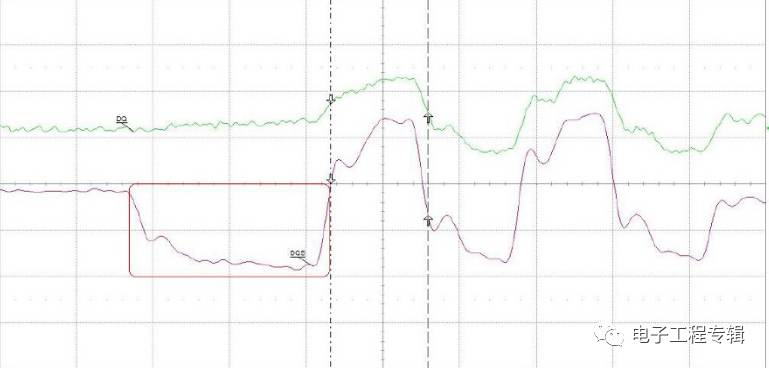

方法二:幅度上的差异一般在DRAM端进行测试,写数据从memory controller出来,经过了主板PCB板,内存插槽和内存条PCB板,到达DRAM颗粒的时候,信号已经被衰减了,而读数据刚刚从DRAM出来,还没有经过任何的衰减,因此读数据的幅度要大于写数据。如下图所示方法三:写数据是DQS和DQ centre-align(中间对齐), 读数据DQS和DQ是edge align(边沿对齐),memory controller在接收到内存的读数据时,在controller内部把DQS和DQ的相位错开90度,实现中间对齐来采样(这个过程示波器就看不到咯);方法四:斜率的差异:读数据的斜率大于写数据。一般在DRAM端进行测试,写数据从memory controller出来,经过了主板PCB板,内存插槽和内存条PCB板,到达DRAM颗粒的时候,信号已经被衰减了,所以,斜率也小一些;而读数据刚刚从DRAM出来,还没有经过任何的衰减,因此读数据的斜率要大于写数据。也可以从下图得到区分。

-

DDR3

+关注

关注

2文章

268浏览量

41782

原文标题:四种方法搞懂DDR3的读写分离

文章出处:【微信号:eet-china,微信公众号:电子工程专辑】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

cyclone V控制DDR3的读写,quartusII配置DDR3 ip核后,如何调用实现DDR3的读写呢,谢谢

基于Xilinx MIS IP的DDR3读写User Interface解析

DDR3的读写--Spartan-6 x16,感觉data mask有问题

基于FPGA的DDR3六通道读写防冲突设计

基于FPGA的DDR3 SDRAM控制器的设计与优化

基于FPGA的DDR3多端口读写存储管理的设计与实现

DDR3芯片读写控制及调试总结

基于FPGA的DDR3多端口读写存储管理的设计与实现

ddr3的读写分离方法有哪些?

ddr3的读写分离方法有哪些?

评论