背景

之前在一个ASCI开发项目中有小小接触过一些新思科技的一个NVMe控制器,代码量尚可,只是由于速度及其他原因的考虑,整个部分的设计其实有时候还是比较难以考量的,而且由于流片成本及IP购买成本的问题,当时就想像如果在一款FPGA中可以直接实现这样一款高性能的PCIe NVMe控制器或许会对整个性能的把握会更好一些,而下面的Fidus Sidewinder-100系统就是一个集成的PCIe NVMe 控制系统。

Fidus Sidewinder-100 PCIe NVMe Storage Controller:Fidus系统是基于Sidewinder-100 PCIe NVMe存储控制器设计实现的,而这个控制器在一个Xilinx Zynq UltraScale+ MPSoC ZU19EG 上实现,之所以选择这款芯片来实现有很多考量,不过最重要的是因为PCIe Gen3/4 能力:高速,且板卡的两个100Gbps QSFP 光纤网络槽可以实现防弹并行转换;另外还可以利用Xilinx可编程器件内部巨大的I/O灵活性来实现DDR SDRAM控制器,并驱动两个SFF-8643 Mini SAS连接器(用于片外SSDs等);并且,芯片上集成了六个ARM处理器核,可以提供强大的处理能力(四个64bitARM Cortex-A53 MPcore 处理器和两个32bit的ARM Cortex-R5 Mpcore处理器);Xilinx UltraScale架构还提供大量的片上可编程逻辑单元。正是由于Zynq UltraScale+ MPSoc系列用于这么多的features,才使得实现一个高性能NVMe 控制器成为可能并变得容易,正像Sidewinder-100系统一样,用户可以基于此板卡实现大量的各种类型的任何可以想到的硬件设计。

Sidewinder-100系统通过SCSI和SAS存储阵列获得了具有较强市场竞争力的性能优势,同时它还通过Fabrics技术实现了NVMe, 从而大大减少了存储传输时的延迟。从下图的板卡上可以看出,板卡上还集成了两个M.2连接器,可以用于连接NVMe SSD卡。此外,可以通过Zynq UltraScale+ MPSoC的PS(处理系统)和PL(可编程逻辑)部分分别连接到两个到DDR4 SO-DIMM端。这种分开连接实现了两种不同速率的DDR4 SO-DIMM,连接到PS上的DDR4 SO-DIMM操作速率为1866M每秒,而连接在PL部分的DDR4 SO-DIMM传输速率可以达到每秒2133M。

当然,正是利用了Sidewinder-100的这些优点才实现了一个强大的PCIe Gen4开发平台,如下图所示:

图1:Fidus Sidewinder-100 PCIe NVMe Storage Controller

不过,由于Fidus其实是一个设计house,在最开始,也考虑到Sidewinder-100 PCIe NVMe存储控制器的应用,它还是可以用于实现一些通用目标设计的。当然了,最重要的是此板卡为实现任何高性能PCIe Gen3或Gen4开发设计提供了强大的平台,此外,在利用此平台进行开发时遇到任何问题,都可以通过Fidus获得一些帮助。(特别提示:Siderwinder-100 PCIe NVMe存储控制器的PCIe电源和回路适配器是在板卡的背面):

图2:Fidus PCIe Power and Loopback Adapter

另外,考虑到Gen4母板还是比较缺乏的,所以当你没有一个母板的时候,刚好可以通过这个连接口插一个PCIe卡到板卡上。而且这个适配器看起来它应该是比一个能量紧缺的母板的功耗要小很多,而且只需要将这个适配器看作一个简单的DC电源连接器来操作就好。

总结随着Xilinx FPGA技术的不断增强,之前一些设计难题或者功耗难题已经在慢慢的解决,而随着这些困难的消除,FPGA的设计领域也越来越广泛,相信在未来,Xilinx 的FPGA会给我们带来更多惊喜。

-

FPGA

+关注

关注

1602文章

21320浏览量

593158 -

fidus

+关注

关注

0文章

1浏览量

1448

原文标题:Sidewinder-100 PCIe NVMe Controller的秘密武器

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

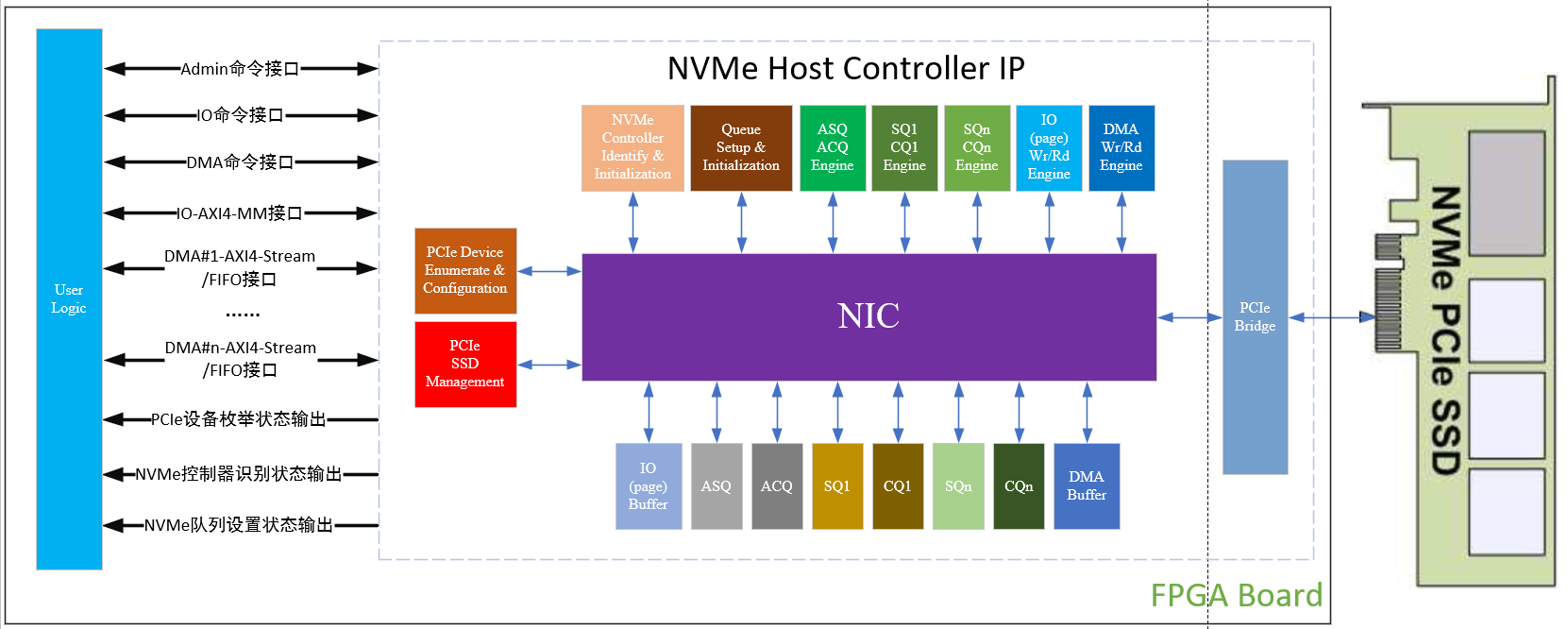

高性能NVMe主机控制器,Xilinx FPGA PCIe 3

高性能NVMe主机控制器,Xilinx FPGA NVMe Host Accelerator IP

Xilinx FPGA高性能NVMe SSD主机控制器,NVMe Host Controller IP

Xilinx FPGA NVMe主机控制器IP,高性能版本介绍应用

Xilinx FPGA NVMe Host Controller IP,NVMe主机控制器

Xilinx FPGA NVMe控制器,NVMe Host Controller IP

配网故障定位如何有效应对电力故障

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有效应对FPGA硬件设计

Fidus Sidewinder-100集成PCIe NVMe 控制系统,有效应对FPGA硬件设计

评论