在设计模拟采集电路时,ADC芯片的SPI通信总线的时序可能存在偶发异常,但如果异常出现概率很低,我们该如何对这种异常进行定位呢?我们刚刚定位了客户端波形异常的原因,本文正是实战案例分享。

有工程师反馈:在产品测试过程中偶尔会出现通信故障,经过系统性的分析,ZLG致远电子团队推测可能是ADC芯片的SPI通信总线时序偶发异常引起,但由于异常概率很低,我们该如何对SPI通信总线偶发的时序问题进行定位呢?

一、搭建测试环境

SPI总线测试点位于主机的主板底部,时钟频率大约为33MHz,属高频信号,所以对探头的端接方式比较讲究;为了方便测试,如图1所示,用短线将测试点引出,探头的地线也从前端自绕线引出,这样可以提高信号完整性,减少示波器采样对时序分析过程的影响。

图1 探头端接测试点

二、长时间监测定位异常

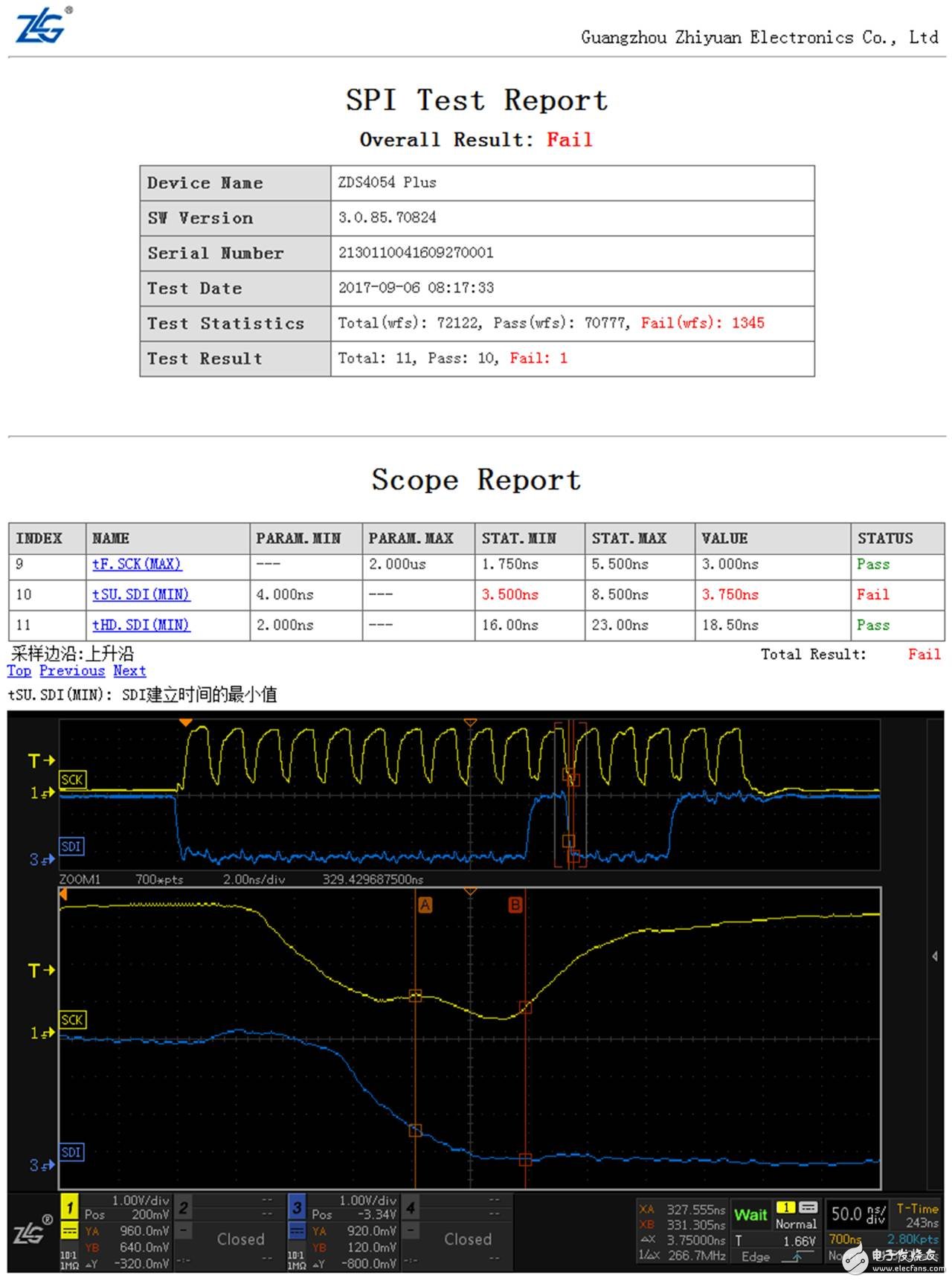

ZDS4000的时序分析软件具备长时间统计功能,下班后设置好示波器,对数据采集仪的SPI总线时序连续监测一个晚上,第二天上班的时候,导出监测分析结果,如图2所示,一个晚上总共进行了72185次测量,其中有1347次是测量失败的,导致异常的原因是SPI的数据建立时间不满足后级芯片的时序要求。示波器自动保存了这1347份失败的测试报告,打开第1345份测试报告,如图3所示,显示了当前建立时间为3.75ns(包含时序违规处截图),不满足后级芯片4ns建立时间的要求,而且历史出现最差的时序是3.5ns,最好时序是8.5ns,问题得以定位。

图2 时序分析统计结果

图3 测量结果失败报表

三、定位问题并做稳定性验证

通过上述测试分析,SPI总线的建立时间偏小,保持时间偏大,调整时钟信号时序延迟6.5ns左右,就可得到较好时序分析,即将数据信号建立时间和数据信号保持时间尽可能接近。整改之后再次用时序分析软件对SPI总线进行一夜的稳定性测量,测量结果如图4所示,进行了72842次时序分析,所有测试都通过,且每一项测量项都PASS。之前的问题项建立时间,最小值10.75ns,最大值13.5ns,非常完美,这显示了 SPI总线的时序非常稳定性。

图4 时序分析测量结果

总结

时序的一致性和稳定性分析,一直以来都是业界难题。当前ZLG致远电子的时序一致性测试方案已经免费支持I2C、SPI、I2S和MIPI-RFFE,如果您有其它时序分析的需求,也可以在后台联系我们,我们将第一时间反馈给研发团队。

-

ADC芯片

+关注

关注

3文章

68浏览量

20070 -

偶发异常

+关注

关注

0文章

2浏览量

2044

原文标题:自动监测数十小时——时序一致性测试解决方案

文章出处:【微信号:ZLG_zhiyuan,微信公众号:ZLG致远电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AI技术如何融入测量分析进行偶发异常定位

AD7193如何通过spi的时序图来进行模拟spi的通信编程?

SPI总线小结

_SPI_总线协议及时序介绍

SPI总线协议的通信原理及应用举例

利用SPI通信总线对从机进行IAP升级

SPI总线协议及时序图详解

用SPI总线实现DSP和MCU之间的高速通信

SPI总线协议和SPI时序图的详细资料讲解

详解SPI总线协议与时序图

FreeRTOS SPI 时序以及模拟SPI时序

SD卡系列之spi模式---spi通信

SPI总线协议及SPI时序图详解

如何对ADC芯片的SPI通信总线的时序可能存在的偶发异常进行定位?

如何对ADC芯片的SPI通信总线的时序可能存在的偶发异常进行定位?

评论