在信号完整性杂志上面看到这篇文章,作者:Zachariah Peterson 发表时间:2020年9月1日,个人觉得本篇文章内容对从事PCB设计、EMC设计、信号完整性设计都具有一定的参考价值,经翻译后适当配图分享给大家。

如果您的职业生涯大部分时间都在从事 PCB 设计,并且您在计算机接口的布局和布线方面有经验,那么您就知道一件事是正确的:在器件应用说明中会有一些推荐的设计建议,并不是这些建议总是错误的,而是这些建议很容易断章取义。

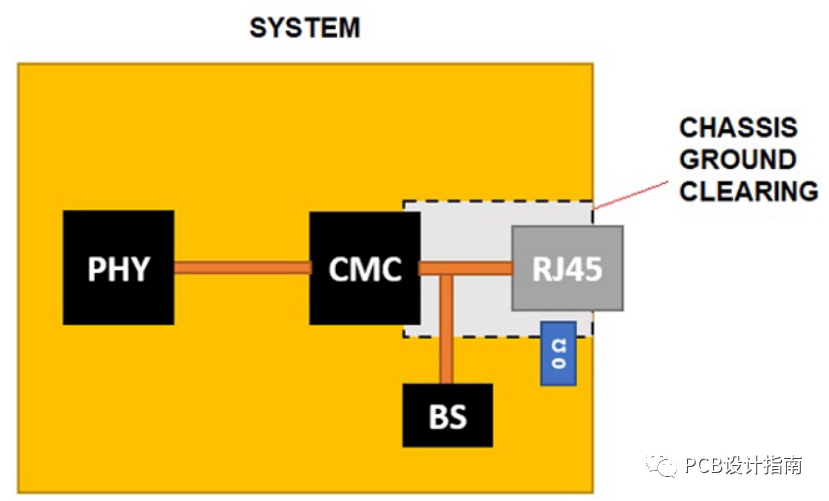

一位同事向我提出的一项建议是,在离散磁铁和连接器之间布线时,在RJ45连接器下方使用接地层。一些应用说明建议将系统接地覆盖RJ45连接器下方,一些应用说明建议将接地平面拆分为系统和机箱部分,以提供更强的隔离。应用说明中的一些建议指出,PHY、磁体和/或RJ45插孔下方应完全省略接地层。

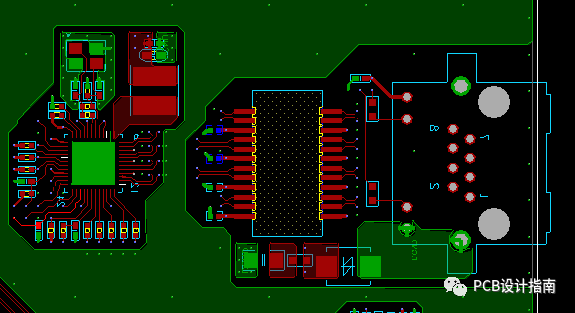

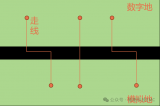

图2:以太网连接器处地平面挖空处理

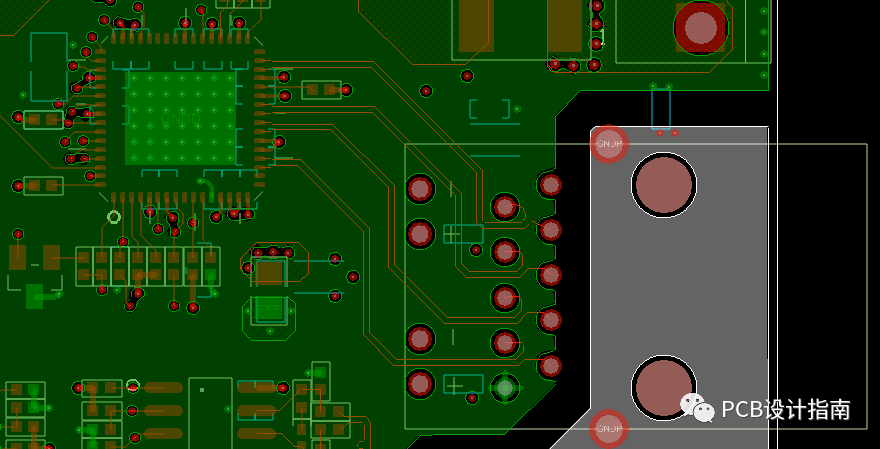

图2:以太网连接器处地平面挖空处理 图3:以太网连接器处保护地和数字地分割处理

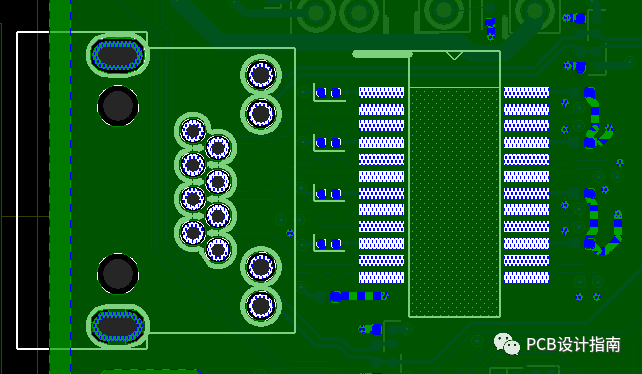

图3:以太网连接器处保护地和数字地分割处理 图4:以太网连接器处数字地处理

图4:以太网连接器处数字地处理那么哪一个是正确的呢?与我一起工作的设计师以及我们最近开发的电路板始终包括一个系统平面,其机箱切口一直延伸到RJ45的边缘,即使多个连接器并联放置。当我在论坛上浏览不同的建议时,其他专业设计师声称他们从来没有遇到过移除共模扼流圈输出端和RJ45之间的所有地平面区域的问题。让我们更深入地研究一下,看看我们是否能够理解这些差异产生的原因,以及何时适合在RJ45连接器下使用连续平面、拆分平面或无平面。

以太网布局和地平面的功能

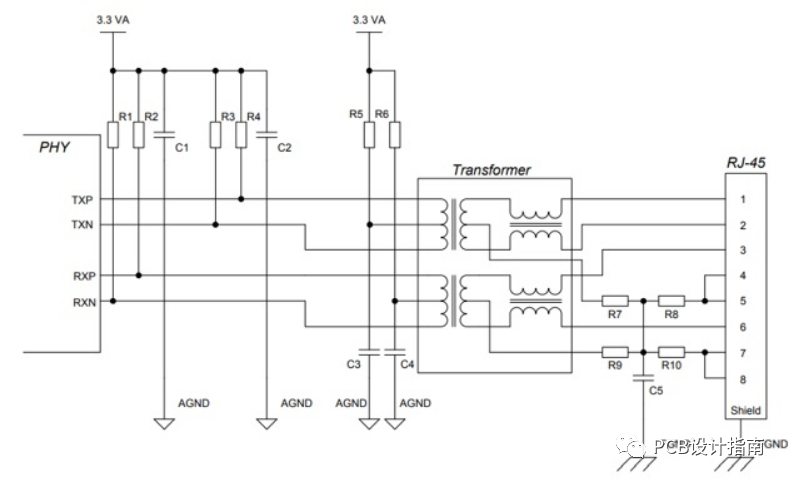

为了进一步了解以太网系统和连接器不同部分下面的接地层的概念,让我们简要介绍一下以太网和RJ45连接器的布线要求。以太网系统由MAC/PHY接口(通常集成到单个IC中)、用于共模噪声抑制和端接的磁性电路、用于端接的其他无源器件(通常为上拉或戴维南端接)和RJ45连接器组成。Rx和Tx线路在整个系统中并行布线。无源器件的数量、值和排列取决于确切的布线标准(例如,Base-T与以太网供电)和PHY接口。

MAC/PHY、磁性电路和RJ45连接器之间的记录道作为具有定义阻抗的差分对布线。注意,这包括离散磁电路内的布线。差分阻抗设置为100欧姆,以提供与电缆差分阻抗的匹配。通常首选较短的布线,尤其是在较高频率(如千兆以太网和更高)下,以减少损耗。每个使用以太网的人都非常清楚这些要求。围绕接地层(一个或多个接地层)的争议始于放置离散磁铁和与PHY和RJ45连接器相关的终端所需的任何其它器件。通常有三种可能性:

选项1:将系统接地至RJ45连接器,无论连接器中是否集成了磁性元件;

选项2:使用分割接地平面,其中机箱接地位于RJ45下方,系统接地延伸至共模扼流圈的输入边缘;

选项3:在磁性输入和RJ45接头之间不放置接地层。

这个问题的答案取决于以下几点:在共模扼流圈附近,接地层中的随机位移电流(噪声)如何表现,磁铁是否集成到连接器中,以及磁铁和RJ45之间是否需要机箱接地以确保EMI保护和隔离。在我们了解这些选项中的哪一个客观上最适合在PHY、磁性和RJ45连接器之间进行路由之前,有助于回顾总体设计目标:

设计目标1:ESD/过压保护。802.3标准规定以太网PHY必须与系统的其余部分隔离,以便在50至60 Hz的频率下承受高达1500 V(RMS)的高压交流60秒;

设计目标2:噪音隔离。应防止电缆上拾取的任何噪声耦合回PHY和板的其余部分;

设计目标3:共模噪声分流器。任何接地区域中的共模噪声都应通过低阻抗路径从磁性和PHY侧转移。

所有这些设计目标都可以通过选项1-3以不同的方式实现。多个接地层的布置/耦合,或单个连续接地层的使用,将决定通过传播噪声电流看到的隔离、ESD保护和阻抗水平。为了更好地理解选项1-3,让我们看看如何为带有分立和集成磁性的RJ45连接器安排接地。

集成与离散磁体

下图(图 5)显示了 100 Mbps 以太网的示例原理图,在 PHY 附近采用典型的上拉电阻方案,用于端接,并在变压器中心抽头处为共模噪声分流连接 [1]。此示意图旨在显示分立磁体的接地区域的放置,但它也适用于具有集成磁体的 RJ45 连接器。 PHY 的输出和磁输入之间的距离应至少为 25 mm。此处的目的是在磁体和 PHY 之间提供足够的隔离,尽管使这些线路过长会导致更大的衰减,并且这种衰减在较高频率时更大。在这两种类型的连接器中,共模电容器也可以放置在末端抽头上,作为磁输入处系统接地的分流器,以提供更高的高频噪声抑制。

图5:工业级以太网原理图(最高 100 Mbps)

图5:工业级以太网原理图(最高 100 Mbps)上图显示了一个屏蔽的 RJ45 连接器,其中屏蔽层与 Bob Smith 终端电阻旁边的机箱接地连接。如果我们使用非屏蔽 RJ45,则连接器护罩没有机箱接地连接。请注意,STP 电缆需要与屏蔽 RJ45 连接器一起使用,但 UTP 电缆可以与屏蔽或非屏蔽 RJ45 连接器一起使用。在非屏蔽电缆上使用屏蔽连接器在抑制电缆中接收到的 EMI 方面没有任何好处,但在实际的以太网系统中也不会造成问题。

千兆以太网和更快的以太网将使用类似的方案,在磁性元件中有四个差分对和共模扼流圈。Bob Smith 终端几乎总是用于磁性变压器输出侧的中心抽头。一些人认为 Bob Smith 端接方案不是最佳选择,使用不同的端接方案可以实现更低的回波损耗。

对于带有集成磁性元件的 RJ45 连接器,系统接地层应延伸到连接器的边缘,以便为连接器的差分线路提供连续阻抗。系统平面也应该运行到离散磁体;在这两种类型的连接器中,如果连接器被屏蔽,则连接器屏蔽层连接到机箱接地以进行 ESD 保护并提供对高频噪声的屏蔽。这在设备可能存在于高压源或无线电设备附近的工业环境中很有用。我看到的许多应用手册都指出,磁性元件下方的区域不应填充接地层。这就留下了以太网路由中最后一个未解决的问题和争论的根源:我们是否在磁输出和 RJ45 之间扩展了一个接地区域(系统和/或机箱)?

机箱和系统接地布局

选项 1

可视化选项 1 相当简单:只需在整个第二层运行系统接地层。系统接地将在磁性元件下方延伸并延伸至 RJ45 连接器。屏蔽连接器将紧靠机箱和外壳,因此其内部屏蔽将参考回系统接地。

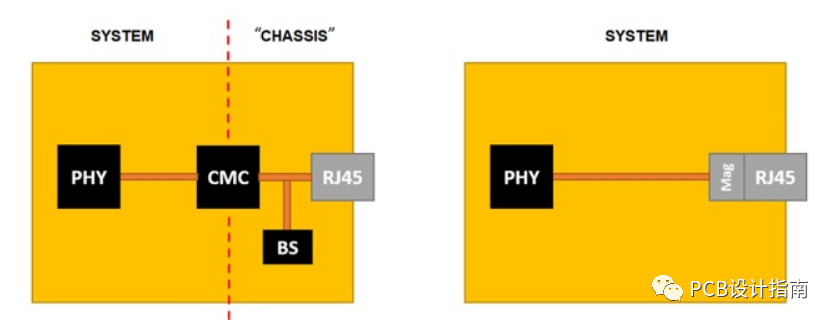

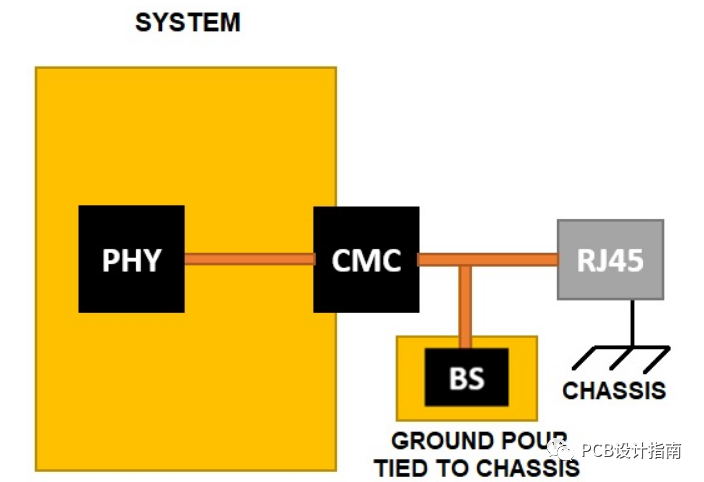

图 6:(左)框图显示了共模扼流圈 (CMC) 和其他组件下方的连续接地层。在这里,我们有机箱和系统区域,而不是一组平面。(右)框图显示了用于集成磁性的 RJ45 连接器的单个系统接地层。如图5所示,集成磁体上的中心抽头连接回底盘接地。请注意,Bob Smith 电阻器是集成磁体的一部分。

图 6:(左)框图显示了共模扼流圈 (CMC) 和其他组件下方的连续接地层。在这里,我们有机箱和系统区域,而不是一组平面。(右)框图显示了用于集成磁性的 RJ45 连接器的单个系统接地层。如图5所示,集成磁体上的中心抽头连接回底盘接地。请注意,Bob Smith 电阻器是集成磁体的一部分。对选项 1 的反对意见是,系统接地层连接器区域中的噪声电流可以通过耦合到磁性元件中将共模噪声耦合回 PHY 侧(设计目标 2 和 3)。这里的另一个反对意见与设计目标 1 相关:以太网 PHY 应该在 802.3 标准下与系统的其余部分电隔离,并且接地层为 ESD 脉冲到达 PHY 和其他组件提供了低阻抗路径. 提供返回机箱的低阻抗返回路径,最终电源返回点仍可提供 ESD 保护和噪声吸收器。

理想情况下,您希望噪声电流沿着定向路径返回地面,而不是通过隔离栅耦合。从接地平面耦合回磁性元件并进入系统平面的 PHY 侧的共模噪声将以容性或感性方式进行。理想情况下,磁性元件应具有低漏电感和低漏电容/返回接地层的寄生电容。对于速度较低的以太网,漏电感将主导噪声传输,因为载波频率较低。相比之下,电容寄生将在更高的以太网速度下占主导地位,因为载波频率更高。

为满足选项 1 的所有三个设计目标,这需要将组合系统平面以非常低的阻抗连接到机箱。在我看来,这种方法最适用于集成屏蔽 RJ45 连接器,因为 ESD 脉冲或噪声可以立即分流回机箱。但是,不需要直接连接到屏蔽 RJ45;只要机箱有低阻抗连接,人们就会期望非屏蔽 RJ45 连接器能够正常工作。

请注意,如果没有正确规划返回路径,则连续接地层可能会导致数字和模拟部分之间出现干扰形式的 EMI 问题。此外,将平面上的多个点连接回机箱可以使电流形成通过机箱的环路,当系统平面和机箱之间存在很强的接地反弹电位时,会产生潜在的大型辐射器 。

选项 2

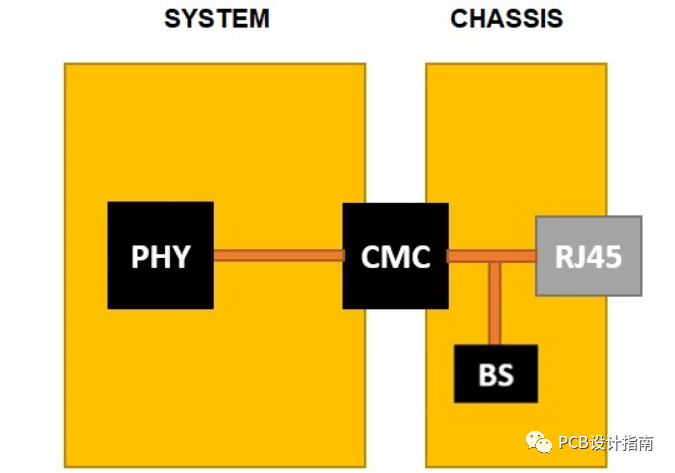

接下来,让我们看看选项 2。指定运行接地到 RJ45 连接器的应用手册指出,PCB 中应使用机箱接地区域。这在上面的示意图(图 5)中显示在磁性元件的输出侧,其中电阻器部分(R7-R9 = 75 欧姆)也通过 Bob Smith 终端连接回机箱接地部分。但是,选项 2 下的布局建议指定在物理上分离机箱和系统平面。对于分立磁性元件,无源元件需要放置在 PCB 上的某个位置并连接回地,因此在表面层下方必须有一个接地区域,或者至少在表面层上有一些接地,以提供与机箱的连接地面。如图 7 所示。

图 7:显示 CMC 和其他磁性元件周围的机箱和系统接地平面布置的框图(上面列表中的选项 2)。在 [1] 中可以找到对此的变体。

图 7:显示 CMC 和其他磁性元件周围的机箱和系统接地平面布置的框图(上面列表中的选项 2)。在 [1] 中可以找到对此的变体。在这里,您有两个独立的接地部分:系统接地和 PCB 中连接到机箱接地的平面区域。您如何确保它们保持相同的潜力?机箱接地区域应连接到其他接地,以消除这些区域之间的电位差。这可以通过低阻抗路径完成;将系统平面机械固定到机箱或在机箱和系统接地区域之间使用 0 欧姆电阻器这样简单的操作就足够了。放置高压电容器是桥接两个平面同时将高频噪声从磁体中引导出来的另一种策略。这样做的问题是,如果设计不当,您可能会在两个部分之间产生较大的环路电感返回路径。

图 7 的一个变体是简单地使用一个连续接地层,并为共模扼流圈切出一个大孔。不要这样做:您已经创建了一个大的导体环,它可以接收 EMI 并在系统的关键区域(即共模扼流圈之后)引发共模噪声。您基本上已将总共模抑制比 (CMRR) 减半。

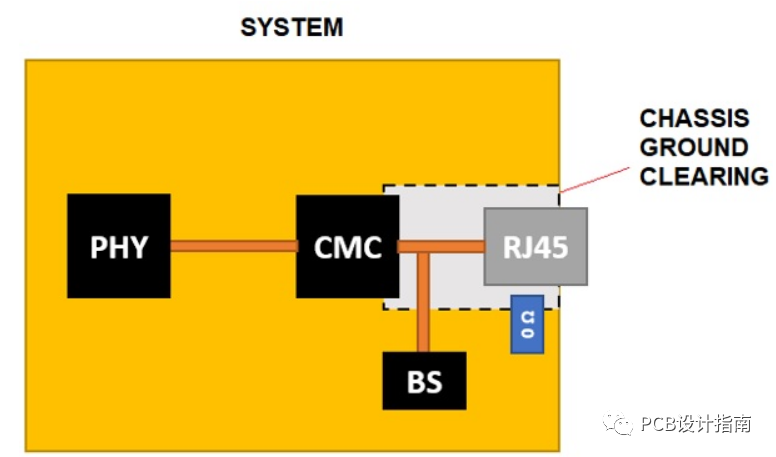

图 8显示了选项 2 的另一个变体。这包括在系统接地层中放置一个接地切口,该接地层一直延伸到电路板边缘,然后在 RJ45 连接器下方放置一个机箱层。Bob Smith 终端网络然后被放置在一边并连接回系统平面。可以使用 0 欧姆电阻或内部过孔将两个平面部分设置为相同的直流电势。然后可以将 RJ45 连接器护罩直接参考回机箱接地层。

图 8:在表层下方带有平面切口的以太网接地

图 8:在表层下方带有平面切口的以太网接地然后将机箱通过低阻抗路径连接回系统接地。应用说明指出应使用 0 欧姆电阻,而其他人建议使用电容器。从 ESD 的角度来看,最好的连接方式是将它们以机械方式连接回机箱。同样,如果没有仔细规划返回路径,我们在磁性元件附近存在接地电流并在 PHY 附近感应噪声的可能性相同。

选项 3

最后,让我们看看选项 3。对于集成磁性元件,系统接地将延伸到连接器的边缘(参见图 6,右面板),因此选项 3 仅适用于具有离散磁性元件的布局。在这种情况下,分立磁输入和连接器输入之间没有接地层;您有阻抗受控但没有接地层屏蔽的差分对。

图 9:带有离散磁性元件的选项 3 的以太网接地。此处显示了屏蔽连接器,尽管这可以通过移除 RJ45 上的机箱接地连接来应用于非屏蔽连接器。

图 9:带有离散磁性元件的选项 3 的以太网接地。此处显示了屏蔽连接器,尽管这可以通过移除 RJ45 上的机箱接地连接来应用于非屏蔽连接器。您仍然需要在整个系统中提供统一的参考电位。典型的建议是使用高压电容器桥接这两个区域,如选项 2 中所示。您唯一的其他选择是在机箱和系统接地之间使用长路径直接连接,类似于图 7所述.我在移除磁性元件和 RJ45 连接器之间的接地层时遇到的一个问题是差分对之间的差分串扰的可能性。这对于千兆以太网(它使用四个差分对)和速度更快来说更令人担忧,并且它会在附近的信号线中产生噪声,特别是在具有多个以太网连接器的电路板中。

此外,这部分电路下方没有任何接地可能会产生与图 7 相同的返回路径问题;存在为噪声创建大环路电感返回路径的风险。尽管我对选项 3 有意见,但它的使用是有目的的,而且它可以按设计工作并通过 EMC 测试。对于屏蔽 RJ45,与其将 ESD 电流转入电路板上的机箱接地层,不如将 ESD 电流直接转入机箱本身。机箱和系统接地层之间的大物理隔离可以提供更高的隔离度,目标是超过 802.3 标准中的 1500 V 要求。如果布局正确,只要有低阻抗路径返回电源回路,接地区域连接器侧的噪声电流就可以从磁性元件和 PHY 转移出去。在接收高频噪声和 ESD 方面,在选项 3 中使用屏蔽导体是更好的选择,因为它可以通过低阻抗连接直接集成到机箱中。

其他不良接地建议

您将看到的另一个常见系统接地建议是将接地平面物理拆分为 PHY 输出处的数字和模拟区域。确保这两个平面之间接地电位一致的典型方法是将模拟平面和数字平面与旁路电容器连接起来。我经常在其他情况下看到这个建议,我觉得这个建议没有必要。在分离的数字和模拟平面之间使用旁路电容器旨在提供不同部分之间的返回路径,但这可能会产生额外的 EMI 问题。特别是,提供通过旁路电容器的返回路径会为模拟模块中的电路产生较大的环路电感,这会增加对外部 EMI 和内部串扰的敏感性。如果您正确规划了返回路径,则无需使用分离平面或旁路电容器。

最后的想法

总而言之,RJ45 连接器布局的重点围绕着正确接地、低环路电感、足够的 EMI 屏蔽、ESD 隔离和电路板中的返回路径规划。从环路电感和 EMI 屏蔽的角度来看,选项 1 和 2 是最好的,尽管它们需要仔细的布局规划。从 ESD 角度来看,选项 3 可以说是最好的,只要接地布置设计正确,尽管存在在系统中为共模噪声创建大环路电感路径的危险。如果在上述任何选项中使用屏蔽 RJ45,重要的一点是确保连接器屏蔽与机箱的连接阻抗非常低,然后需要一个低阻抗路径到系统接地。还要确保机箱和输出变压器中心抽头之间的路径具有足够低的阻抗,以稳定直流偏移并将机箱、RJ45 连接器屏蔽层和系统接地之间的任何电压差降至最低。对于非屏蔽 RJ45,这是一个有争议的问题;只需关注机箱和系统之间的低阻抗连接,即可提供 ESD 保护、噪声隔离和远离磁性元件和 PHY 的低阻抗路径。

如果布局得当,即如果存在足够低的阻抗路径以将噪声和 ESD 从磁性元件/PHY 转移开,则选项 1 可以很好地工作。

众所周知,只要没有接收 EMI 的大环路电感路径,选项 3 就可以很好地用于隔离和 EMC。这可能需要差分对之间的间距更小,以降低噪声敏感性,同时保持 100 欧姆差分阻抗。

选项 2 是选项 1 和 3 的混合体,具体取决于去除了多少地面;您必须通过低阻抗路径来平衡接地层间隙与接地连接。

与我合作的设计人员选择使用图 8 中的分割方法连接到 RJ45 连接器的接地层(分立磁性元件的选项 2),或者仅将系统接地连接到 RJ45(无论磁性元件放置如何)。两者都可以设计为确保机箱和系统接地之间的低环路电感路径,并在共模扼流圈之后提供与该区域中其他电路块的一些隔离。混合信号系统中的隔离可以通过表面层上的接地填充来增加,然后将其连接回系统接地。在布局和布线期间需要仔细规划返回路径,以使其正常工作,但如果您已正确完成所有操作,则在共模扼流圈之后可以从其他电路块接收到更少的共模噪声。

来源:微信公众号《PCB设计指南》

-

以太网

+关注

关注

40文章

5079浏览量

166251 -

emc

+关注

关注

165文章

3646浏览量

181184

发布评论请先 登录

相关推荐

以太网接口与地平面设计3种方案

以太网接口与地平面设计3种方案

评论