当然是可以的!您可以采用具有出色输入特性的运算放大器,并进一步提高其性能,使其电压范围、增益精度、压摆率和失真性能均优于原来的运算放大器。

ADI工程师曾设计过一个精密电压表的输入,需要一个亚皮安输入单位增益放大器/缓冲器,其低频噪声小于1μV p-p,失调电压低至大约100μV,非线性误差 小于1 ppm。它还需要在音频和60 Hz频率下具有非常低的交流失真,以便利用不断增强的ADC分辨率。这足够雄心勃勃,但它同时需要使用±50V电源缓冲±40 V信号。缓冲器输入连接到高阻 抗分压器,或直接连接到外部信号。因此,它还必须能够承受静电放电和过压输入的冲击。

可用的亚皮安偏置电流运算放大器并不多。可堪使用的器件常常被称为静电计级放大器,偏置电流低至数十飞安。遗憾的是,这些静电计放大器的低频电压噪声(0.1Hz到10Hz)为几微伏(峰峰值)。此外,其输入失调电压和失调温度系数一般也不符合要求。其共模抑制比(CMRR)和开环增益不够好,难以支持1 ppm线性度。最后,没有一款静电计能够承受高电源电压。

LTC6240 系列提供0.25 pA偏置电流(典型值)和0.55μV p-p低频噪声。这对于输入缓冲器来说已经足够好了,但该器件仅支持最高12 V的电源。ADI工程师将不得不在放大器周围添加电路以使其适应更高的电压。

设计方法

LTC6240由Vp(通过增益为+1的缓冲放大器保持输出加5 V的值)和Vm(由另一个缓冲器驱动而保持输出减5 V的值)供电。

由于电源总是跟随输入信号(由LTC6240的输出缓冲),因此理想情况下根本没有共模输入误差。即使是平庸的CMRR也通过自举提升至少30 dB。该30 dB值是由Vp和Vm缓冲器的有限增益精度导致的。

LTC6240的开环增益也得到类似的提升。当内部增益节点和电源轨之间存在晶体管输出阻抗时,放大器电路会发生增益受限的情况。由于电源被自举到输出,所以很少有信号电流流过上述阻抗,而且开环增益的增加量与CMRR的提升量相似。但是,输出负载仍可能会限制开环增益。

也许不那么明显,但电路整体压摆率也被自举提高。通常,它受限于LTC6240内部静态电流和以电源为基准的补偿电容。当电源追随输入和输出时,很少有动态电流流入这些电容,放大器不会进入有限压摆率状态。缓冲放大器最终会限制整体压摆率。

高压电源Vhvp和Vhvm可能有干扰,但缓冲器输出会在很大程度上抑制干扰,LTC6240的电源抑制比(PSRR)将大大增强。

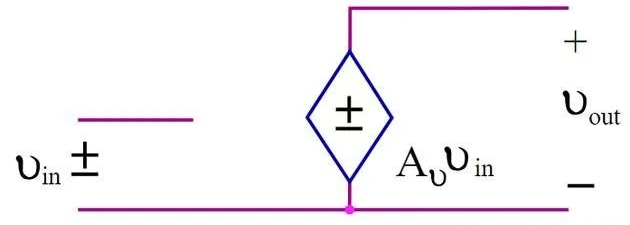

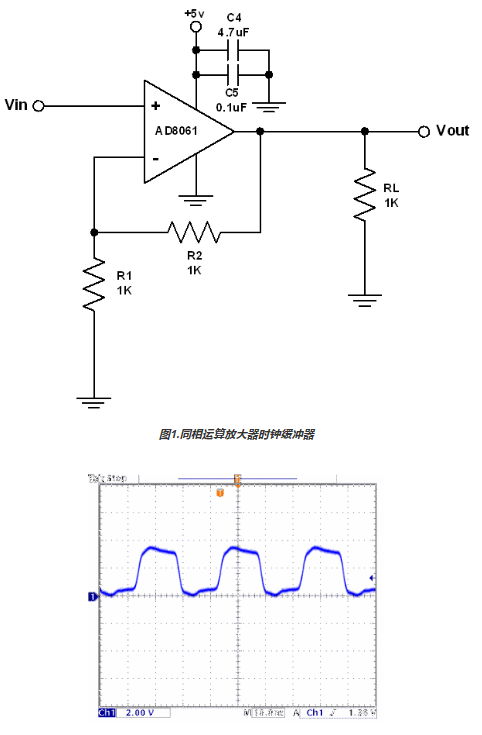

所以,这很棒;通过自举电源,缓冲器在多个方面得到改善。可能会出现什么问题?图1所示电路几乎肯定会振荡。考虑电源引脚行为的最佳方法是将其视为反馈环路的一部分:输出引脚电压乘以缓冲放大器频率响应,然后将乘以1/PSRR,加到输入端,最后乘以开环增益成为输出,如此循环往复。图2a显示了PSRR随频率的变化。

在PSRR曲线中没有获得相位数据,但假设它具有+90°相位。是的,这个+90°就像一个差异化因素。如图2b所示,从低频到100 kHz,开环增益具有-90°相位,之后该负值变得越来越大。缓冲器将具有有限频率响应,并且也将表现出相位滞后。将环路中的所有相位滞后相加可确保在一些频率下的反馈相位为0°或360°的倍数。如果在这些相位的电源环路增益大于1,振荡就会发生。PSRR幅度下降到4 dB的低点(衰减 = -4 dB→ 增益 = 0.63,非dB),看起来环路可能永远不会有足够的增益来发生振荡。这很可能是错误的,因为PSRR同时适用于Vp和Vs,其PSRR增益相加会使幅度超过1。此外,缓冲器可能会有一定的峰化,之后其增益在高频发生滚降,从而将整体反馈幅度推高至1以上。缓冲器必须驱动稍大的电容,并且会具有更多的相位滞后。无论如何,LTspice中的电路仿真表明会发生大信号振荡(LTC6240的频率响应和非线性体现在宏模型中)。

实际实现

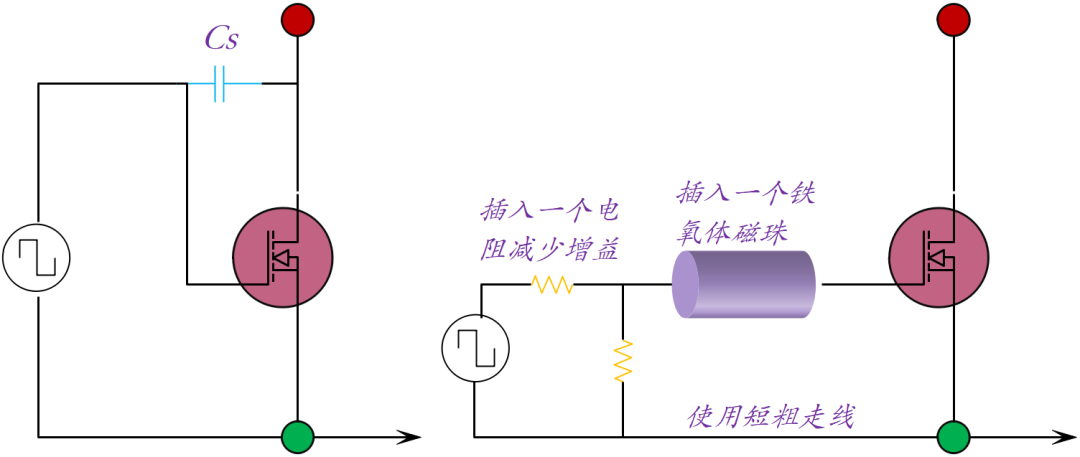

请注意,1000 pF旁路电容必须与LTC6240电源引脚紧密连接。运算放大器有数十个内部晶体管,在该放大器中,晶体管的Ft量级为GHz。它们常常以反馈方式彼此连接,除非安装了旁路电容,否则它们可能在高交流阻抗电源下发生振荡。1000 pF足以消除这些振荡。如果希望电源旁路电容远大于任何输出负载电容,因为在高频时,负载电容上的电压转换会导致电流流向电源轨,并可能调制电源电压,通过PSRR反馈引起振荡。因此,旁路电容会降低频率下的电源调制,相当于降低从输出到电源的反馈增益。

压摆这些旁路电容会需要很大的电流,而且必须是双向的。Q5和Q6是射极跟随器,可以驱动旁路电容的压摆电流。Q3和Q4是偏置二极管,用于设置Q5和Q6静态电流。Q2为这些二极管和齐纳二极管D1(实际上是并联基准电压源IC)提供偏置电流,D1设置相对于输出的正电源电压。Q2的集电极是一个电流镜的输出,该电流镜由高压轨之间的R9偏置。如果电源电压不是恒定值,可以用两个电流源代替R9。

Q7至Q12形成与之前所述相当的Vm减电源驱动器。请注意齐纳电压的不匹配是有意为之的:Vp比输入/输出高5V,Vm比输入/输出低3V。这种不匹配使输入电压的中点位于LTC6240的电源限制输入范围以内,从而优化压摆波形。

通常,LTC6240的电源电流会消耗Q5的发射极电流,并基本上关闭Q6,所以Vp缓冲器输出阻抗大部分是R3。因此,电源反馈Vp路径的带宽约为1/ (2π × 100 Ω × 0.001 µF) = 1.6 MHz。这保证了在10 MHz及以上的频率(此时LTC6240的开环相位向振荡发展),Vp环路增益远小于1。100Ω电阻还让跟随器Q5不必直接驱动1000 pF 电容。发射极跟随器会有输出电感,可能与容性负载发生谐振,引起振铃甚至振荡。

设计自举在1.6 MHz以上的频率会失败后,整体电路的完美行为在频率超出大约100 kHz时会降级。如果输出不能完全跟随输入,自举的好处将会打折扣。带Cin的Rin将带宽限制在100 kHz,这是ADC跟随缓冲器的系统抗混叠滤波器的一部分,它还会衰减无线电干扰和不支持的压摆率。

该电路必须能够承受任何不受限制的压摆输入信号或ESD,因此Rin也用于限制输入故障电流。电阻有四个串联段,以便分担输入过驱,暂时承受1 kV的电压。根据信号源和预期过载,可以减小输入电阻。

LTC6240内部有保护二极管,可将输入过压电流引导至Vp或Vm。允许进入LTC6240输入的最大故障电流为10 mA,但如果有周围电路可以快速切断输入故障,则在短时间内可以增加该电流。该电路的预期应用中存在SPDT继电器,当未通电时,其将缓冲器的输入连接到÷10网络。通电后,继电器直接连接输入。因此,当未通电时,缓冲器连接到远大于10 kΩ的源阻抗,故障电压和电流降低的幅度与10 mA连续额定值相当。应用的输入范围为±400 V,故障容差为±1000 V。这只有在有两个比较器的情况下才能安全地实现,比较器检测输入过压并快速释放继电器。这可以在1 ms至2 ms内完成,允许100 mA瞬态输入电流,此电流不会熔化LTC6240的保护二极管。

请注意,D3至D6用于将输入过载电流引导至Vhvp或Vhvm电源,该电流此前已通过LTC6240导向Vp或Vm。这些电源可能无法吸收过载电流,因为相对于正常供电操作,该电流是向后流动的。需将依靠足够大的旁路电容来安全地保持电源电压,同时等待继电器开关减压。对于100 mA过载,将需要100μF电容来使电源在2 ms内的电压变化保持在2 V以内。

高压信号源

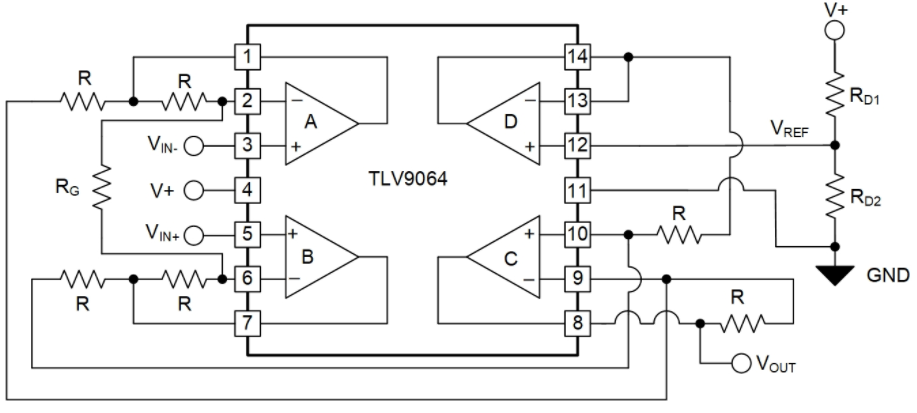

当测试实验室原型时,ADI工程师意识到没有信号发生器来提供任何波形的足够输出电压摆幅以激励电路。有可以产生最多±10 V p-p的各种波形的信号发生器。现在需要设计一个可以清晰地再现大幅度波形的放大器。图4显示了一个电流反馈放大器(CFA)的高压分立实现方案。

CFA(电流反馈型放大器)具有极高的压摆率,带宽通常也很宽(单位增益时)。不过因为使用的是高压晶体管,所以带宽适中。与较低电压类型相比,高压晶体管具有更高的寄生电容和更低的 Fts。

这里有一些事项需要注意。电路本身没有限流或限制功耗的功能,因此超过10mA的持续大负载电流会烧毁输出级,甚至可能烧毁更多电路级。此外,最好不要在高压电源上添加0.1μF以上的旁路电容。如果使用大电容,短路会引起焊接效应。有鉴于此,ADI工程师不得不在高压电源上增加100μF旁路电容以抑制二次谐波失真。ADI工程师用手上下摇动实验室电源,以避免硬开启和关闭。请注意,50V 电压就会产生足够的电流流过人体导致心脏停搏。最好将高压电源的电流限值降至60 mA。50 V足够高,需要警惕。

在图4中,ADA4898 运算放大器控制CFA,使其精度和失真受到控制。CFA一般具有高直流误差,高精度建立时间较长。运算放大器解决了这些问题。

CFA的正输入为节点n25,负输入为n5(是的,这是输入)。Rff和Rgg本身将内部CFA的增益设置为约27。这种高增益可以将运算放大器输出摆幅控制在±2 V。CFA可以设置为更高增益以进一步减轻控制放大器的负担,但如此一来,CFA将损失带宽,并且失真增加。总增益由Rf和Rg设置为20。Ctweak和Ctweak2配合Rf工作,从215 kHz以上的运算放大器整体反馈中消除CFA的相位滞后,从而增强运算放大器的稳定性。

Tn13是CFA增益节点,由涉及Q1/Q2/Q20和Q11/Q12/Q19的电流镜驱动。

Q7/Q8/Q10/Q13形成输出缓冲器,作为复合互补射极跟随器。没有限流电路——请勿将输出短接到任何东西!

高压放大器的CFA部分具有35 MHz的-3 dB带宽,并且不会自行峰化。整体电路的-3 dB带宽为33 MHz,但有8dB的峰化。通常,复合放大器设计的第二放大器的带宽至少是输入控制放大器带宽的3倍以避免峰化,但无法获得如此有利的比率。至少 8 dB峰值没有高Q值,并且振铃会相当快地消失。在峰化频率以下,目标100 kHz信号再现得很好。在100 kHz且输出为80 V p-p时,失真测量值为-82dBc;在100 kHz以下且输出为32 V p-p时,失真降至-100 dBc。对于快速边沿,方波响应具有约60%的过冲;当输出压摆率小于250 V/μs时,过冲很小或几乎没有过冲。最大压摆率约为1900 V/μs。

测量设置

面对大信号,如何使用普通实验室设备来测量±40 V输出?高压放大器和高压缓冲器的输出都不应超过10 mA,而且它们也不能稳定地驱动40 pF负载。同轴电缆的电容率为27 pF/英尺,电容量太大。示波器÷10探针只有大约15 pF||10MΩ负载,因此耦合到示波器会没问题。

对于失真测量,实验室的所有音频分析仪都不能在100 kHz时达到-80 dBc,所以必须求助于频谱分析仪。遗憾的是,频谱分析仪只有50Ω输入,这对驱动电路来说太低。解决方案是将阻抗提高到50Ω(见图5);也就是说,在信号和50Ω分析仪输入之间放置一个5 kΩ分压电阻,做成一个接近÷100的分压器。重要的是,5 kΩ电阻在低频信号下不会出现热偏移, 因为这些偏移与 VOUT2相关,会造成偶次谐波。ADI工程师选择将5个1kΩ、2 W电阻串联起来制作Rdivider。2 W电阻具有约37°C/W的热阻,5个1 kΩ电阻具有7.5°C/W的热阻。在其上施加±40 V正弦波时,功耗为160 mW,电阻加热将导致电阻的温度升高7.5×0.16 = 1.2°C。电阻偏移大约为100 ppm /°C,因此在直流时会有120 ppm的偏移,或大约0.01%的非线性误差及-80 dBc的失真。对于测量,这种精度怎么可能足够?好消息是分压器电阻的热时间常数相当大,ADI工程师预计在100 kHz周期的中部实际电阻偏移很小。讽刺的是,在较低频率(可能1 kHz及以下)时失真更差。

由于分析仪输入范围有限,80 V p-p信号无论如何都必须衰减,但它仍然太大,无法获得最佳频谱分析仪性能。在无辅助的情况下,分析仪只能提供-80 dBc失真,这是权衡利弊的结果,否则要么其噪声会淹没谐波,要么大输入会造成额外的失真。解决办法是在分析仪输入端放置一个100 kHz的陷阱来消除基波幅度。当信号少于几毫伏(仅谐波)时,可以实现接近-120 dBc的测量范围。图5显示了测试设置。

发生器通过一个低通滤波器(Linput和Cinput)驱动Rterm,滤波器衰减发生器的100 kHz谐波。失真由此改善到-113 dBc,低于要测量的电路。净化后的信号由高压放大器提升,并由缓冲器传递,缓冲器驱动分压器。

电感由缠绕在大型线轴(用于功率E-I磁芯)上的磁线构成。由于会增加失真,任何类型的磁芯材料都不能使用;必须使用气绕。只需反复缠绕和测量。

Ltrap以磁场方式将谐波辐射到相邻的松散无屏蔽线路(这是常用的方法),因此将陷阱元件放在一个带有接地BNC插孔连接的饼干罐中。实验室中有饼干罐,任何屏蔽钢质箱都可以。

为了校准,ADI工程师将两个放大器替换为直通线,并记录下二次到四次谐波频率时从Rterm电压到频谱分析仪输入的增益。在失真测试中测量谐波时,ADI工程师使用所存储的该频率对应增益来推断缓冲器输出端的谐波成分。ADI工程师用一个示波器监测缓冲器基频输出的幅度,计算归一化谐波的有效值,然后除以基波幅度,得到整体失真。

结果

使用图5所示设置,频谱分析仪在70 V p-p和80 V p-p输出时的失真为-81 dBc,在50 V p-p和60 V p-p输出时的失真为-82 dBc,在 16 V p-p和32V p-p输出时的失真为-86.5 dBc,频率均为100 kHz。

然后测量直流线性度、增益精度和输入范围。图6显示了扫描输入直流信号时缓冲器的输入失调。

任何具有有用输入特性的放大器都可以如上所述进行自举,从而配合高压信号工作。超低输入噪声或超低失调放大器可以在数百伏下运行。

万用表难以在±40 V信号的背景下解析亚微伏变化,但由于这是一个缓冲器,ADI工程师可以简单地将电压表从输入连接到输出以找到偏移量,并使用一个敏感范围。对于±40 V输入,该万用表的共模抑制小于1μV(该测试的输入短路)。

曲线中的扰动是由低频噪声(尤其是热扰动)引起的。有人在附近或空调就能导致气流和热变化,致使电路中出现微伏级的塞贝克和热电偶电压误差。由于没有很好的屏蔽室,但用一些衣服遮住电路以防止气流影响。即便如此,结果仍有0.6μV rms的漂移。

在噪声中,无负载(绿色)曲线表明增益误差约为0.03 ppm。还算不赖。未自举的LTC6240的标称增益误差为5.6 ppm,CMRR误差导致的最差情况增益误差为100 ppm。当加载50 kΩ(紫色)时,看到增益误差为-0.38ppm。该负载增益误差相当于0.02Ω的输出阻抗。很难知道0.02Ω来自何方——它可能是负载电流调制 Vp或Vm,并通过LTC6240内的共模抑制或增益限制过程起作用,或者它可能只是导线和电路板电阻。无论如何,为使增益保持精确,可以将LTC6240的反馈远程连接到最终负载,形成一个开尔文连接。图7显示了小信号脉冲响应。

对绿色通道中的振铃,其实是高压放大器的输出。它不是自行振铃的,原因只是使用的示波器探针和板对板接地很一般。黄色通道是缓冲器输出,它是由Cin + Rin主导的简单指数图像。

图8显示了大信号脉冲响应,输入压摆率为±32 V/μs——很好很平滑的响应。

图9显示了缓冲器对过载压摆率的响应。在100 kHz时80 V p-p输要求峰值压摆率为±25 V/μs,这在所示的±32 V/μs能力范围内。

请注意,输入滤波器将过载压摆率限制为缓冲器可以处理的量。纹波是自举电路无法跟随输出压摆的伪像,这导致压摆期间输入裕量反复过载。减小Cin会迫使输入压摆率变得更大,自举电路将无法跟随,导致波纹更难看。

总结

本文展示了一种让低压运算放大器缓冲器有效自举成高压缓冲器的方法。ADI工程师采用了一款具有出色输入特性的运算放大器,并进一步提高其性能,使其电压范围、增益精度、压摆率和失真性能均优于原来的运算放大器。在座的筒子们,你们对这样的方法有什么的见解呢?在文末留言吧,咱们一起讨论~

责任编辑:haq

-

放大器

+关注

关注

142文章

12416浏览量

210005 -

电流

+关注

关注

40文章

5997浏览量

129893 -

时钟缓冲器

+关注

关注

2文章

84浏览量

50706

原文标题:能否让低压放大器自举来获得高压缓冲器?

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么是缓冲放大器

电压型缓冲放大器和电流型缓冲放大器的作用?

电流型运算放大器是什么?

请问如何将缓冲器与AD8221搭配使用 ?

分立式仪表放大器与集成仪表放大器的区别

如何设计和使用缓冲器

三态输出的缓冲器有哪些用途?

为什么共漏级又称为源极跟随器、电压缓冲器?

MAX13256的缓冲器设计

廉价的高速放大器提供灵活的时钟缓冲器

用缓冲放大器解决VCO问题

运算放大器的工作原理和工作模式

让低压运算放大器缓冲器有效自举成高压缓冲器的方法

让低压运算放大器缓冲器有效自举成高压缓冲器的方法

评论