互联标准之战,CXL正在走向胜利

在上世纪总线大战之下,各大厂商为了自己的开放标准纷纷全力出击,最终只留下PCIe统治着服务器市场。而在高性能计算对延迟、带宽要求越来越高的情况下,互联技术同样开展了类似的大战。CXL、CAPI(OpenCAPI)、CCIX、Gen-Z、AMD的Infinity Fabric与英伟达的NV Link等技术百花齐放,既有开放标准,也有专用标准。

这其中不少开放标准其实也都有对应的厂商在背后支持推动,比如CXL由英特尔主导,CCIX由赛灵思主导,OpenCAPI由IBM主导,Gen-Z由慧与主导。但这种分割的局面自然不是服务器市场内其他厂商想要看到的,他们希望能统一起来,为混合计算架构提供通用的互联方案,而不是一味地提供多种标准支持。好在这种局面似乎离我们不远了,从各种趋势来看,CXL正在走向最终的胜利。

从“言和”到“吞并”

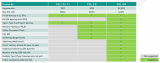

CXL作为开放的行业互联标准,其作用是为主处理器与其他设备之间提供高带宽低延迟的连接,比如加速器、内存扩展和其他智能I/O设备。CXL诞生的时间其实并不长,离第一版规范的发布也才过去两年而已,其联盟创始成员包括阿里巴巴、华为、英特尔和微软等企业。CXL诞生之际,CCIX、OpenCAPI和Gen-Z早就在耕耘服务器市场了,也利用这提前几年的时间召集了不少联盟成员,那么最晚面世的CXL又是如何杀出重围的呢?

首先自然是来自联盟成员的支持,尤其是当前服务器CPU份额遥遥领先的霸主英特尔,像Gen-Z这样的标准要想做CPU互联,必须要CPU端的支持。但英特尔并未加入Gen-Z联盟,更不用谈支持了,GPU、加速器等产品想要在服务器市场继续生存下去,加入英特尔推行的CXL阵营成了一个理所当然的选择。

CXL 1.0与1.1用例 / CXL联盟

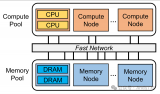

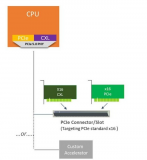

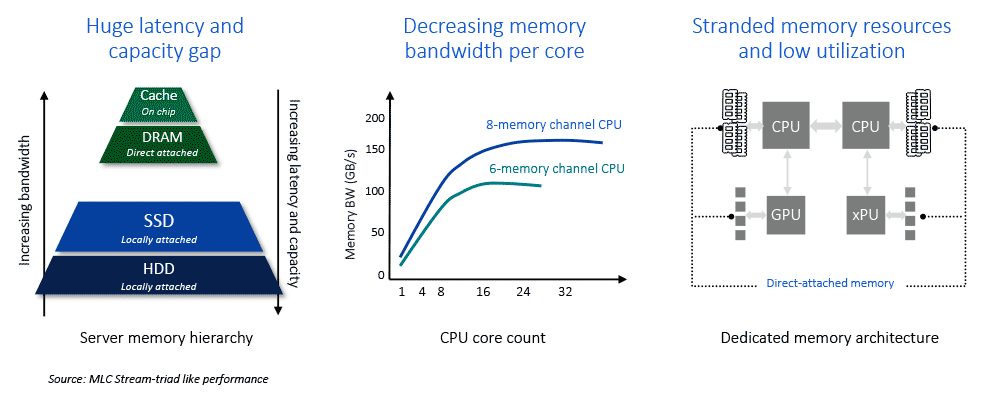

其次,CXL的I/O基于PCIe 5.0,可以充分利用它在速度和带宽上的优势。利用CXL,部分NIC等无本地内存的加速器可以直接使用处理器的DDR内存;而自带DDR或HBM内存的加速器,比如GPU、FPGA和ASIC设备等,可以实现内存互用,大大提高异构工作下的性能。内存扩展之类的产品利用CXL不仅可以省去宝贵的DRAM插槽,还能一并提高内存带宽。

Gen-Z这样的标准虽不愿意服输,但在CXL如此强势的崛起下,内存厂商、IP厂商、处理器厂商和加速器厂商纷纷加入了CXL联盟,甚至慧与也是CXL的创始成员。Gen-Z无奈之下也只能选择“握手言和”。2020年,CXL联盟与Gen-Z联盟达成合作备忘录,强调了两者之间的合作共赢,CXL专注于一致的节点层级计算,也就是机架内CPU、GPU和加速器之间的互联,而Gen-Z负责支持机架之间的互联。

而今年11月10日,Gen-Z联盟与CXL联盟正式发布公告,两者签署了一份意向书,在各方同意后,将把所有Gen-Z规范和资产转移给CXL联盟,双方联盟成员将专注于CXL这唯一的互联标准,减少无意义的重复工作。如此一来,CXL基本正式“吞并”了Gen-Z,加上两者之间互补的特性,CXL已经确立了自己的领先地位。

来自厂商的支持

近几个月内,英特尔、AMD等大厂都相继推出了自己的服务器产品,从他们的产品支持来看,我们也能看出倾向于哪种互联标准。作为CXL的主导者,英特尔自然不会减少对CXL的支持,其公布的Sapphire Rapids处理器将提供PCIe 5.0和CXL 1.1的支持;尽管刚发布的Milan-X并没有CXL支持,但AMD也同时宣布下一代Epyc处理器Genoa将提供CXL支持。

Arm Neoverse路线图 / Arm

Arm的Neoverse N2平台已经提供了对CCIX 2.0和CXL 2.0的支持,Arm也宣布下一代Poseidon平台将支持下一代CCIX与CXL标准;SiFive不久前公布的Performance P550核心也将通过Chip2Chip-Link,支持外部CXL连接。

因此从处理器的支持来看,无论是x86、Arm还是RISC-V似乎都开始在往CXL布局。三星也在今年发布了首个支持CXL的DDR5内存模组,消除了传统DDR内存通道数的限制,可将内存扩展至TB级的同时,还能极大降低由于缓存造成的系统延迟。

小结

CXL仅用了两到三年的时间,就走完了其他标准长途跋涉的路,不过由于支持PCIe 5.0和CXL的服务器处理器普遍都在2022年面世,加速器和内存厂商跟进还需要一定的时间。而Gen-Z也并不会就此成为历史,被并入CXL后,未来内存从TB走向PB级,很有可能仍要用到Gen-Z所代表的互联技术。

在上世纪总线大战之下,各大厂商为了自己的开放标准纷纷全力出击,最终只留下PCIe统治着服务器市场。而在高性能计算对延迟、带宽要求越来越高的情况下,互联技术同样开展了类似的大战。CXL、CAPI(OpenCAPI)、CCIX、Gen-Z、AMD的Infinity Fabric与英伟达的NV Link等技术百花齐放,既有开放标准,也有专用标准。

这其中不少开放标准其实也都有对应的厂商在背后支持推动,比如CXL由英特尔主导,CCIX由赛灵思主导,OpenCAPI由IBM主导,Gen-Z由慧与主导。但这种分割的局面自然不是服务器市场内其他厂商想要看到的,他们希望能统一起来,为混合计算架构提供通用的互联方案,而不是一味地提供多种标准支持。好在这种局面似乎离我们不远了,从各种趋势来看,CXL正在走向最终的胜利。

从“言和”到“吞并”

CXL作为开放的行业互联标准,其作用是为主处理器与其他设备之间提供高带宽低延迟的连接,比如加速器、内存扩展和其他智能I/O设备。CXL诞生的时间其实并不长,离第一版规范的发布也才过去两年而已,其联盟创始成员包括阿里巴巴、华为、英特尔和微软等企业。CXL诞生之际,CCIX、OpenCAPI和Gen-Z早就在耕耘服务器市场了,也利用这提前几年的时间召集了不少联盟成员,那么最晚面世的CXL又是如何杀出重围的呢?

首先自然是来自联盟成员的支持,尤其是当前服务器CPU份额遥遥领先的霸主英特尔,像Gen-Z这样的标准要想做CPU互联,必须要CPU端的支持。但英特尔并未加入Gen-Z联盟,更不用谈支持了,GPU、加速器等产品想要在服务器市场继续生存下去,加入英特尔推行的CXL阵营成了一个理所当然的选择。

CXL 1.0与1.1用例 / CXL联盟

其次,CXL的I/O基于PCIe 5.0,可以充分利用它在速度和带宽上的优势。利用CXL,部分NIC等无本地内存的加速器可以直接使用处理器的DDR内存;而自带DDR或HBM内存的加速器,比如GPU、FPGA和ASIC设备等,可以实现内存互用,大大提高异构工作下的性能。内存扩展之类的产品利用CXL不仅可以省去宝贵的DRAM插槽,还能一并提高内存带宽。

Gen-Z这样的标准虽不愿意服输,但在CXL如此强势的崛起下,内存厂商、IP厂商、处理器厂商和加速器厂商纷纷加入了CXL联盟,甚至慧与也是CXL的创始成员。Gen-Z无奈之下也只能选择“握手言和”。2020年,CXL联盟与Gen-Z联盟达成合作备忘录,强调了两者之间的合作共赢,CXL专注于一致的节点层级计算,也就是机架内CPU、GPU和加速器之间的互联,而Gen-Z负责支持机架之间的互联。

而今年11月10日,Gen-Z联盟与CXL联盟正式发布公告,两者签署了一份意向书,在各方同意后,将把所有Gen-Z规范和资产转移给CXL联盟,双方联盟成员将专注于CXL这唯一的互联标准,减少无意义的重复工作。如此一来,CXL基本正式“吞并”了Gen-Z,加上两者之间互补的特性,CXL已经确立了自己的领先地位。

来自厂商的支持

近几个月内,英特尔、AMD等大厂都相继推出了自己的服务器产品,从他们的产品支持来看,我们也能看出倾向于哪种互联标准。作为CXL的主导者,英特尔自然不会减少对CXL的支持,其公布的Sapphire Rapids处理器将提供PCIe 5.0和CXL 1.1的支持;尽管刚发布的Milan-X并没有CXL支持,但AMD也同时宣布下一代Epyc处理器Genoa将提供CXL支持。

Arm Neoverse路线图 / Arm

Arm的Neoverse N2平台已经提供了对CCIX 2.0和CXL 2.0的支持,Arm也宣布下一代Poseidon平台将支持下一代CCIX与CXL标准;SiFive不久前公布的Performance P550核心也将通过Chip2Chip-Link,支持外部CXL连接。

因此从处理器的支持来看,无论是x86、Arm还是RISC-V似乎都开始在往CXL布局。三星也在今年发布了首个支持CXL的DDR5内存模组,消除了传统DDR内存通道数的限制,可将内存扩展至TB级的同时,还能极大降低由于缓存造成的系统延迟。

小结

CXL仅用了两到三年的时间,就走完了其他标准长途跋涉的路,不过由于支持PCIe 5.0和CXL的服务器处理器普遍都在2022年面世,加速器和内存厂商跟进还需要一定的时间。而Gen-Z也并不会就此成为历史,被并入CXL后,未来内存从TB走向PB级,很有可能仍要用到Gen-Z所代表的互联技术。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

amd

+关注

关注

25文章

5204浏览量

132697 -

英特尔

+关注

关注

60文章

9436浏览量

169025 -

服务器

+关注

关注

12文章

8134浏览量

82615

发布评论请先 登录

相关推荐

利用CXL技术重构基于RDMA的内存解耦合

本文提出了一种基于RDMA和CXL的新型低延迟、高可扩展性的内存解耦合系统Rcmp。其显著特点是通过CXL提高了基于RDMA系统的性能,并利用RDMA克服了CXL的距离限制。

发表于 02-29 10:05

•574次阅读

什么是CXL技术?CXL的三种模式、类型、应用

CXL的目标:解决CPU和设备、设备和设备之间的内存鸿沟。服务器有巨大的内存池和数量庞大的基于PCIe运算加速器,每个上面都有很大的内存。内存的分割已经造成巨大的浪费、不便和性能下降。CXL就是为解决这个问题而诞生。

佰维发布CXL 2.0 DRAM,赋能高性能计算

导语: CXL是一种开放式全新互联技术标准,可在主机处理器与加速器、内存缓冲区、智能I/O设备等设备之间提供高带宽、低延迟连接,从而满足高性能异构计算的要求,并且其维护CPU/GPU内存空间和连接

发表于 12-27 15:17

•130次阅读

佰维发布CXL 2.0 DRAM,赋能高性能计算

导语: CXL是一种开放式全新互联技术标准,可在主机处理器与加速器、内存缓冲区、智能I/O设备等设备之间提供高带宽、低延迟连接,从而满足高性能异构计算的要求,并且其维护CPU/GPU内存空间和连接

关于CXL的功能与特性详解

CXL.io 和CXL.cache 是CXL 协定中的两个子协定,它们的功能和用途有所不同,主要是为了引入非对称的概念;CXL.io 类似于PCIe 的事件(event),主要用于初始

CXL技术的三种模式 CXL技术与其他技术的对比

CXL的目标:解决CPU和设备、设备和设备之间的内存鸿沟。服务器有巨大的内存池和数量庞大的基于PCIe运算加速器,每个上面都有很大的内存。内存的分割已经造成巨大的浪费、不便和性能下降。CXL就是为解决这个问题而诞生。

发表于 10-30 14:30

•5422次阅读

Credo携手行业伙伴在OCP 2023全球峰会上共同宣布将助力CXL AEC及光互联标准化

Credo产品副总裁兼HiWire全球产业联盟组织者Don Barnetson表示:“HiWire全球产业联盟在现如今云运营中大量使用的以太网AEC的标准化进程中扮演关键角色。我们新的CXL工作流将带来同样的创新——在CXL柜内

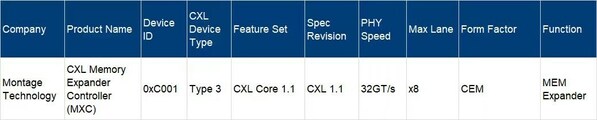

澜起科技MXC芯片率先列入CXL官网的合规供应商清单

上海2023年8月21日 /美通社/ -- 近日,澜起科技的CXL内存扩展控制器(MXC)芯片成功通过了CXL联盟组织的CXL1.1合规测试,被列入CXL官网的合规供应商清单(

澜起科技MXC芯片成功通过CXL联盟组织的CXL1.1合规测试

近日,澜起科技的CXL内存扩展控制器(MXC)芯片成功通过了CXL联盟组织的CXL1.1合规测试,被列入CXL官网的合规供应商清单。澜起科技是全球首家进入

平凡英雄 | 从一个胜利走向下一个胜利

6月,国能北电胜利能源无人驾驶矿卡应用项目顺利终验,这是国能集团首个完成终验的无人重型矿卡项目。从7台220吨级矿卡改造、无人运输系统部署、无安全员24小时运行到无人运输效率达到有人作业,踏歌

揭开CXL的神秘面纱:概述

CXL 是一种在主机(通常是 CPU)和设备(通常是附加了内存的加速器)之间实现高带宽、低延迟链接的技术。CXL 堆栈专为低延迟而设计,使用 PCIe 电气和附加卡的标准 PCIe 外形规格。

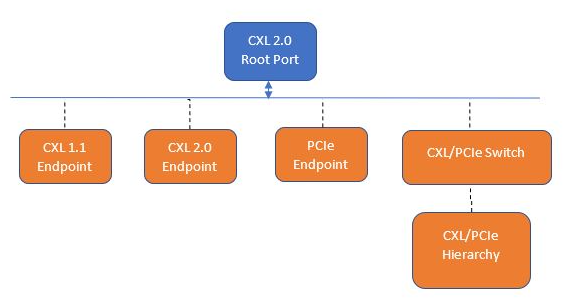

CXL 2.0设备发现的迷人路径

CXL 2.0 规范在 PCIe 配置空间映射寄存器中定义了多个新的 PCIe 指定供应商特定扩展功能 (DVSEC)。以下是 CXL 2.0 设备的一些强制性 DVSEC。

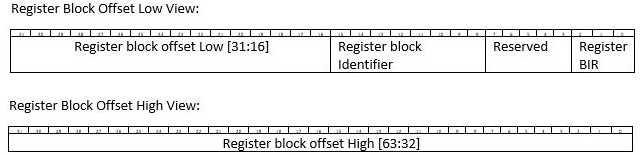

访问CXL 2.0设备中的内存映射寄存器

计算快速链接 (CXL) 1.1 和 CXL 2.0 规范在内存映射寄存器的放置和访问方式上有所不同。CXL 1.1 规范将内存映射寄存器放置在 RCRB(根复合寄存器块)中,而 CXL

互联标准之战,CXL正在走向胜利

互联标准之战,CXL正在走向胜利

评论