一、生成固化文件1、先生成bit文件,再生成固化文件

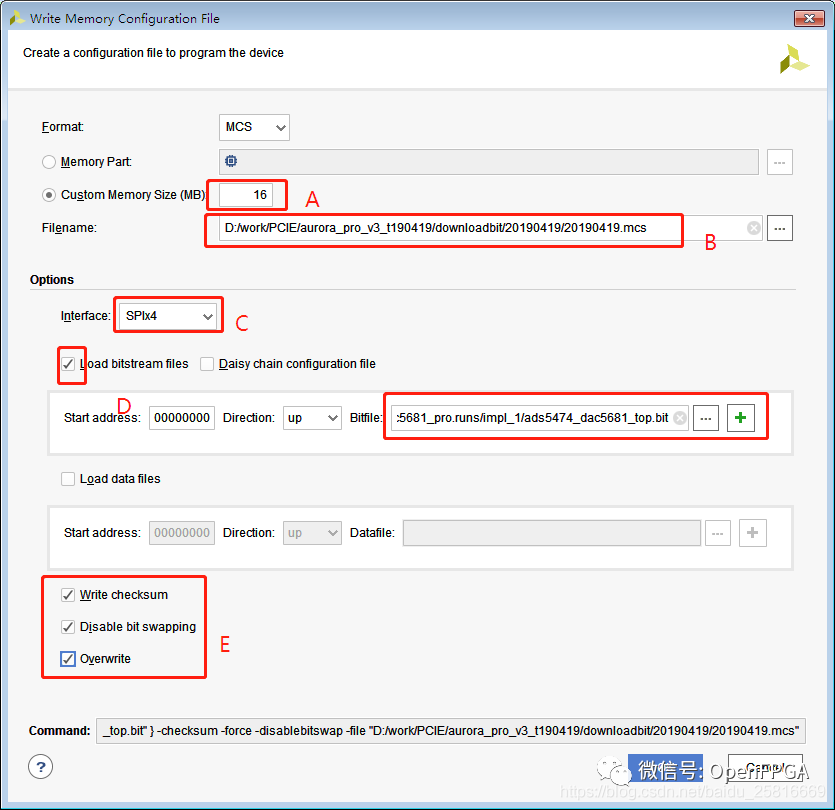

2、生成固化文件步骤

A选择当前flash的大小,注意这里是MB,不是Mb。

B选择要生成的固化文件的保存路径,设置名字。

C选择当前芯片的烧录方式

D选择已经生成的bit文件。

E勾选所有。

3、点击OK,生成完成。

二、固化文件1、连接设备,open Device

1、设置参数

选择芯片的参数

注意芯片的电压。

点击OK后出现下面界面

选择固化的文件.Msc和.Prm文件,其他不用设置,点击OK,开始固化。

固化完成后需要关闭设备,断电后重启。

2、连接固化代码后的设备。

添加lit文件,注意是和bit文件在统一目录下。

如果后面重新生成了bit文件,那么固化的文件也需要再重新生成,两者需要对应。

命令行方式

注意:只用一条命令即可:

其实这条命令就是在第一种方法中下图中command命令复制出来的。这里解释一下这条命令。

write_cfgmem -format mcs -size 128 -interface SMAPx16 -loadbit {up 0x00000000 “M:/led.bit” } -checksum -force -disablebitswap -file “C:/Users/Xilinx/Vivado/led.mcs”

write_cfgmem:顾名思义,这就是写配置存储文件,也就是生成配置存储文件。

format:生成存储文件的格式,这里是 mcs

size:这里指定Flash大小,这里是以Byte为单位

interface:指定Flash接口是SMAPx16

loadbit: 指定生成MCS文件需要的比特流文件,并且指定MCS文件存放起始地址是 0x00000000,地址增长方向是向上增长。

file:指定mcs文件存放地址及文件名

参考链接

ug908

ug835

https://blog.csdn.net/MaoChuangAn/article/details/80763034

编辑:jq

-

FlaSh

+关注

关注

10文章

1550浏览量

146645 -

代码

+关注

关注

30文章

4555浏览量

66751 -

bit

+关注

关注

0文章

47浏览量

31853

原文标题:【Vivado那些事】Vivado两种生成、固化烧录文件

文章出处:【微信号:gh_339470469b7d,微信公众号:FPGA与数据通信】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AMD Versal AI Edge自适应计算加速平台之准备工作(1)

如何禁止vivado自动生成 bufg

labview生成exe文件如何配置文件

keil如何生成bin文件

ADgerber文件怎么生成PCB

常见的ARM架构分为两种一种是M系列另外一种是A系列,这两种有什么区别啊?

Vivado设计流程指导手册

Vivado使用指南

用 TCL 定制 Vivado 设计实现流程

MES50HP——FPGA与CPLD的下载与固化

Vivado布线和生成bit参数设置

Vivado两种生成固化烧录文件的教程

Vivado两种生成固化烧录文件的教程

评论