在高速磁浮交通系统中,车载测速定位单元对车辆的位置和速度进行实时测量,并将位置和速度信号通过无线电系统传送至地面上的牵引控制系统和运行控制系统,以用于长定子直线同步电机牵引的反馈控制,以及车辆运行的指挥和安全防护。测速定位单元是牵引和运控系统闭环控制的核心与关键。

测速定位单元紧邻悬浮电磁铁及长定子绕组和铁心,处于悬浮磁场和牵引磁场中,电磁环境非常复杂,这对其通信设备的电磁兼容性能提出了很高的要求。另外,为满足牵引控制系统的需求,测速定位信号的精度要求相当高。因此,测速定位信号传输的速度、实时性及可靠性都面临挑战。基于以上考虑,本文提出了基于DSP和FPGA的磁浮列车同步485通信方式的研究,以解决上述挑战。

同步485的实现方法

考虑到测速定位单元的工作环境及通信功能需求,在选择该单元与车载无线电系统之间的通信方式时,经过分析,本研究采用了传输速率较高的同步通信方式,并使用屏蔽性能较好的双绞线实现RS-485平衡型差分传输。

接口设计及通信协议

测速定位单元与车载无线电控制单元之间的通信接口关系如图1所示。车载无线电控制单元为主控方,车辆测速与定位单元为受控方。通信双方均由收发器和控制器构成,收发器之间采用RS-485同步串行接口方式,每个接口有4对差分线。

图1中,CLK为时钟信号,ANF为无线电请求信号,UEF为门控信号,DATA为数据信号。车辆测速定位单元每20ms向无线电控制单元发送一次数据,传输速率为512kbps。为了防止小脉冲信号的干扰,ANF信号的宽度为10个CLK信号;在ANF信号变为低电平后,等待10个CLK信号宽度,UEF才开始跳变为有效。ANF、UEF、DAFA信号均在CLK的上升沿变化。在无信号传输时,UEF、DATA、ANF均为低电平,时钟信号保持传输。数据传输采用左移方式,即先传高位,后传低位。信息帧格式如表1所示。

同步485的收发器实现

在本文所论述的通信系统中,车辆测速定位单元及车载无线电控制单元双方均采用XC2S100作为通信收发器,模拟同步485的发送与接收时序。同步485的FPGA设计主要是基于Verilog硬件描述语言,所使用的EDA工具包括ISE(含其内部集成工具)、Modelsim。

时钟及定时信号的的产生

车载无线电控制单元需要产生速率为512k的时钟信号与20ms一次的ANF信号。另外,该单元在串行接收定位数据时接收时钟应为512k(波特率时钟)的16倍,即8M。因此,分频器在同步485通信方式中得到有效应用。

对偶数分频,只需设计一个计数器进行计数,待计数至分频数的二分之一时,使分频后的时钟电平翻转即可;奇数分频较为复杂,因为计数器不能对非整数进行计数,需使用一定的算法进行处理。这里对奇数分频模块进行功能仿真后的波形见图2。

ANF信号每隔20ms发送一次,每次发送脉宽为10个时钟周期。ANF信号的产生可以分成两部分实现:首先产生间隔20ms的脉冲信号,然后把此脉冲信号的宽度变成10个时钟周期。

串行数据的发送与接收

产生串行数据时,根据通信协议的要求,测速定位单元每隔20ms应串行移出72bits数据。如果每个发送时钟周期移出一位,则需要72个时钟周期才能全部移出,因此门控信号也需要保持72个时钟周期的宽度。

接收串行数据时,同步串行接收一帧(72bits)数据与异步串行接收是不同的。由于收发时钟不是异步的,因此不能以判断在空闲态以后出现的第一个低电平作为一帧的开始,而是以门控信号(UEF)的上升沿作为一帧数据到来的判断。为了避免数据传输过程中毛刺的影响,我们仍以波特率时钟的16倍进行接收,即每隔16个波特率时钟周期采样一次,因此,每个数据将在传输的每一位的中点处被采样。

串行数据发送与接收的仿真时序图见图3。

收发器与控制器之间的数据交换

基于RS-485的同步通信时序是用FPGA作为通信收发器来模拟的,但是通信数据最终是与系统的CPU进行数据交换的。在该通信方式的设计中,通信双方均采用TMS320F2812作为通信控制器。FPGA与DSP的数据交换必须满足一定的时序,才能保证测速定位单元向车载无线电控制单元实时地传输位置及速度信号。本系统中,DSP控制器采用C语言进行软件设计。

测速定位单元侧DSP与FPGA的数据交换

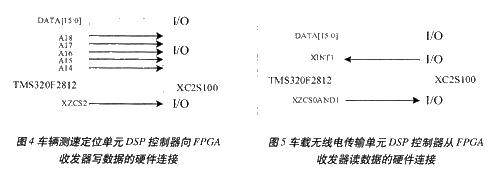

TMS320F2812的外部存储器XINTF可供选择的外部地址空间有XINTF0、XINTF2及XINTF6。其中XINTF0使用XZCS0AND1作为片选信号,外部存储器扩展空间为8K;XINTF2与XINTF6分别使用XZCS2、XZCS6AND7作为片选信号,外部存储器扩展空间均为0.5M。测速定位单元在发送位置速度信息时,通过DSP的数据线传输到FPGA,DSP根据相应的外部存储器片选信号找出对应的地址,在从底层传感器得到一个新的定位数据后写入该地址。相对应的硬件连接框图见图4。

根据协议要求,定位信息每次发送时包括5个字节的用户数据和2个字节的CRC校验,因此,16bits数据线至少需要连续发送四次,才能将底层的定位信息完整地传送到FPGA。

为了减少硬连线,这里只连接地址线的高五位,对其中的低四位地址线进行4~16译码,最高位地址线作为该译码器的使能信号。取对应于一个外部存储器片选信号的四个地址,比如片选信号XZCS2为低,即可选用0xe0000,0xe4000,0xe8000,0xec000四个地址作为DSP向FPGA写数据的地址。

由于每个不同的地址都对应一个地址译码值,当四个译码值都出现后才可认为一次定位信息传送完成。这时把连续接收到的七个字节加上帧头及帧尾,作为测速定位单元发送给车载无线电控制单元的一帧数据。

车载无线电控制单元侧DSP与FPGA的数据交换

为了避免占用过多的CPU资源,车载无线电控制单元中DSP从FPGA读数据时不采用查询方式,而采用外部中断来接收数据。将DSP的16bits数据线与FPGA连接,DSP的XINT1也连接到FPGA的I/O管脚。若选用XZCS0AND1作为外部存储器片选信号,则DSP从FPGA读数据的寻址空间范围为0x002000—0x004000,这个地址范围内所读出的数据即为数据线上传送到DSP的定位数据。相对应的硬件连接框图见图5。

由于FPGA传送到DSP的一帧数据为72bits,因此通过16bits数据线传输需要5次才能传送完,每16bits数据到达时产生一次外 部中断。设波特率时钟为512k,假设来自定位单元完整的一帧数据为0x02123456789abcde03,车载无线电单元通过16bits数据线分次转发到DSP的数据则为0x0002、0x1234、0x5678、0x9abc及0xde03。数据及中断信号产生的时序如图6所示。由图6可以看出,每对应移出一次dataout,都会相应地发出一个外部中断信号xint1,DSP一旦接收到外部中断,便在中断服务子程序中从16bits数据线读取信号值。为了完整的接收一帧信号,可在外部中断服务程序中定义一个16级FIFO,当从FIFO的最底层读出的数据为0x02时,便可以判断一帧数据的开始(若在用户数据和校验值中存在0x02,则要进行相应的字符转义),依次接收以下的数据便得到完整的一帧定位信息。

通信双方的原理图

根据以上对同步485实现方法的描述,在ISE中利用ECS工具所描绘的顶层原理图如图7和图8所示。包括测速定位单元同步数据发送和车载无线电控制单元同步数据接收两部分。

图7中,addr_decode为地址译码模块,用于从DSP完整地接收一帧定位信息;tra485data为串行数据及门控信号发送模块。其中,din(15:0)直接来自DSP的16bits数据线;addr(3:0)与DSP的A17~A14地址线相连;clkin及anfin信号由车载无线电控制单元提供。输出的dataout及uefout经过输出缓冲及差分电平转换后送给车载无线电控制单元。

在图8所示的车载无线电控制单元同步数据接收方的原理图中,divide_512k为发送时钟产生模块,产生通信所需的波特率时钟;anf_shift用于产生无线电请求信号;rec485data用于串行接收定位信息并通过dataconvert模块转发到通信控制器。其中,Dataout(15:0)直接通过数据线连到DSP,Xint1则连到DSP的外部中断1。anfout和clkout由输入的晶振频率分频后得到,经输出缓冲及差分电平转换后送给车辆测速定位单元。

结语

在高速磁浮列车特殊的通信环境中,基于RS-485物理层的同步通信方式体现出其抗干扰性强、实时性好、误码率低等优点,且实现原理简单。利用FPGA所实现的通信收发器设计灵活、可靠性高,其功能在实际应用中已得到验证。

责任编辑:gt

-

dsp

+关注

关注

544文章

7682浏览量

344350 -

FPGA

+关注

关注

1602文章

21320浏览量

593158 -

无线电

+关注

关注

58文章

2070浏览量

115093

发布评论请先 登录

相关推荐

基于DSP和FPGA实现RS-485平衡型差分传输系统的设计

基于DSP和FPGA实现RS-485平衡型差分传输系统的设计

评论