计算机技术领域的格局一直在不断变化。随着新标准的出现,需要改变设备架构。在解决从DDR3到DDR4 的世代标准更改时,该说法同样正确。

随机存取存储器的这些进步也带来了整体性能的显着提高。因此,要利用最新的RAM,就需要PCB设计上的改变。就像USB标准从USB 2.0升级到USB 3.0一样。随着对更大处理能力,更好性能和更高水平功能的需求不断推动行业发展,这些类型的变化是连续且必要的。

尽管大多数人不会注意到或看到PCB设计所需的必要体系结构更改,但这并不会减少这些关键更改的重要性。

DDR4实现需要哪些PCB布局更改?

DDR4或Double Data Rate 4有两种不同的模块类型。So-DIMM或小型双列直插式内存模块(260针)已在便携式计算设备(如笔记本电脑)中使用。另一种模块类型是在台式机和服务器等设备中使用的DIMM或双列直插式内存模块(288针)。

因此,架构的第一个变化当然是由于引脚数。先前的版本(DDR3)将240针用于DIMM,将204针用于So-DIMM。鉴于前面提到的,DDR4在其DIMM应用中使用了288针。随着引脚或触点的增加,DDR4提供了更高的DIMM容量,增强的数据完整性,更快的下载速度以及更高的电源效率。

伴随着整体性能的提高,还采用了弧形设计(底部),可实现更好,更安全的连接,并提高安装过程中的稳定性和强度。另外,有一些基准测试证实DDR4可以将性能提高50%,并可以达到3200 MT(每秒兆传输)。

此外,尽管使用较少的功率,但仍可实现这些性能提升;1.2伏特(每个DIMM),而不是其先前版本的1.5到1.35伏特要求。所有这些变化意味着PCB设计人员必须重新评估其设计方法以实现DDR4。

DDR4 PCB设计指南

可以理解,如果您希望电子设备或组件以最佳水平运行,则需要精确而准确的PCB设计,其中包括DDR4的实现。除了对设计准确性的要求外,还必须遵守当今的内存要求。

PCB设计人员还必须考虑其他各种因素。例如空间分配和关键连接。还需要管理初始设计阶段,因为设计必须满足布线拓扑和设计规范才能成功实现。

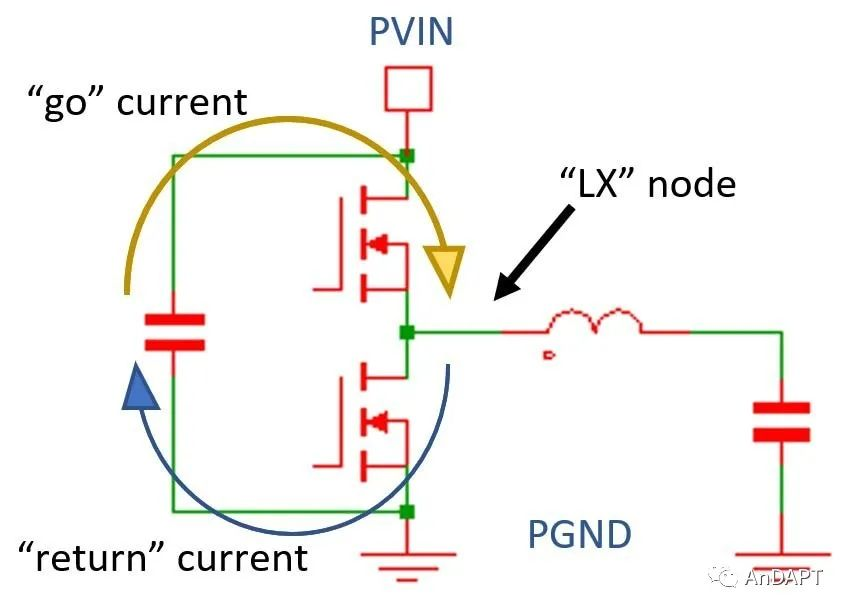

PCB应遵循布线和最佳实践(PCB)来有效管理数据。如果与该实践有任何偏差,可能会导致多个问题,包括磁化率和辐射发射。PCB设计人员还应利用适当的技术进行大规模扇出,高边沿速率以保持低误码率以及1.6至3.2 Gbps的数据范围。同样,如果没有适当的设计技术,您的PCB将遇到信号完整性问题,并导致串扰和由此产生的(过度)抖动。

DDR4布线准则以及长度和间隔规则

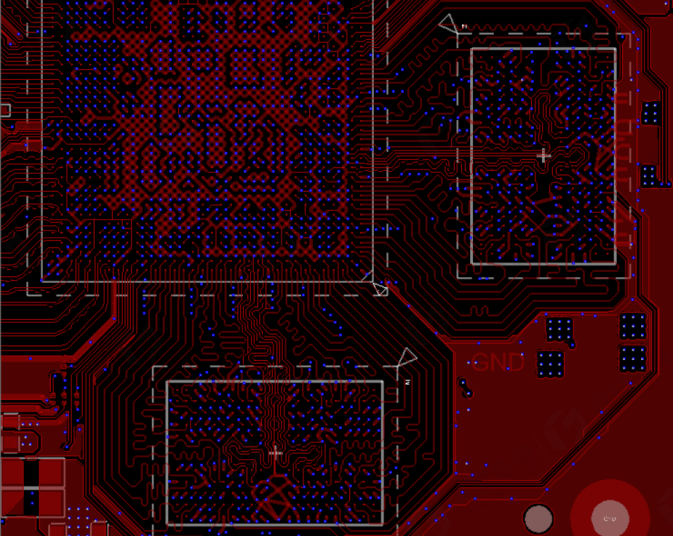

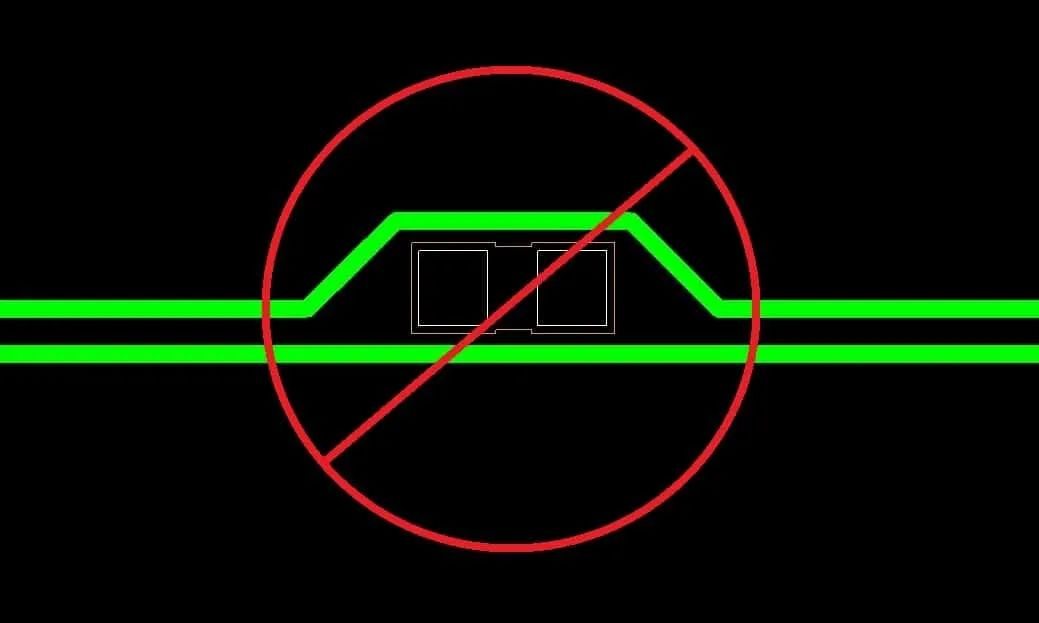

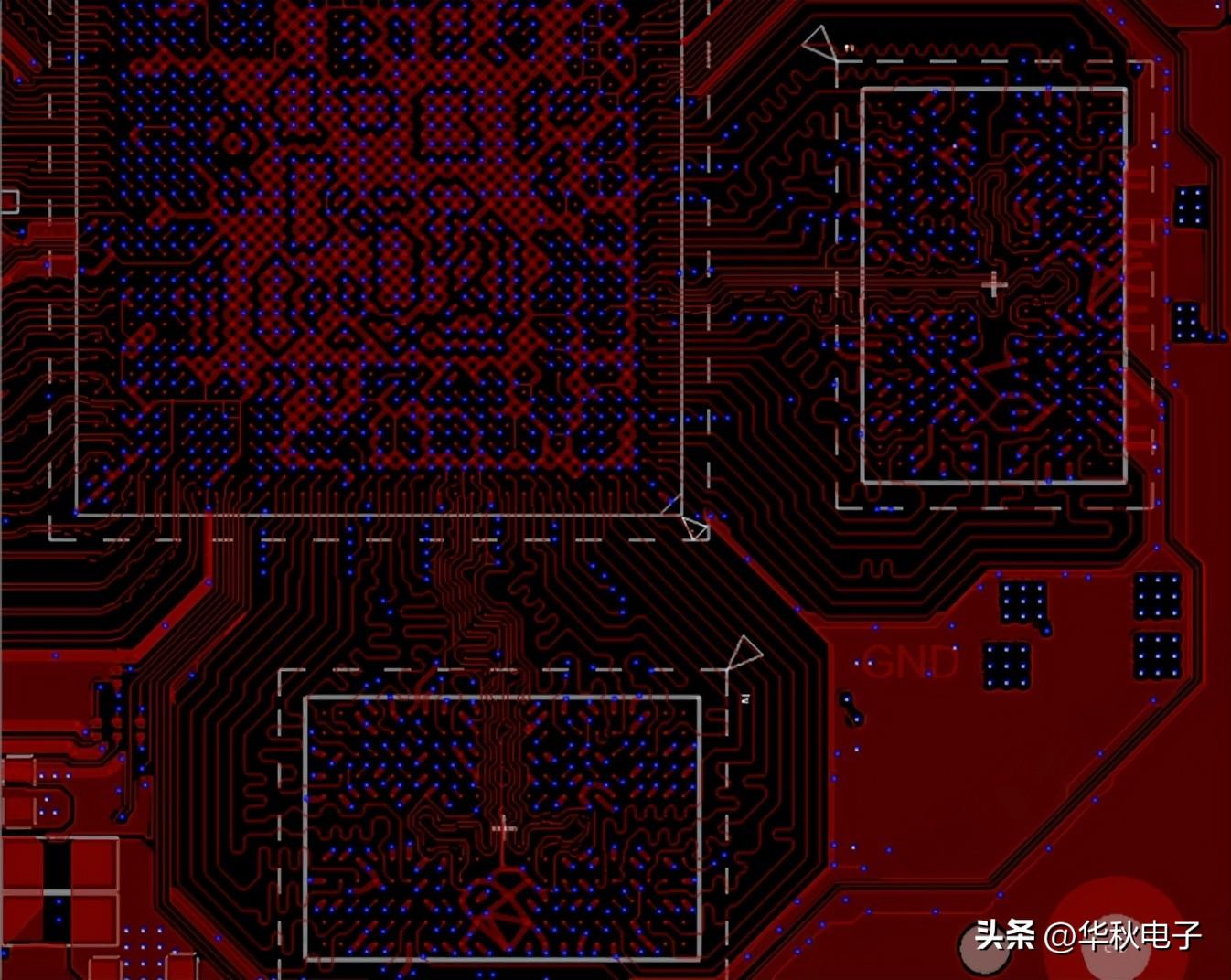

在PCB设计中,要获得最佳的布线路径,既需要正确安装DIMM接口,也需要正确使用存储芯片。通常,DDR4 SDRAM需要较短的路径和适当的间隔,以实现峰值时序和最佳信号完整性。PCB设计人员还应在相关信号组中采用引脚交换。另外,在实现过程中,应避免在空隙上路由信号,避免信号层彼此相邻以及参考平面分裂。

同时,还应在可行的情况下在电源层或适当的接地(GND)之间路由存储接口信号。此外,您可以通过在同一层的同一字节通道组中路由DQ(输入/输出数据),DQS(数据选通)和DM(数据掩码)信号来帮助减少或消除传输速度差异。而且,由于时钟信号的传播延迟比DQS信号更长,因此时钟信号走线通常需要比双列直插式存储模块中最扩展的DQS走线更长的长度。

最后,必须记住,每个板的堆叠都是不同的,间距要求也是如此。因此,有必要利用场求解器(Clarity 3D Solver)在关键信号之间建立低于-50dB的串扰。注意:DQS的时钟没有长度要求,但是命令/控制/地址的时钟确实有长度要求。但是,长度要求取决于材料的Dk(介电常数)和每个SDRAM的负载。

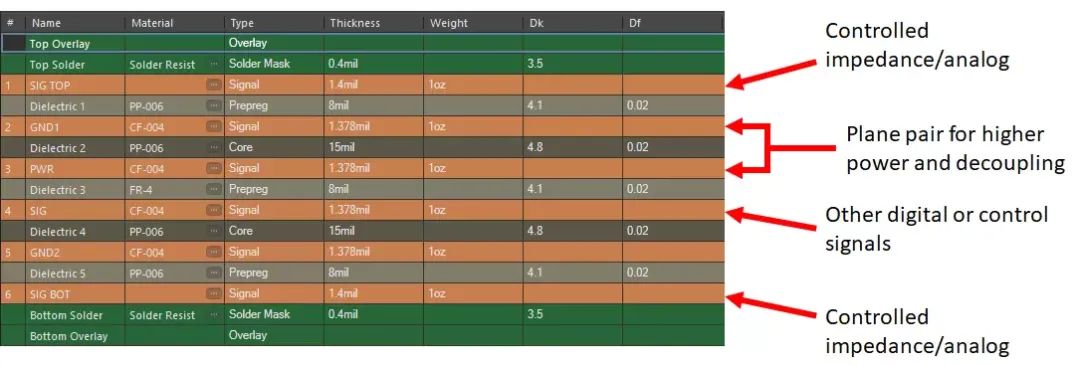

DDR4层分配和数据通道参考

可以将DQS,DQ和DM网络分配给堆叠中任何可用的内部带状线层。而地址/命令/控制和时钟应在更靠近SDRAM的层上进行路由,以通过耦合最小化。

地址/命令/控制SDRAM通孔应在每个SDRAM处添加接地的通孔(阴影通孔),以减少通孔耦合。

另外,根据控制器的地址和控制参考功率或接地。应该注意的是,DIMM具有地址和控制参考功率,而板载BGA(球栅阵列)很少具有地址和控制参考功率。

DDR4与其前身(DDR3)一样,在考虑实现时也需要一种新的设计方法。显然,在设计要求方面有几项更改以适应升级后的性能,这是创新的副作用。但是,遵循适当的设计和拓扑技术将使这个新的,当前的世代标准产生最高的性能。

-

PCB设计

+关注

关注

392文章

4572浏览量

83222 -

PCB设计软件

+关注

关注

0文章

51浏览量

10153 -

线路板设计

+关注

关注

0文章

55浏览量

7948 -

华秋DFM

+关注

关注

20文章

3483浏览量

3907

发布评论请先 登录

相关推荐

6层PCB叠层设计指南

【PCB设计干货】DDR电路的PCB布局布线要求

DDR电路的PCB布局布线要求

DDR电路的PCB布局布线要求

【华秋干货铺】DDR电路的PCB布局布线要求

【华秋干货铺】DDR电路的PCB布局布线要求

DDR电路PCB布局布线技巧

DDR电路的PCB布局布线要求

DDR4 PCB布线指南和PCB架构的建造

DDR4 PCB布线指南和PCB架构的建造

评论