学习 FPGA,在不同层次的人明显有不同的答案。先说一句,说不要开发版的都是菜鸟级选手。

FPGA 层次可划分为,鸡蛋级别,菜鸟级别,老鸟级别,高手级别四类。鸡蛋级别属于还未入门的,这里就先不说了。下面的内容主要介绍如何成为一个菜鸟。

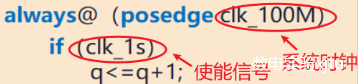

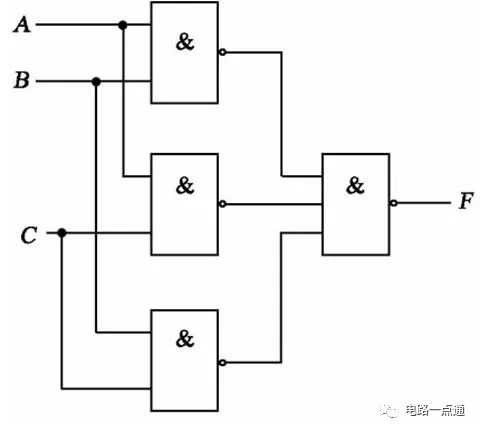

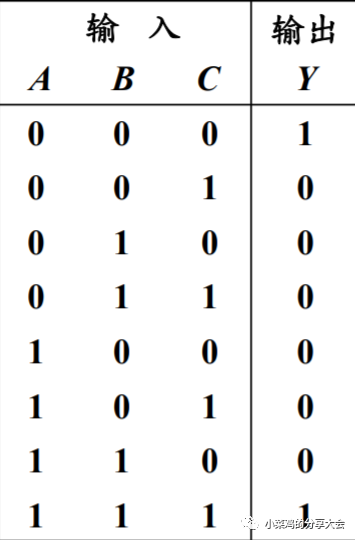

1)熟悉语法,其实你不需要什么都会,但是要记住几个经典的时序,逻辑电路的描述方式。

2)熟悉三个经典电路描述并仿真。仿真其实不是很重要,我开始学习压根没学那个玩意儿,因为要是只做接口那玩意儿没啥用。直接用 ChipSchop 抓抓数据更快。仿真是给做算法,工程相对较大的人用的。三个经典电路分别是,分频器,计数器(可做一个时钟),序列检测器。

这样你就基本熟悉了开发环境了。

3)上板卡跑一个灯,熟悉一个板卡上时钟资源使用,硬件的使用原理。

4)知道了 FPGA 学习主要不在于编程!压根没有编程这回事!!Verilog 是硬件描述语言!描述!!写代码时脑子里必须有电路图!!知道 FPGA 主要学的是硬件和算法!!软件最多能占 10%就不错了!!

只要你能完成这上面的东西,恭喜你进入菜鸟行列,可以在别人设计好 FPGA 方案的条件下完成一些模块的设计了。其实华为招聘员工,很多人 FPGA 水平一开始都差不多这么菜。

先写一下老鸟需要会什么,以后再答怎么做到。

1)FPGA 逻辑资源,特别是时钟资源要非常熟悉。

2)做算法的必须熟悉 sysgen 的使用。说的容易了,sysgen 画画图也没那么容易哦,你要熟悉使用各种滤波器,理论知识要求起点就不小。

3)充分理解 FPGA 从上而下的设计原则,能够编写中等程度的 FPGA 详细设计方案。

4)熟悉时序优化,时序收敛,区域约束等知识。并且能运用到编程之中,解决菜鸟们解决不了的“不科学”的问题。说白了就是会使用 planhead,以及 ISE 中那些你还没接触过的功能。一般菜鸟们 ISE 都只会编程,默认的编译一下,然后下载,ChipSchop 抓抓数看看。

5)能够熟悉 FPGA 常用的接口,不求都会编程,但是要知道他们功能是什么。比如 ADC,DAC,串口,EMIF 等等。并且熟悉 DSP 等 FPGA 周边常用芯片工作原理。

6)熟悉硬件设计,至少要知道 Bank 上 IO 规划怎么好,全局时钟,区域时钟大致怎么规划等等。

等这些都熟悉了,差不多是老鸟了。

责任编辑:pj

-

dsp

+关注

关注

544文章

7681浏览量

344346 -

FPGA

+关注

关注

1602文章

21317浏览量

593136 -

逻辑电路

+关注

关注

13文章

468浏览量

42204

发布评论请先 登录

相关推荐

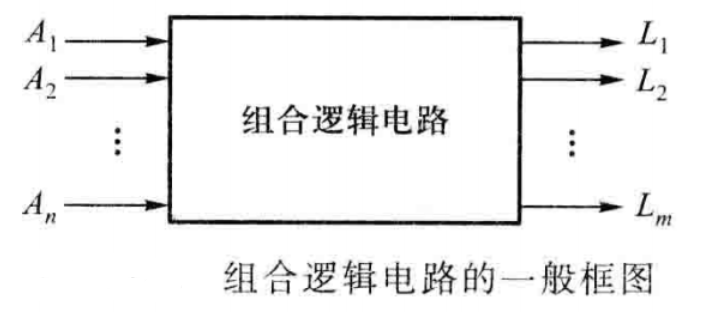

什么是组合逻辑电路和时序逻辑电路?它们之间的区别是什么

时序逻辑电路有哪些 时序逻辑电路和组合逻辑电路区别

时序逻辑电路的分析方法

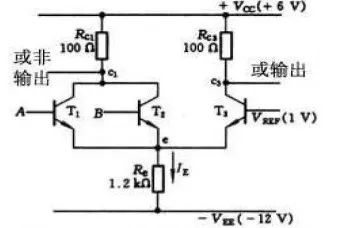

了解逻辑电路的设计与描述方式

了解逻辑电路的设计与描述方式

评论