(文章来源:深讲电磁兼容)

除了与时钟电路输出端相关联的回路会产生电磁辐射以外,电源线回路也是一个主要的电磁辐射源,关于电源回路中产生突变电流的机理,前面章节已经作了介绍。这里通过实验增加一下感性认识。

左图是一个时钟电路电源线回路,请大家关注电源线回路,也就是电池和去耦电容器。

右上图是没有去耦电容器时,电磁辐射的情况。

右下图是安装了去耦电容时,电磁辐射情况。可以看到,电磁辐射强度低了很多。这说明,电源线回路确实有电磁辐射。

因为,没有安装去耦电容时,突变电流存在于电池所连接的电源线回路中,这是一个面积较大的回路。

当安装了去耦电容后,突变电流局限在去耦电容与芯片所连接的回路中,这是一个面积较小的回路,因此产生较小的电磁辐射。

这个实验还告诉我们,去耦电容的安装方式对与电源线回路的辐射有很大影响,我们应该尽量减小去耦电容与芯片之间的电源线回路面积。

(责任编辑:fqj)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电路

+关注

关注

170文章

5480浏览量

169522 -

电磁辐射

+关注

关注

5文章

341浏览量

43355

发布评论请先 登录

相关推荐

PCB线路板叠层设计应该注意的事项

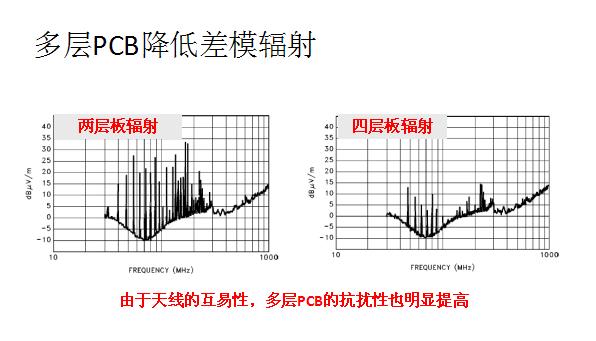

单层板和双层板的电磁兼容问题越来越突出,造成这种现象的主要原因就是信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。要改善线路的

发表于 01-09 15:57

•133次阅读

如何降低运放电路中的电源噪声

来自开关电源或市电网络的高频干扰可能通过空间杂散电容直接耦合到信号回路。设计中的考虑包括:合理的布局、调整电感线圈或变压器放置方向、优化布线,减小关键信号的

发表于 11-21 06:27

什么是环路面积?怎么减小走线的环路电感?

以下一些方法: 1. 缩小环路面积:环路电感与电流路径所围成的面积成正比,因此缩小环路面积可以有效减小环路电感。在进行PCB布线时,可以采用紧凑布局,尽量

如何优化PCB走线来减小回路电感和环路面积?

如何优化PCB走线来减小回路电感和环路面积? 随着电路设计的复杂性和频率的不断提高,电路中的电感和环路造成的影响也越来越明显。因此,优化PCB走线以

电源线和地线过长会加大系统的电磁辐射吗?

的使用,会产生大量的电磁辐射。其中,电磁辐射对人体健康的危害最突出,而长期接触高水平的辐射更容易导致疾病。 所以,正确使用和正确维护电子设备,可以降低环境对

如何抑制时钟电路产生的电磁辐射?

一定的影响。因此,为了抑制时钟电路产生的电磁辐射,需要采取一些措施来降低其产生的电磁辐射水平。 一、由于时钟电路产生的

电源线上的电磁辐射防护要注意什么?

电源线上的电磁辐射防护要注意什么? 电子设备已经成为了现代人日常生活必不可少的一部分。但是它们的使用也带来了一些不良影响,如电磁辐射、射频辐射、两干扰等等。特别是

对产品做电磁兼容设计可以从哪几个方面进行?

电磁辐射和敏感信号的干扰 ...

在进行电磁兼容(EMC)设计时,可以从以下几个方面着手:

电路设计:合理的电路布局和线路布线是EMC设计的基础。通过减少

发表于 06-21 11:51

如果降低USB通信的辐射发射?

能力。

· 地线和电源线的布局:与DC到DC电路类似,合理布局USB的地线和电源线,并尽量减少它们之间的距离。使用短而粗的地线和电源线,减小回路面积

发表于 06-14 09:30

如何降低dc to dc电路的辐射发射?

摘要 : 要降低DC到DC电路的辐射发射,可以采取以下几种方法: 地线和电源线的布局:确保地线和电源线的布局合理,并尽量减少它们之间的距离。

发表于 06-12 14:26

电磁兼容整改100个小技巧

干扰。

· 使用合适的隔离设备和屏蔽设备来分隔敏感设备和干扰源。

· 控制高功率设备的开关过程,减少开关过程中的电磁干扰。

· 使用电磁屏蔽材料和方法来防止电磁辐射。

· 避免信号

发表于 06-09 10:36

如何降低dc to dc电路的辐射发射?

摘要 : 要降低DC到DC电路的辐射发射,可以采取以下几种方法: 地线和电源线的布局:确保地线和电源线的布局合理,并尽量减少它们之间的距离。

发表于 06-06 09:21

电路中减小电源线回路面积以达到降低电磁辐射的目的

电路中减小电源线回路面积以达到降低电磁辐射的目的

评论