1.静电放电之前静电场的效应

2.放电产生的电荷注入效应

3.静电放电电流产生的场效应

尽管印刷线路板(PWB,通常也称之为PCB)的设计会对上述三种效应都产生影响,但是主要是对第三种效应产生影响。下面的讨论将针对第三条所述的问题给出设计指南。

通常,源与接收电路之间的场耦合可以通过下列方式之一减小(这些通用方法也会在其它讨论场的章节中提到):

1.在源端使用滤波器以衰减信号

2.在接收端使用滤波器以衰减信号

3.增加距离以减小耦合

4.降低源和/或接收电路的天线效果以减小耦合

5.将接收天线与发射天线垂直放置以减小耦合

6.在接收天线与发射天线之间加屏蔽

7.减小发射及接收天线的阻抗来减小电场耦合

8.增加发射或接收天线之一的阻抗来减小磁场耦合

9.采用一致的、低阻抗参考平面(如同多层PCB板所提供的)耦合信号,使它们保持共模方式

在 具体设计中,如电场或磁场占主导地位,应用方法7和8就可以解决。然而,静电放电一般同时产生电场和磁场,这说明方法7将改善电场的抗扰度,但同时会使磁 场的抗扰度降低。方法8则与方法7带来的效果相反。所以,方法7和8并不是完善的解决方案。不管是电场还是磁场,使用方法1~6与9都会取得一定的效果, 但PCB设计的解决方法主要取决于方法3~6和9的综合使用。

下面详细阐述通过方法3~6和9解决问题的六条实践法则及其原因所在。

一、保持环路面积最小

任意一个电路回路中有变化的磁通量穿过时,将会在环路内感应出电流。电流的大小与磁通量成正比。较小的环路中通过的磁通量也较少,因此感应出的电流也较小, 这就说明环路面积必须最小。应用这一经验的困难之处是如何找到环路。每个人都知道图1中所示的环路,但要正确识别图17中所示的环路则比较困难。

图1、简单的PCB回路

图2、电源线与地线构成的PCB回路

与其试着去找出所有可能的环路,还不如采取下列步骤来减小环路面积:

A、电源线与地线应紧靠在一起以减小电源和地间的环路面积。图18示例说明了电源线与地线同集成电路连接的几种不同方法。

图3、电源与地形成的环路面积的减小

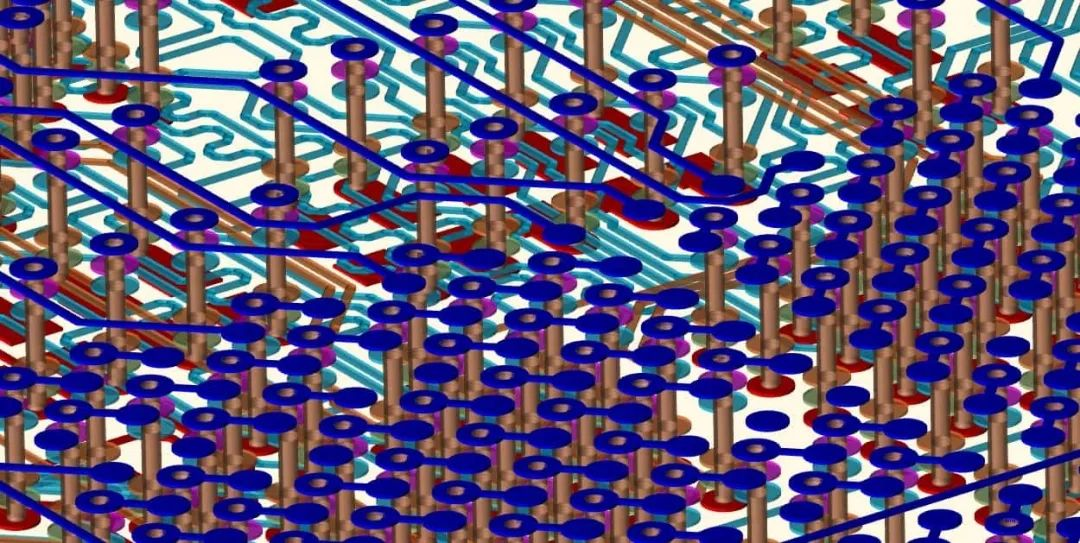

B、多条电源及地线应连接成网格状。图4和图5说明了这一点:在这个典型的PCB设计中,PCB的一面布垂直线,而另一面则布水平线(此图中仅画出地线)。

如 图4所示,这个典型的地线结构会使环路面积很大,可以在双面板上添加一些连接线以减小环路面积,如图5所示。网格构成的环路面积小得多,这将使感应电流很 低,出现问题的可能性也较小。插在底板(或母板)PCB上的PCB板,应该有多个地线和电源线节点,且在连接器长度方向上均匀布置。这将有利于减小整个系 统的环路面积。

图4、典型的PCB地线结构

图5、地线网格

上述步骤A和B既可减小电源与地之间的环路面积,同时也可减小环路天线的效能,下面讲的步骤C和D将降低天线及信号线的效率。

C、并联的导线必须紧紧地放在一起,最好仅使用一条粗导线。图6表明了这一原则。这就是说,地平面不应有大的开口,因为这些开口如同平行导线一般,其作用等同于环路天线。

图6、缩短平行路径

D、信号线应与地线应紧挨着放在一起。在每根信号线的旁边安排一条地线。不过,这也许会产生很多平行地线。为了避免这个问题,如前所述,可采用地平面或地线网格,而不采用单条地线。一个例子如图22所示。在这里,假设由于某种原因信号线不能移动。

图7、信号线与地线紧挨着布线

可在与信号线相对的一面上布置地线面,如图8所示。实际上,将空余PCB部分填以地线面是个好办法。

图8、信号线与地线或地平面的分层布线

E、特别敏感的器件之间的较长的电源线或信号线应每隔一定间隔与地线的位置对调一下。对调的含义是将一根导线从上移到下面,或从左边移到右边,另一根导线则做相反的调整。图24表明了这种方法与减小环路面积的等同效果:对调有关导线后,只有较小的环路存在。

F、在电源线与地线间安装高频旁路电容。因为在静电放电较低的频率段,旁路电容的阻抗较低,在这些频率处,旁路电容能有效减小电源与地间的环路面积。然而,在静电放电较高的频率段,由于寄生电感的影响,即使是高频电容,其作用也很有限。

当然,电源线与地线彼此靠得越近,滤波电容的效果就越不明显。因为环路面积已经足够小了。图9和10说明了这种效果。即使在每个元件旁边都安装旁路电容器,图9中的电路仍有很大的环路面积。

图9、安装旁路电容器的大环路面积

图10、安装旁路电容的小环路面积

图10 中所示的电路,由于将电源线与地线紧挨着放在一起布置,使得环路面积大大减小。然而,即使将电源线与地线并列分布,较长的导线仍会导致较大的环路面积。

二、使导线长度尽量短

天线要具有较高的效率,其长度必须是波长很大的一部分。这就是说,较长的导线将有利于接收静电放电脉冲产生的更多的频率成份;而较短的导线只能接收较少的频率成分。因此,短导线从静电放电产生的电磁场中接收并馈入电路的能量较少。

使导线尽可能短是一个比是环路面积尽量小更容易实现的措施。因为它不象信号环路那样不容易识别,环路面积的尽可能小不可能立即看到,而导线的长短则是很显然的。有关设计步骤如下:

a)使所有元件紧靠在一起,PCB设计人员不应将元件过于分散而占用更多的面积;

b)在相关的元件组,相互之间具有很多互连线的元件应彼此靠得很近。例如,I/O器件是与I/O连接器尽量靠得近些;

c)如有可能的话,从线路板的中心馈送电源或信号,而不要从线路板边缘馈送,如图27所示,中间的馈送信号使大多数元件的连线最短。当线路板为正方形时,这样做的效果最明显,当线路板狭长时,效果则不很明显。但只要可能,还是应该尽量这样做。

前 面提出的PCB设计规则主要针对静电放电电流产生的场效应。但值得注意的是,前面介绍的降低天线效率的方法,这也有助于防止共模噪声转化成会带来更大麻烦 的差模噪声,这在本章开始列出的一般性方法的第9条中已提及过。之所以有这样的效果,是因为前述的各种步骤都有助于减小各种PCB回路的阻抗差异。例如, 规则一中的步骤D特别有用,因为这样处理会使信号线与相关地线的回路阻抗几乎相等。因此,串入到这两条路径中的共模噪声在幅度上也很接近,产生的差模噪声 极小。另外,PCB设计也能采取措施减小由于静电场和电荷注入所带来的问题。下面讲述的规则就与这个问题有关,你会发现有几个规则与前述规则相同。

三、尽可能在PCB上使用完整的地线面(建议采用多层板)

前 面已提到过,地线面有助于减小环路面积,同时也降低了接收天线的效率。地线面作为一个重要的电荷源,可抵消静电放电源上的电荷,这有利于减小静电场带来的 问题。PCB地线面也可作为其对面信号线的屏蔽体(当然,地线面的开口越大,其屏蔽效能就越低)。另外,如果发生放电,由于PCB板的地平面很大,电荷很 容易注入到地线面中,而不是进入到信号线中。这样将有利于对元件进行保护,因为在引起元件损坏前,电荷可以泄放掉。(然而,即使泄放到地的电荷也可能损坏 器件,应采取措施加以避免)

四、加强电源线和地线之间的电容耦合

电源线与地线间的耦合通过两种方式来实现,这在前面已经提到过。

A、使电源线与地线靠得很近,或采用多层PCB板。这将在电源线和地线间产生更多的寄生电容。

B、 在电源线与地线之间接入高频旁路电容(电容组合方式可适用于静电放电频率较低和较高的场合)。电源线与地线间的耦合将有助于减小电荷注入问题。两个物体之 间由各个物体上电荷量的差异造成的电压取决于两者(V=Q/C)间的电容。如果X库仑的电荷注入到电源线中,就会在电源线和地线间产生Y伏的电压。如果电 源线与地线间的电容增加一倍,X库仑的电荷将仅仅产生Y/2伏的电压。当然,这个较小的电压造成损坏的可能性也相应减小。

五、隔离电子元件与静电放电电荷源

在静电放电效应的讨论中,曾指出注入到电子仪器中的电荷可通过隔离来解决。对于PCB设计,这主要指将电子仪器与可能的电荷源隔离开,也与连接器端口或感应电流趋于集中的信号线相隔离。可采取以下两个步骤来进行隔离:

A、使电子元件与PCB走线远离会暴露在静电放电中的PCB部分(例如,操作人员可直接触摸到的地方)。

B、使电子元件和PCB走线远离会暴露在静电放电中的任意一个金属物体(包括螺钉、机架、连接器外壳等)。后一个要求小于下面的设计规则相关联。

六、PCB上的机壳地线的阻抗要低,隔离要好

尽管PCB轨线上的阻焊层有利于隔离PCB走线,但阻焊层可能会导致插针孔发生电弧。

A、隔离机壳地线的最好方法是使之远离电子仪器。另外,如果机壳地线的阻抗很低,静电放电电流易于通过,就不会发生电弧。当然,如此迅速的电荷泄放会产生更强的场,但这比电荷通过电弧直接注入到电路中好得多。

B、机壳地线的长度不能超过其宽度的四或五倍。比这个比例更宽的地线仅能使其阻抗(电感)稍微减小,但是更窄的地线却会使其阻抗大幅度增加。这个长宽比例意味着机壳地线必须很短才行,否则当地线增长时,其宽度要很宽。

设计规则的优先级

至此,关于防止静电放电危害的PCB设计技术的讨论已告一段落。当然,有些时候,这些规则不能全部满足。这时,必须有意识地对一些东西进行取舍。本章开始部分提出三类潜在的静电放电危害可用于确定处理静电放电问题的一般顺序。通常是采用以下顺序来进行考虑:

1、防止电荷注入到系统电路,因为这会造成损坏电路。

2、防止静电放电电流产生的场带来的问题。

3、防止静电场。

所幸的是,这些规则的大部分都是兼容的,在典型的PCB设计中,所有的问题都可以得到很好的解决。

PCB设计指南总结

对于静电放电问题的解决方案,可按以下十二条规则来进行(按优先顺序排列):

1、PCB上的非绝缘机壳地线必须与其他走线相距至少2.2毫米。这适用于连接到机壳地上的所有物体,包括轨线;

2、机壳地线的长度不应超过其宽度的五倍;

3、使未绝缘的电路与操作人员可触摸到的PCB区域或未接地的金属物体相隔至少2厘米以上;

4、电源线与地线要么并排平行地放在PCB的同一层上,要么放在相邻的两层;

5、 地平面和地线必须连成网格状。在任意一个方向上,垂直地线与水平地线至少每隔6厘米连接一次。尤其是双面PCB板,也就是说,PCB板的第一层可以布水平 的地线,而第二层可布垂直的地线,必须至少每隔6厘米放置一个过孔以将两者相连(当然,在小于6厘米的地方进行连接是更好的,地平面比地线网格要好一 些);

6、所有信号线必须在地线面边缘或地线以内13毫米以上。地线既可以布在与信号线相同的层,也可布在与之

紧挨着的层上。如果信号线的长度达到30厘米或其以上,则必须在其旁边放置一根地线,在信号线上方或其

相邻面上放置地线也是可以的;

7、电源线与地线之间跨接的旁路电容器,彼此之间的距离不能大于8厘米(这样每片集成块可能会有多个旁路

电容相连);

8、相互之间连线较多的元件要靠在一起;

9、所有元件必须尽可能靠近I/O连接器(注意,首先应满足第3条);

10、将PCB的空余部分全部填以地线(应注意在每隔6厘米的地方进行连接以产生地线网格);

11、如可能的话,将馈送电源线或信号线从PCB板的边缘中心处引出,而不应从某一个角上引出来。

12、对于特别敏感且较长的信号线(30厘米或更长),应每隔一定间隔与其地线对调。

注意:这些设计规则必须应用到系统内的所有PCB板上(例如主板及插在上面的板卡)。例如,当应用第2条时,机壳地线长度包括母板与子板所有地线的长度之和。

文章知识内容来源于电子工程专辑,如果侵权请联系小编。

关于云创硬见

云创硬见是国内最具特色的电子工程师社区,融合了行业资讯、社群互动、培训学习、活动交流、设计与制造分包等服务,以开放式硬件创新技术交流和培训服务为核心,连接了超过30万工程师和产业链上下游企业,聚焦电子行业的科技创新,聚合最值得关注的产业链资源, 致力于为百万工程师和创新创业型企业打造一站式公共设计与制造服务平台。

-

pcb

+关注

关注

4220文章

22470浏览量

385741 -

电路设计

+关注

关注

6565文章

2316浏览量

195342 -

电源线

+关注

关注

1文章

314浏览量

21253

发布评论请先 登录

相关推荐

云创硬见PCB电路设计指南(经典)

云创硬见PCB电路设计指南(经典)

评论