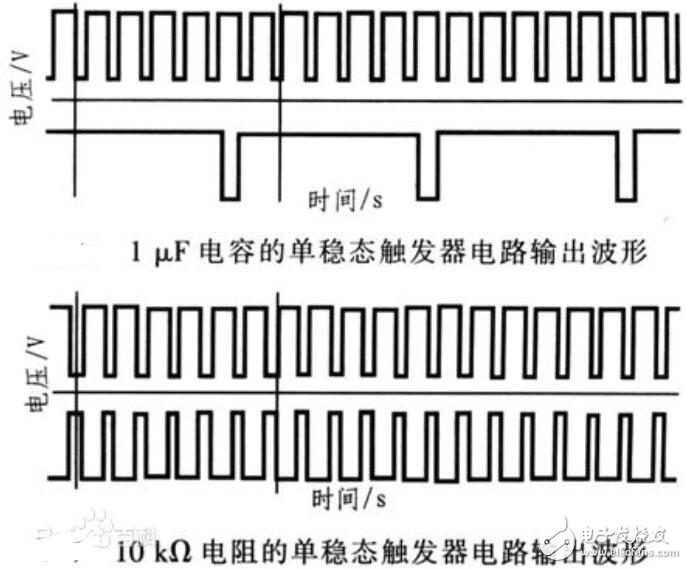

单稳态触发器只有一个稳定状态,一个暂稳态。在外加脉冲的作用下,单稳态触发器可以从一个稳定状态翻转到一个暂稳态。由于电路中RC延时环节的作用,该暂态维持一段时间又回到原来的稳态,暂稳态维持的时间取决于RC的参数值。

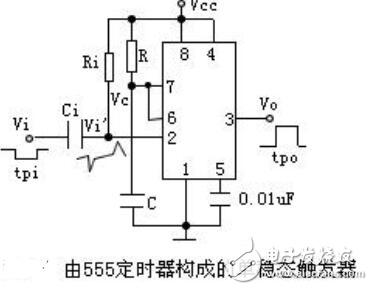

如下图所示,其中R、C为单稳态触发器的定时元件,它们的连接点Vc与定时器的阈值输入端(6脚)及输出端Vo‘(7脚)相连。单稳态触发器输出脉冲宽度tpo=1.1RC。

Ri、Ci构成输入回路的微分环节,用以使输入信号Vi的负脉冲宽度tpi限制在允许的范围内,一般tpi》5RiCi,通过微分环节,可使Vi’的尖脉冲宽度小于单稳态触发器的输出脉冲宽度tpo。若输入信号的负脉冲宽度tpi本来就小于tpo,则微分环节可省略。

定时器复位输入端(4脚)接高电平,控制输入端Vm通过0.01uF接地,定时器输出端Vo(3脚)作为单稳态触发器的单稳信号输出端。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

定时器

+关注

关注

23文章

3147浏览量

112034 -

触发器

+关注

关注

14文章

1677浏览量

60402 -

单稳态触发器

+关注

关注

1文章

44浏览量

23998

发布评论请先 登录

相关推荐

单稳态触发器有几个稳定状态 单稳态触发器的特点

)。它的特点是能够根据输入的触发信号产生一个固定时长的输出脉冲,而输出脉冲宽度与输入触发脉冲的宽度无关。 单稳态触发器通常由一个RC电路、几个

单稳态施密特触发器与多谐振荡器有什么区别?

单稳态施密特触发器与多谐振荡器有什么区别? 单稳态施密特触发器和多谐振荡器是两种在电子领域中常见的电路设计。尽管它们在一些方面有一些相似之处,但它们在原理、功能和应用等方面存在显著的区

d触发器有几个稳态 触发器上升沿下降沿怎么判断

稳态是指触发器在某个特定的输入状态下稳定保持输出的状态。根据触发器的类型和触发方式,触发器分为很多种类,不同类型的

单稳态触发器的工作过程是什么 单稳态触发器的输出状态有哪些

单稳态触发器(Monostable Multivibrator)是一种具有两个稳定状态的逻辑电路,其输出在输入触发信号的边沿触发之后会暂时改变,并在一段时间后返回到初始的稳定状态。本文

什么是单稳态触发电路 单稳态触发电路有哪些特点?有哪些应用

单稳态触发电路(Monostable Multivibrator Circuit)也被称为单稳态多谐振电路或单摇摆电路,是一种产生一次性脉冲信号的电路。它具有稳态和非

单稳态触发器的暂稳态时间与什么有关

单稳态触发器是一种能够在某个时间间隔内将输入信号的电平转换为期望的输出信号电平的数字电路。在单稳态触发器中,暂稳态时间是指当

单稳态触发器暂稳态持续时间误差产生的原因是什么

单稳态触发器是一种基本的数字电路元件,具有两个稳态(稳定状态):稳定低电位(低电平)和稳定高电位(高电平)。当输入信号触发器时,触发器会进入

单稳态触发器的主要用途 单稳态触发器的功能和特点

单稳态触发器(也称为单稳态多谱仪或单稳态稳定器)是一种重要的数字电路元件,用于在输入触发信号的变化时,产生一个确定时间宽度的稳定的输出脉冲。

施密特触发器工作原理 施密特触发器有几个稳态

施密特触发器是一种常用的数字逻辑触发器,具有两个稳态的特点,即激励信号超过一定阈值时触发,且在激励信号低于另一阈值时复位。它由一个比较器和两个正反馈网络组成,具有较高的噪声抑制能力和

单稳态触发器有几个稳定状态

单稳态触发器,又称为单稳态多谱仪,是一种常用的数字电子元件。它具有两个稳定状态:稳定状态1和稳定状态2。 单稳态触发器是由

rs触发器和双稳态触发器的区别

RS触发器是由两个交叉连通的反相器(NOT门)和两个逻辑门组成的,通常是由两个与门(AND门)和一个非门(NOT门)构成。而双稳态触发器(也称为D触发器)是由一对互补输出的锁存器构成,

D触发器与亚稳态的那些事

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D触发器与亚稳态的

FPGA设计的D触发器与亚稳态

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。对于FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D触发器与亚稳态的

单稳态触发器有几个稳态

单稳态触发器有几个稳态

评论