物联网(IoT)等功耗敏感型应用需要在片上系统(SoC)内实现全面的节能策略。仅依靠使用传统断电模式和低电源电压的技术可能不足以实现所需的功率目标。模拟模块通常被认为过于敏感,并且与积极的电源管理技术不兼容。

然而,很好地理解模拟模块的特性可以实现低功耗SoC设计。在本文中,我们将详细介绍在通用物联网SoC设计中与外部传感器接口的模数转换器(ADC)IP,并描述其可在系统级利用以实现低功耗的相关特性。

可能使用纽扣电池或能量收集的物联网应用正在推动非常低的要求功耗SoC设计遍及整个行业。为了在不更换电池的情况下长时间维持运行,设计人员必须充分利用可用的功率降低技术。

传统方法依赖于降低SoC的电源电压和更精细的电源电压。几何过程'较小的特征尺寸,以减少有功功率。这种方法会增加系统成本,并可能导致更高的泄漏功率。

在系统级,可以通过识别芯片中可以在某些操作时关闭电源的模块来实现低功耗技术。被执行。还可以将时钟速率和电源电平调整到维持所需操作性能的最小值,从而节省额外的功率。

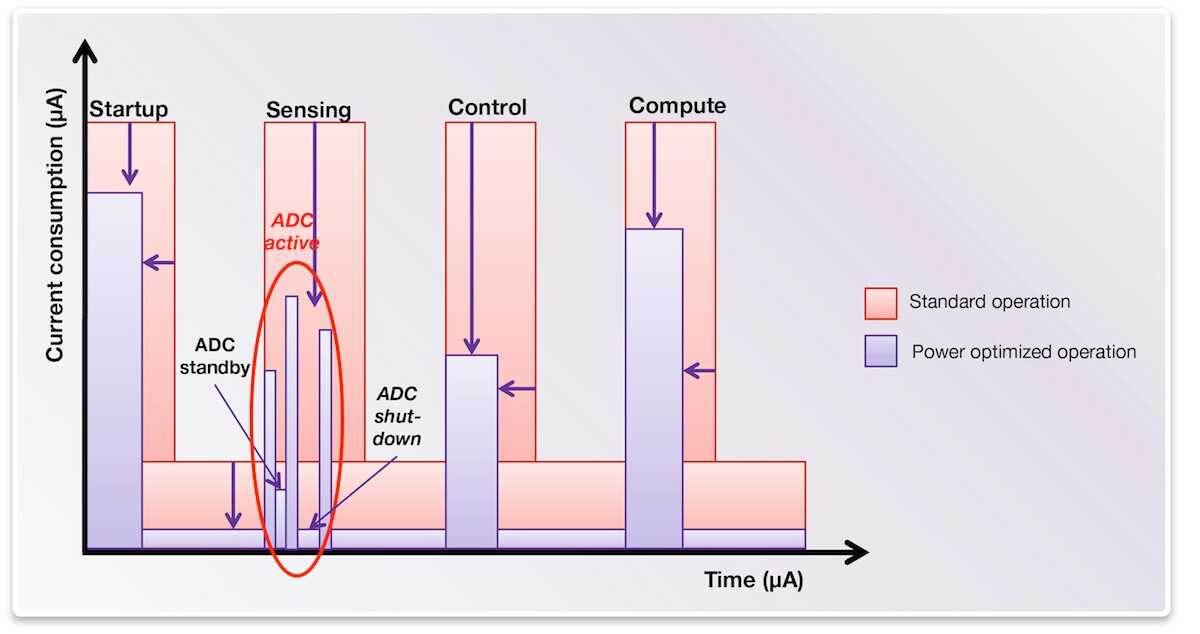

IoT SoC的典型活动配置文件的特点是占空比非常短:大部分电路经常处于空闲模式;只有一小部分电路始终处于活动状态,以便扫描环境并在需要时激活剩余的电路。 (图1)。始终有效的电路放置在专用电源岛上,使用高Vth器件甚至厚氧化物器件,以最大限度地降低漏电功率。剩下的电路可以从电源关闭,以限制其泄漏。

图1:常见的物联网使用情况

语音激活设备就是这种应用的一个例子,其中只有简单的语音检测电路始终处于活动状态,并且只有当语音检测电路识别出一个时,才会激活专用于命令识别和处理的块。潜在的命令。另一个例子是定期汇集传感器以确定环境中的某些变化是否需要采取措施。

因此,现代物联网SoC设计实现了具有多种省电模式和电路详细分区的复杂电源管理架构为了进一步降低有源和漏电功耗而进入单独的电源岛。

针对当今物联网SoC设计的新型低功耗技术

然而,当它出现时来到模拟接口,传统的低功耗技术无法直接应用。通常需要模拟模块来处理具有大电压摆幅和高线性度要求的信号。这限制了降低电源电平的能力,从而限制了有效的最小特征尺寸。

模拟模块具有内部偏置电流和电压,需要正确稳定以获得最佳性能,因此上电和断电时间本身就是如此缓慢,限制了将电源模式更改为接口长时间不使用的能力。此外,它们有时由通过慢速串行总线控制的外部设备制造,这导致实时主动控制其电源状态的能力有限。

设计人员需要一种新的方法来克服这些限制,特别是在设计功耗敏感的应用时。与传感器接口的ADC集成不仅可以降低外部材料清单(BOM)成本,还可以将模拟接口更紧密地集成到SoC的电源管理架构中,从而实现更快的上电和断电转换以及额外的功耗节省。为了降低BoM成本和功耗,设计人员必须选择一个足够灵活的集成ADC,以最小的功耗支持不同的工作模式,并且可以在不同的功耗模式之间快速改变。集成ADC的主要特点是:

最小的静态功耗,随着速度的降低,功耗降至最低

多种性能模式,在性能设置降低时功耗最小化

多个

具体用例

设计师必须了解所有的功能模式,能够快速更改它们而不会失去准确性/性能ADC的功能以及如何在特定用例中使用它们以实现额外的功耗节省。以下是几个用例的示例。

1-非常慢的采集

此示例考虑系统的情况数据处理需要一定的时钟速度才能达到所需的处理吞吐量,但传感器信息可能只需要以低得多的速率更新。

此用例的传统实现是划分处理器时钟匹配传感器采样所需的低速率。但是,此时钟速率可能低于ADC可靠支持的最小值 - 或者,ADC的时钟频率更高,但在某些时间段内保持空闲(待机)。

理想情况下选项是在这些空闲时段内完全关闭ADC,并快速将其唤醒以用于下一个传感器采样。在这种模式下,ADC主要消耗泄漏功率,并且仅在短暂的有效采样瞬间消耗有功功率。这有效地将功耗的缩放扩展到远低于最小支持时钟速率,而不会影响SoC的配置(例如,遵守数据处理所需的时钟速度)。

此选项依赖于以下ADC功能:

快速关闭和上电步骤(在这些步骤中应避免任何缓慢的过程,例如校准)

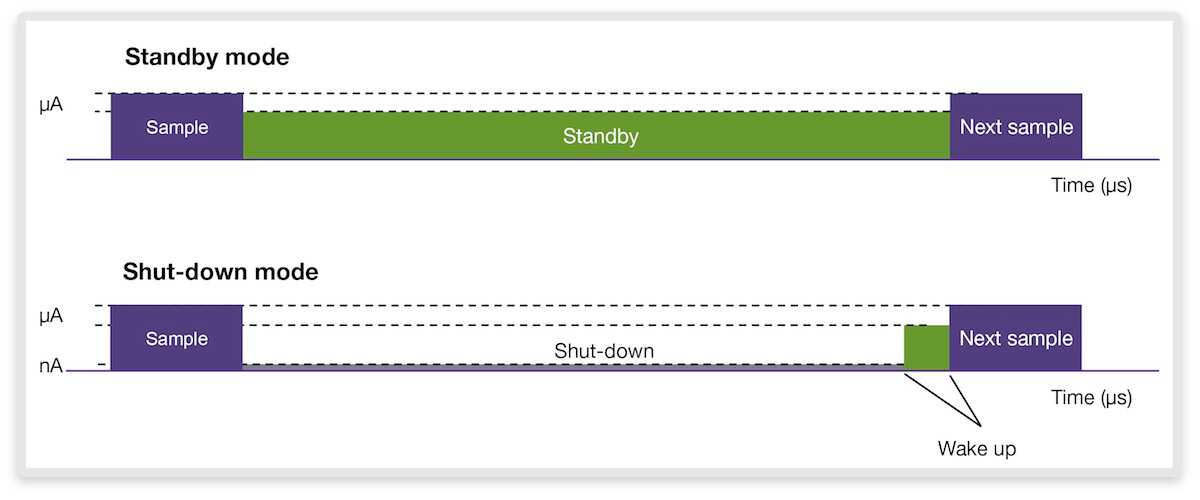

关闭时泄漏功率极低模式,例如将电源管理功能集成到ADC中(电源开关,低压差(LDO)等)。由于不同功率模式之间的转换而导致的额外功耗应该是最小的。 (图2)

图2:待机与关机模式下的低功耗

性能可重复性。偏移和绝对精度等性能参数需要在连续的功率周期内保持一致。转换结果的稳定性可以使用“有效分辨率”(Reff)度量来衡量,该度量是从固定输入的ADC输出直方图获得的,使用多个功率周期的大量测量结果构建。 (图3)。较窄的分布(左侧)是更好的稳定性(和更低的噪音)的证据。多个峰值(右侧)的分布或复苏的放大表明稳定性差。

图3 :ADC的有效分辨率直方图

2-与内部处理器和电源的紧密耦合管理系统

该示例考虑了集成ADC与处理器寄存器紧密耦合的情况,从而将ADC控制映射到处理器的内部寄存器,从而避免了控制ADC的需要通过复杂的总线协议,每个读/写操作通常需要几个时钟周期。该技术通过避免控制外部ADC可能需要的多个时钟周期,使系统能够快速进入低功耗模式。如果ADC经常受到上电/下电周期的影响,这种技术尤其有用。

此外,跨越模拟和数字域的控制环路的环路延迟会降低,从而可能提高控制环路的性能。

此技术依赖于以下ADC功能:

能够将ADC控制映射到内部处理器寄存器或直接映射到AMBA结构,从而避免周期和电源等待周期

能够在SoC电源管理系统中集成ADC电源管理功能(内部电源岛等)

3-性能缩放

此示例考虑了某个传感器读数所需的精度可能因系统状态而异的情况。例如,较低的准确度可以是可接受的,而图像传感器没有检测到任何活动。但是,当检测到活动时,准确度可能需要更高。

这些知识可用于降低功耗:数据采集速度和ADC性能水平可在非活动期间降低,仅在需要更高的精度。

该技术依赖于以下ADC功能:

具有相应节能的分辨率控制

动态采样率控制和比例采样率下的功耗

4-高输出阻抗传感器

这个例子考虑了使用开关电容技术实现的现代ADC的情况。为了简化电路分析,这些ADC的前端采样级可以简化为电容器(采样元件)和非线性电阻器(开关)。传感器本身可以简化为电压源和串联电阻(输出阻抗)。 (图4)。

图4:简化的ADC输入电路和传感器原理图

当电路闭合时,传感器用作加载采样电容的源,其时间常数为τ= RC。如果传感器输出阻抗很大,那么时间常数也很大,可能无法让采样电容上的电压有足够的时间以所需精度稳定下来。

避免这种限制的一种方法是在传感器和ADC之间插入一个低输出阻抗的缓冲器。然而,由于缓冲器本身的功率,这种解决方案会导致相当大的功率损失。

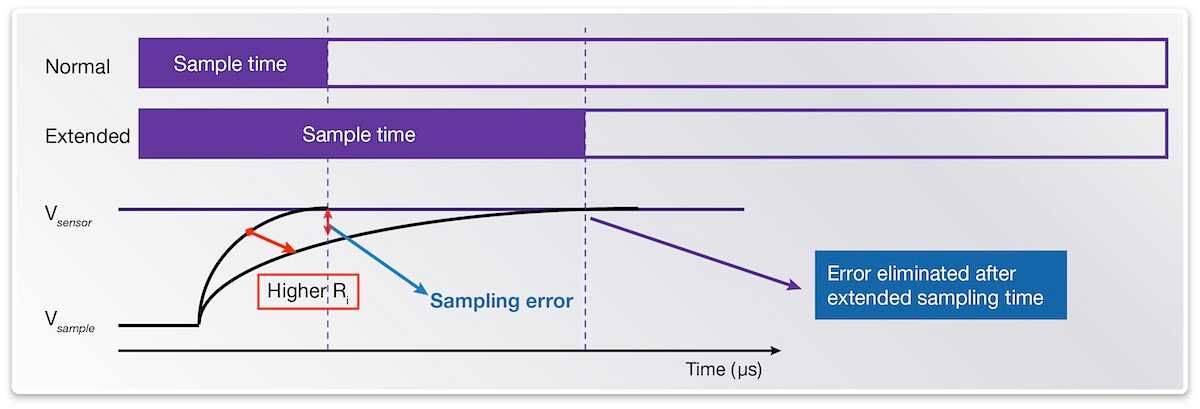

理想的解决方案是延长ADC采样时间以适应所需的建立时间。结果,不需要缓冲器并且降低了功耗。 (图5)。

此技术依赖于以下ADC功能:

可编程采样时间,可根据传感器确定的稳定要求进行调整,扩展用于高阻抗传感器(避免额外缓冲)或降低低阻抗传感器(允许ADC更早关闭 - 或开始新的转换周期)

图5:延长采样时间以适应高阻抗传感器

摘要

了解模拟接口特性和使用案例可以帮助设计人员大幅降低物联网SoC设计的功耗。

通过集成与传感器接口的ADC,可以节省功耗。集成ADC具有最小的静态功耗,可在速度降低时最大限度地降低功耗;多种性能模式,在性能设置降低时功耗最小化;多种功耗模式,能够快速更改它们而不会降低精度和性能。

-

低功耗

+关注

关注

9文章

2226浏览量

102656 -

PCB打样

+关注

关注

17文章

2965浏览量

21383 -

华强PCB

+关注

关注

8文章

1831浏览量

27460 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

42574

发布评论请先 登录

相关推荐

传统低功耗技术面临的挑战

传统低功耗技术面临的挑战

评论