Stateflow 是一个基于状态机和流程图来构建组合和时序逻辑决策模型并进行仿真的环境。Stateflow 可以将图形表示和表格表示(包括状态转换图、流程图、状态转换表和真值表)结合在一起,针对系统对事件、基于时间的条件以及外部输入信号的反应方式进行建模。

Stateflow 可用于设计有关监控、任务调度以及故障管理应用程序的逻辑。Stateflow 包括状态图动画及静态和运行时检查,可以在实施前测试设计的一致性和完整性。

主要功能

构建环境、图形组件和仿真引擎模型,实现复杂逻辑的建模和仿真;

具有层次结构、并行系统、时间算子和事件的确定性执行语义;

通过状态图、状态转移表和状态转移矩阵表达有限状态机;

通过状态图动画、状态活动记录、数据记录和集成调试,分析设计和检测运行时错误;

对于周期问题的静态和运行时检查,状态不一致、数据范围冲突及溢出情况等;

Mealy 和 Moore 有限状态机。

逻辑设计

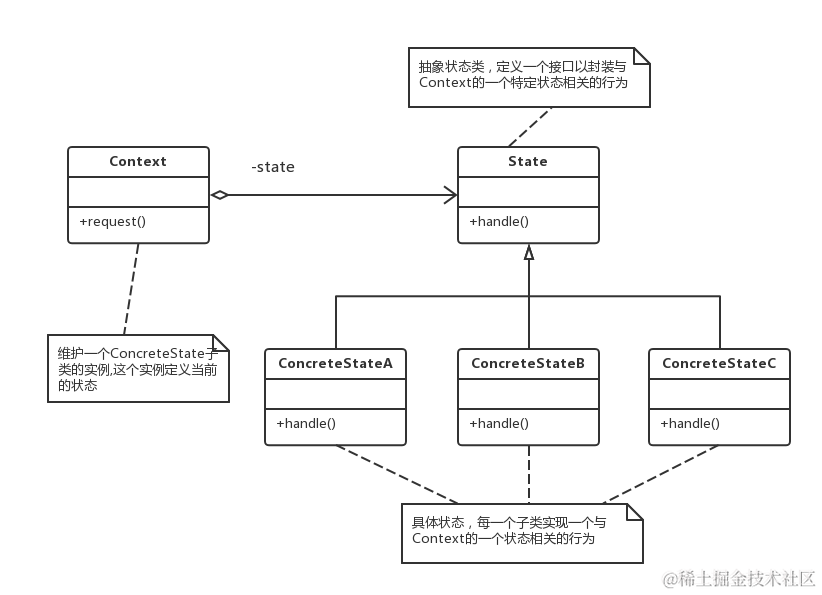

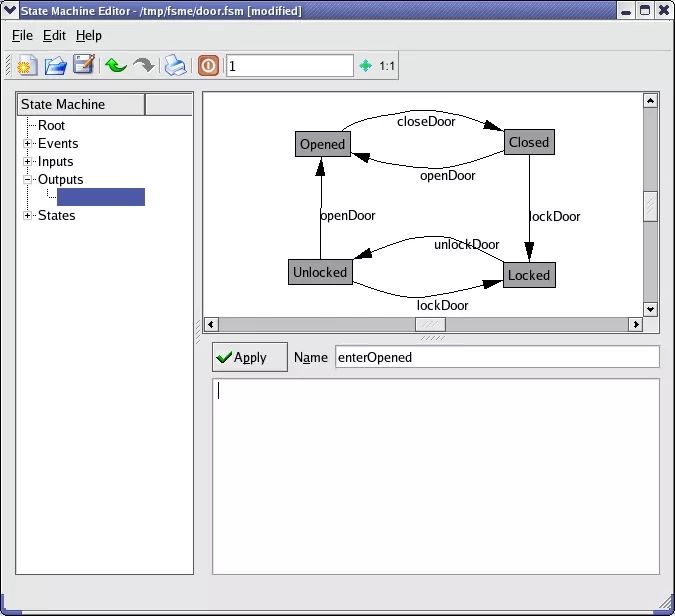

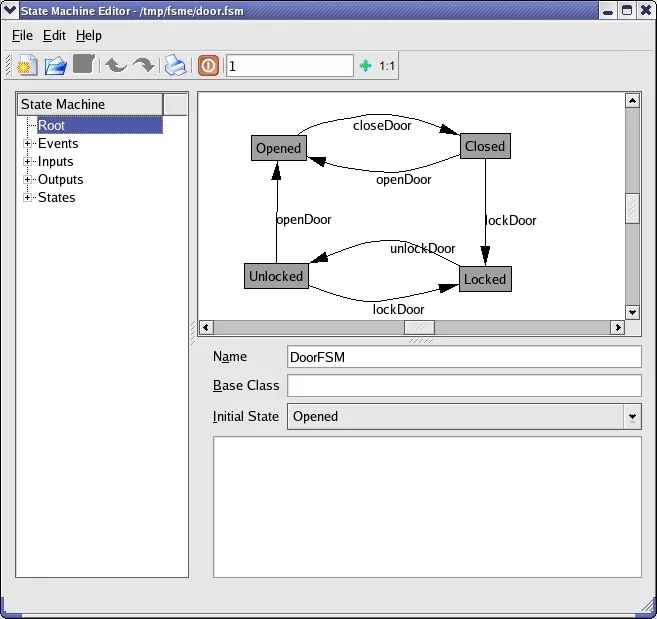

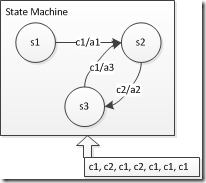

Stateflow提供图形和表格接口,以使用状态机来进行系统逻辑建模。在状态机中,可以将系统运作模式构建为状态模型,通过转移和结点来表达模式间的切换逻辑。系统中的不同组件可以构建为状态模型,能够单独执行或并行执行。Stateflow 通过分层组织状态图对象、函数和组件来管理设计的复杂程度。

在 Stateflow 中,既可以使用流程图以图形方式,也可以使用真值表以表格格式,表达组合逻辑。

逻辑设计包括定义待检查的条件以及所要执行的后续操作。Stateflow 可以使用 C 或 MATLAB 定义条件和操作。您可以通过 Simulink 模型浏览器来管理条件和操作中所用的数据。您可以在执行设计前借助 Stateflow 得知可能存在的状态不一致现象、未使用的数据和事件以及无效的转移。

这是一个定义锅炉温度控制系统逻辑的 Stateflow 图。该图使用图形函数(右侧)实现加热器系统(左侧)所调用的公用程序算法。

以图形方式设计逻辑

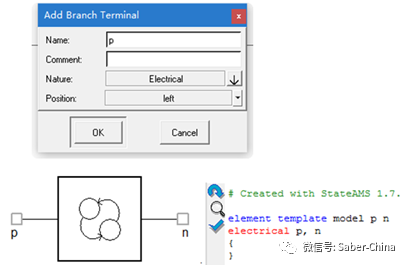

Stateflow提供一个编辑器和一些用于绘制状态机和流程图的图形对象。通过从图形调色板中选择状态、转移和结点,然后将其拖入Stateflow编辑器,即可构建状态机。您也可以使用流程图批注、Simulink 子系统、MATLAB 和真值表创建函数。Stateflow图可以指定为具有扩展功能的 Mealy 和 Moore 混合状态机、Mealy 状态机或 Moore 状态机。

通过绘制由结点连接的转移,可以创建流程图,并根据条件逻辑予以执行。使用“Pattern模式向导”,可以创建常用的逻辑流模式。流程图可以放在图形函数中,既能用在该状态图的许多位置上,也可以用于同一模型的其他状态图中。使用流程图可以设计逻辑,由此在各状态间进行转移。

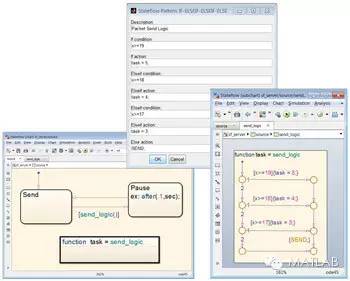

Stateflow 图(左)使用通过“模式向导”(中)生成的图形函数(右)。

Stateflow编辑器可提供编辑时检查,以识别对象的非法位置以及无效转移。

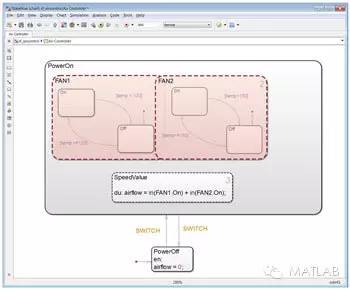

Stateflow 编辑器正在处理一个冷却系统的模型。边界发生交叠的状态以红色突出显示。

以图形方式设计逻辑

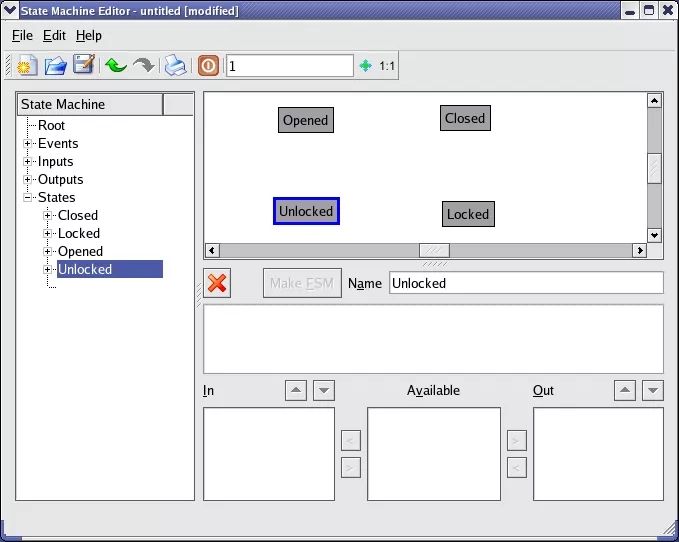

Stateflow中的状态转移表为状态机建模提供了一个结构化环境。通过添加状态行和状态间转移列,可以构建状态机。状态转移表通过提供状态名称下拉菜单、自动完成有限状态机语法和其他编辑时检查,可以帮助您创建状态机。您可以在执行模型前运行静态诊断测试,以检测语法错误、未完成的转移和无法达到的状态。

从状态转移表生成的状态转移矩阵视图有助于快速识别来自特定状态的条件和可能的目标状态。

Stateflow 中的真值表可用于对不需要通过连续运行来维护状态的逻辑建模。输入要检查的条件,然后合并这些条件产生的结果,即可构建真值表。之后,可输入关于对不同的结果组合的操作。构建真值表后,可以运行静态诊断检查,以识别过度指定的条件和指定不足的条件。

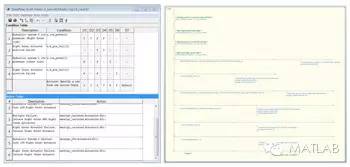

左:用于实施在故障检测算法中选择有效传感器读数的逻辑的真值表。

右:自动生成的真值表图形表示形式。

组件集成与算法调度

您可以将在 Stateflow 中创建组件的与其他组件相集成,从而构建状态机算法。Stateflow 组件可以包含 MATLAB 和 Simulink 函数、自定义 C 代码、图形函数和真值表。在所构建的算法中,可以使用基于时间和基于条件的逻辑来调度组件和函数的执行。

每个 Stateflow 组件都可以独立开发、执行和验证,从而使多个用户能够同时处理算法的不同部分。

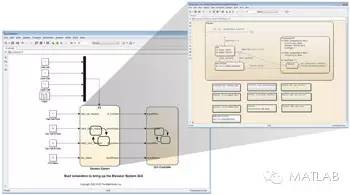

Simulink 模型(左)合并了一个 Stateflow 图(右)。Stateflow 图对升降舵所用的逻辑进行建模,其中包括图形函数、MATLAB 函数和真值表。

将组件集成到设计中

右键单击组件,将其转换为原子子图,并放入库中,即可跨图、跨模型重复使用该组件。要使用该组件,可以将其从库中拖出,然后放入状态图或模型中。当更新库中的某个组件时,该组件的所有实例将自动更新。您可以分层组织组件和函数,以便简明而准确地表达您的系统。

调度算法

在 Stateflow 中,可对条件逻辑和基于时间的逻辑建模,以调用 Simulink 函数和 MATLAB 函数。在 Stateflow 中,根据逻辑建模的事件可以输出到 Simulink,以激活对函数调用或控制信号变化做出反应的子系统。

Stateflow 提供基于事件和基于时间的算子(before、after、at 和 every),以便于您根据事件计数和经过的时间来指定状态转移逻辑,而无需使用计时器和计数器。

模型仿真与结果分析

通过模型仿真,可以分析系统的行为。通过从任何保存的状态重新开始仿真,并分析其对不同设置和配置的反应,可以运行条件假设场景。

模型仿真

在 Stateflow 中,通过使用状态图动画突出显示模型中的活动状态和转移,可以实现系统仿真行为可视化。

Stateflow 的调试能力使您得以详细地对仿真进行逐步调试。您可以设置断点,监视数据值,并逐步调试状态图中的不同函数。您可以通过 Stateflow 调试器窗口来控制仿真的执行情况,显示状态图的调用堆栈以及执行状态。

Stateflow 调试器可检测运行时错误,其中包括状态不一致、数据范围冲突以及可能的无限循环。

分析结果

在仿真过程中,可通过以下方式实现仿真结果可视化:

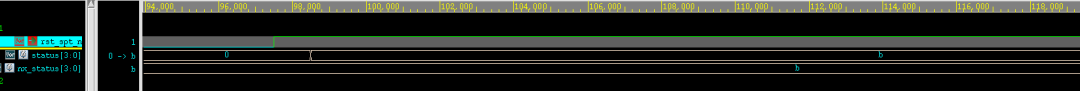

使用 Simulink 显示器和示波器查看状态和数据

在 Simulation Data Inspector (仿真数据检查器)中查看记录的数据

使用 MATLAB 构建自定义显示器

再者,您可以记录状态图和状态活动数据,以便在 MATLAB 中进行后处理。

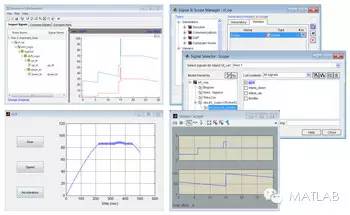

Stateflow 中的仿真数据可视化选项。

左上:Simulink Data Inspector(Simulink 数据检查器)用于比较特定信号;

左下:自定义 MATLAB 界面用于分析数据;

右:Simulink Signal Selector(Simulink 信号选择器)用于比较状态。

设计验证与代码生成

通过将 Stateflow 与其他 Simulink 产品配合使用,可以根据需求验证您的设计,并生成代码以便在嵌入式系统中予以实现。

使用 Simulink Verification and Validation(Simulink 检验和验证),可以将需求直接映射到 Stateflow 对象,检查是否符合标准,并收集模型覆盖度量信息。

使用 Simulink Design Verifier(Simulink 设计检验器),可以检测设计错误,针对采用常规方法难以发现的错误生成测试向量。

-

显示器

+关注

关注

21文章

4737浏览量

137854 -

可视化

+关注

关注

1文章

1020浏览量

20554 -

结构化

+关注

关注

0文章

26浏览量

10264

发布评论请先 登录

相关推荐

什么是有限状态机?如何解决传统有限状态机「状态爆炸」问题?

Verilog状态机+设计实例

嵌入式软件设计之状态机编程开发方案

什么是状态机?状态机的种类与实现

自动生成程序状态机代码状态机建模方法

基于C语言的状态机实现方案

基于FPGA的状态机设计

关于使用状态机与流程图进行建模和仿真决策逻辑的分析和研究

关于使用状态机与流程图进行建模和仿真决策逻辑的分析和研究

评论