HDL Coder 利用 MATLAB 函数、Simulink 模型和 Stateflow 图生成可移植、可综合的 Verilog 和 VHDL 代码。生成的 HDL 代码可用于 FPGA 编程或 ASIC 原型开发和设计。

HDL Coder 提供了一个 Workflow Advisor,可以自动执行 Xilinx 和 Altera FPGA 编程。您可以控制 HDL 架构和实施、突出显示关键路径,并估算硬件资源利用率。HDL Coder 在 Simulink 模型与生成的 Verilog 和 VHDL 代码之间提供了可追溯性,使高完整性应用程序的代码验证遵守 DO-254 和其他标准。

主要特性

独立于目标的、可综合的 VHDL 和 Verilog 代码

代码生成支持MATLAB 函数、系统对象以及 Simulink 模块

使用 Stateflow 实施 Mealy 和 Moore 有限状态机以及控制逻辑

用于 Xilinx 和 Altera 应用程序面板编程的 Workflow Advisor

资源共享和重定时,用以平衡面积速度

符合 DO-254 的代码到模型和模型到代码可追溯性

旧有代码集成

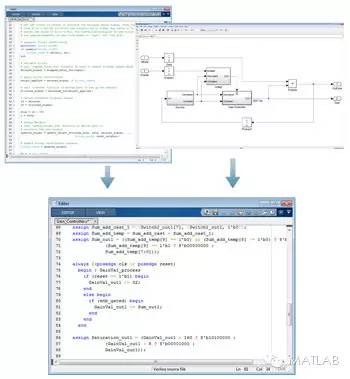

使用 HDL Coder 从 MATLAB 或 Simulink 生成 HDL 代码。您可以使用 MATLAB 函数、Simulink 模型或将两者结合使用来生成可综合的 VHDL 和 Verilog 代码。

主要功能

1.生成HDL代码

使用 HDL Coder,只需几个步骤便可为 FPGA 和 ASIC 实施生成可综合的 HDL 代码:

将 MATLAB 代码、Simulink 模块和 Stateflow 图组合使用,进行设计建模。

优化模型以满足面积速度设计目标。

使用为 MATLAB 和 Simulink 集成的 HDL Workflow Advisor 生成 HDL 代码。

使用 HDL Verifier 验证生成的代码。

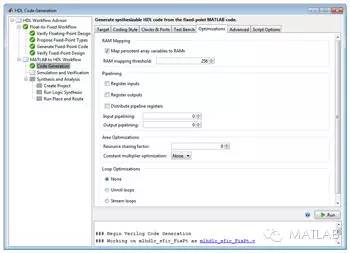

2.优化 HDL 代码

在 MATLAB 或 Simulink 中,通过采用分布式流水线、流式处理和资源共享,可以优化 HDL 代码以实现速度面积目标。在 MATLAB 中,您可以使用高级循环优化,如循环流和循环展开,用于包含 for 循环或矩阵运算的 MATLAB 设计。您可以将 MATLAB 代码中的持续阵列或矩阵变量映射到 Block RAM。在 Simulink 中,您可以实施信号处理和多媒体应用中常用的多声道设计和序列化技术。

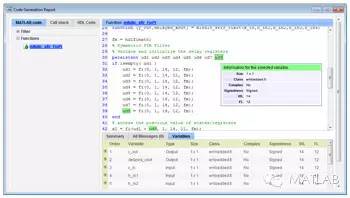

适用于 MATLAB 的 HDL Workflow Advisor 提供了多个优化选项,如 RAM 映射、流水线、资源共享和循环展开

面积速度优化。用一个乘法器取代四个乘法器,降低了设计面积成本,数据率提升4倍。

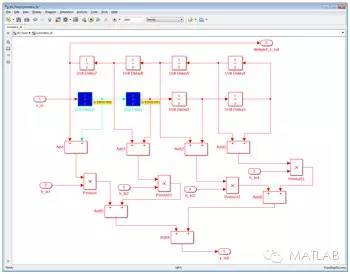

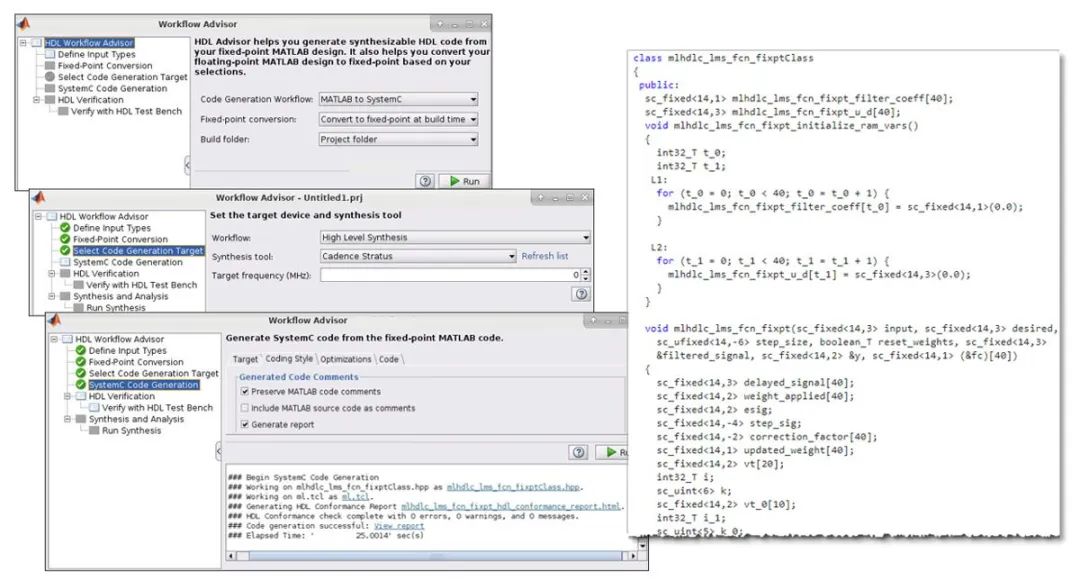

3. FPGA 设计自动化

HDL 中的 HDL Workflow Advisor 可以自动执行将 MATLAB 算法和 Simulink 模型实施到 Xilinx 和 Altera FPGA 的工作流程。HDL Workflow Advisor 集成了 FPGA 设计流程的所有步骤,包括:

检查 Simulink 模型的 HDL 代码生成兼容性

生成 HDL 代码、HDL 测试工作台和协同仿真模型

通过与 Xilinx ISE 和 Altera Quartus II 集成,执行合成和时序分析

估算设计中的资源使用

使用关键路径时序回注 Simulink 模型

使用关键路径时序回注 Simulink 模型。HDL Workflow Advisor 会在 Simulink 中突出显示关键路径时序,以帮助识别速度瓶颈并提高设计性能。

您可以查看合成后时序报告并回注 Simulink 模型,以识别时序约束瓶颈。与合成工具的这一集成实现了快速设计迭代,并显著缩短了 FPGA 设计周期时间。

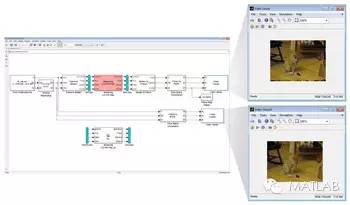

4.验证 HDL 代码

HDL Coder 可以生成 VHDL 和 Verilog 测试工作台以快速验证生成的 HDL 代码。您可以使用各种选项自定义 HDL 测试工作台,测试HDL 代码。您还可以生成脚本文件,在 HDL 仿真器中自动处理代码编译和仿真。

HDL Coder 与 HDL Verifier 配套使用,可以自动生成两类协同仿真模型:

HDL 协同仿真模型,用于使用 Simulink 和 HDL 仿真器(如 Cadence Incisive 或 Mentor Graphics ModelSim 和 Questa)执行 HDL 协同仿真

FPGA 在环 (FIL) 协同仿真模型,用于使用 Simulink 和 FPGA 板验证设计

自动生成 FPGA 在环 (FIL) 模型,用于视频锐化。FIL 仿真可以在硬件上高效地执行设计空间探查。

5. 记录和追踪HDL 代码

HDL Coder 会将生成的代码记录在 HTML 报告中,该报告包括带超链接 的HDL 代码和生成的 HDL 文件表。通过 HDL 代码中的超链接,可以导航到与代码对应的 MATLAB 算法或 Simulink 模块。

为满足 DO-254 等标准对高完整性应用程序的代码可追溯性要求,HDL Coder 让您能够执行以下操作:

从生成的 HDL 代码导航到 MATLAB 代码

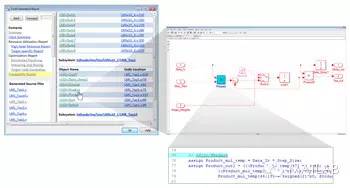

在 Simulink 模块与生成的 HDL 代码之间导航,实现双向追踪

插入用户注释和描述,增加代码可读性

MATLAB 中的代码生成报告,使您可以从生成的 VHDL 和 Verilog 代码导航到 MATLAB 代码。

将 Simulink Verification and Validation 与 HDL Coder 搭配使用,可以将系统需求作为注释嵌入到从 Simulink 或 Stateflow 生成的 HDL 代码中。这样,您便可以使整个工作流程完全透明,包括从系统需求到生成的 HDL 代码。

Simulink 中的 HDL 代码生成报告,使您可以在模型与生成的 HDL 代码之间导航。

6.HDL 编码标准

用于工业 FPGA 和 ASIC 应用(如航空航天工业中的 DO-254)的开发过程可能建议使用特定的 RTL 编码指南。HDL Coder 旨在生成满足通用行业编码指南(如 RMM 和 STARC)的 VHDL 和 Verilog 代码。HDL Coder 还可生成报告,帮助您确定 Simulink 模型和 MATLAB 代码中不合适的结构,这样您可以调整您的模型,使生成的 RTL 符合这些编码指南。

HDL Coder 还可以生成第三方 lint 工具脚本,用于检查您生成的 HDL 代码。HDL Coder 自动生成的代码可通过多种行业标准的 lint 工具的检查,例如Atrenta SpyGlass, Real Intent Ascent Lint, Synopsys Leda, 和 Mentor Graphics HDL Designer。HDL Coder 可生成允许与任何 lint 工具集成的自定义脚本。

使用 HDL Coder 生成的代码遵循 RTL 编码原则,通过:

避免 FSM 状态可访问性和编码问题

避免仿真和综合语义之间的差异

避免在实现代价高昂的操作

避免下游工具流问题

遵循命名规则和RTL编码习惯

强 RTL 建模的清晰度并降低复杂性

增强对时钟资源(时钟、启用、复位)和控制信号的检查

支持代码的可测性和可追溯性

-

编码

+关注

关注

6文章

835浏览量

54457 -

代码

+关注

关注

30文章

4555浏览量

66748 -

脚本

+关注

关注

1文章

372浏览量

14632

发布评论请先 登录

相关推荐

基于FPGA设计频率计方案介绍分享

# FPGA 编程如何工作?

值得多看的FPGA 学习路线

FPGA的Verilog代码编写规范

FPGA和ASIC的优劣势 FPGA和ASIC的应用场景及前景

关于FPGA的学习和发展问题

什么是ASIC设计?使用HDL和SystemC代码生成进行ASIC设计

Verilog代码封装后门访问

关于为FPGA和ASIC生成Verilog和VHDL代码分析和应用介绍

关于为FPGA和ASIC生成Verilog和VHDL代码分析和应用介绍

评论