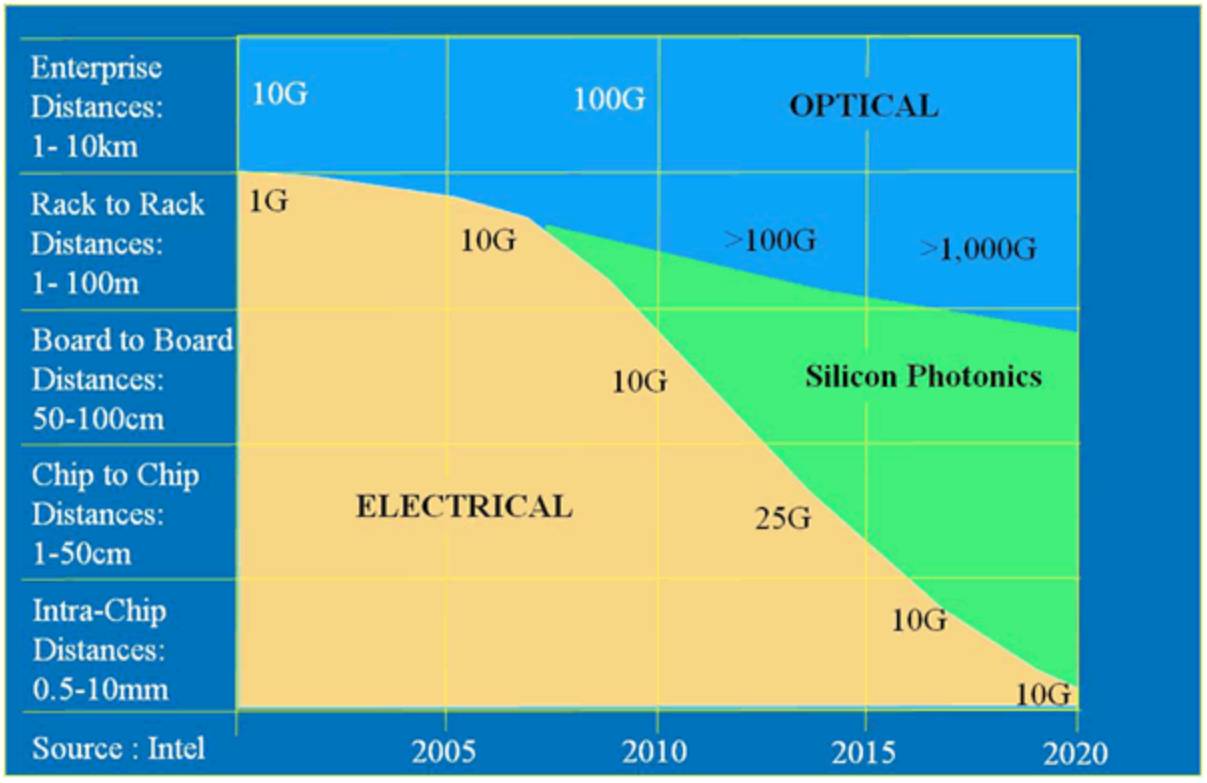

在过去,光纤通信被用于长途通信(50公里及以上)。全世界只需要有限数量的高端接口产品就能满足。然而,随着运营大型数据中心(脸谱网、谷歌、Amazon、……)的崛起,这些公司喜欢取代服务器机架之间的传统布线。基于铜线的方法被认为是进一步提高数据传输能力的瓶颈, 因此光通信可以极大地提高服务器之间的带宽,降低复杂度、功耗和成本。

Reducing cost and power while increasing bandwidth

提高带宽的同时降低成本和功耗

Thus, the optical interconnect suppliers now need to produce a large number of their products. To reduce the cost, they separate the optical parts (laser diodes, photo detectors) from the digital controller circuits. For the electrical ICs regular CMOS technology can be used for mass-production. Moreover, there were several breakthroughs in the last decade, where conventional CMOS processing steps can now be used to create all kinds of optical components like WDM (Wavelength Division Multiplexers), lasers, detectors, waveguides in SOI processes…

光互连供应商在生产大量的产品中,为了降低成本,他们将光学部件(激光二极管、光探测器)从数字控制器电路中分离出来。对于电气集成电路,常规CMOS技术可用于大规模生产。此外,在过去的十年中,有了一些突破,传统的CMOS处理步骤现在可以用来制造各种各样的光学元件,如SOI(波分复用器)、激光器、探测器和SOI工艺中的波导…

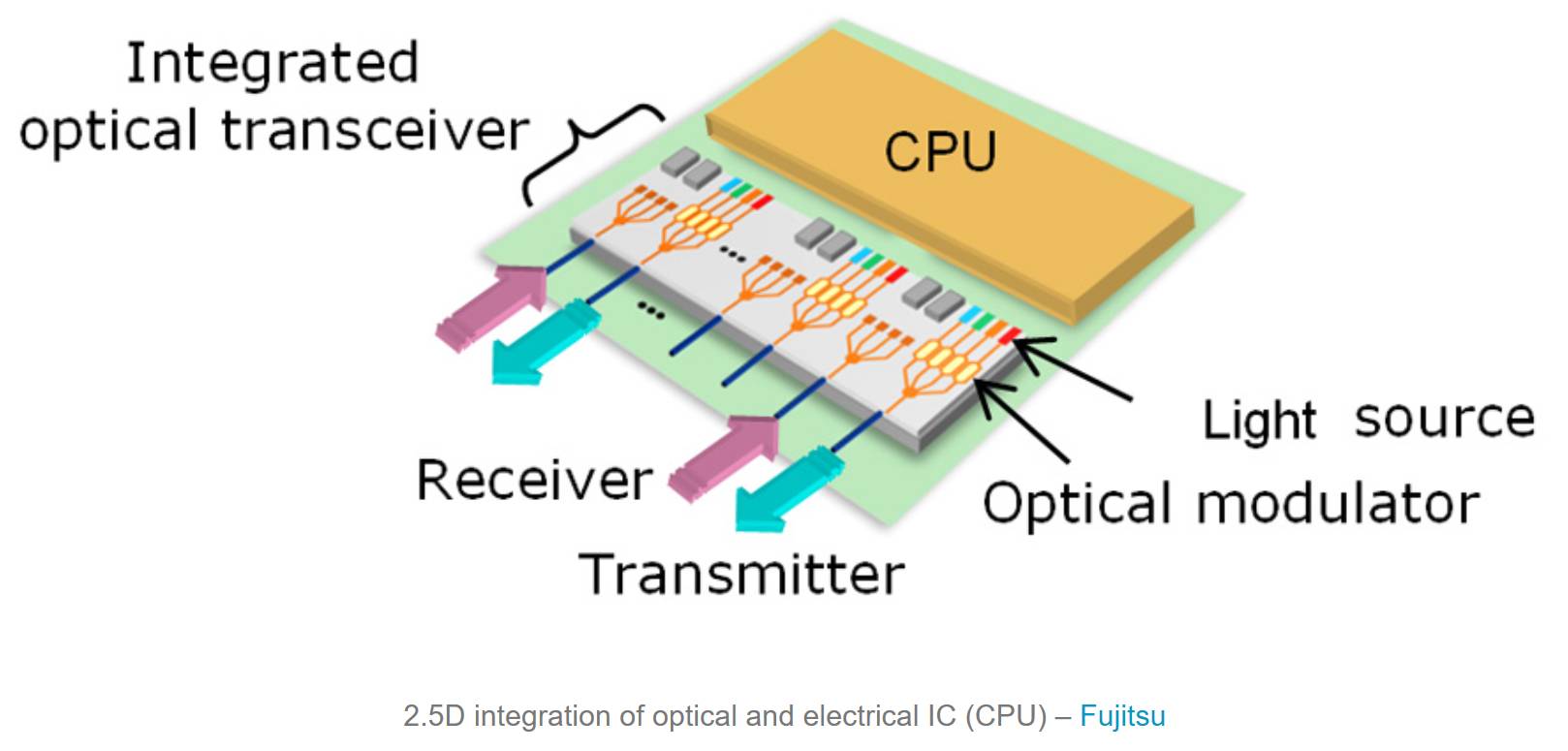

混合2.5D和3D集成

Both optical and electrical elements are then combined within a single IC package using advanced packing techniques like 2.5D (electronic interposer) and 3D (flip-chip) integration. The hybrid integration allows designers to select the best process option for each function. E.g. the digital functions can be integrated in high end CMOS technology with high performance and smaller size. The photonic die does not benefit from this minimum feature size and can thus be designed in a more mature SOI technology which significantly reduces the total cost

光学和电气元件相结合,一个单一的IC封装,采用先进的包装技术2.5D(Interposer)和三维(flip-chip)集成。混合集成允许设计者为每个功能选择最佳的工艺选项。数字功能可以集成在高性能、更小尺寸的高端CMOS技术中。光子裸片并不需要从这个最小特征尺寸中获益,反而可以在更成熟的SOI技术中进行设计,从而显著降低总成本。

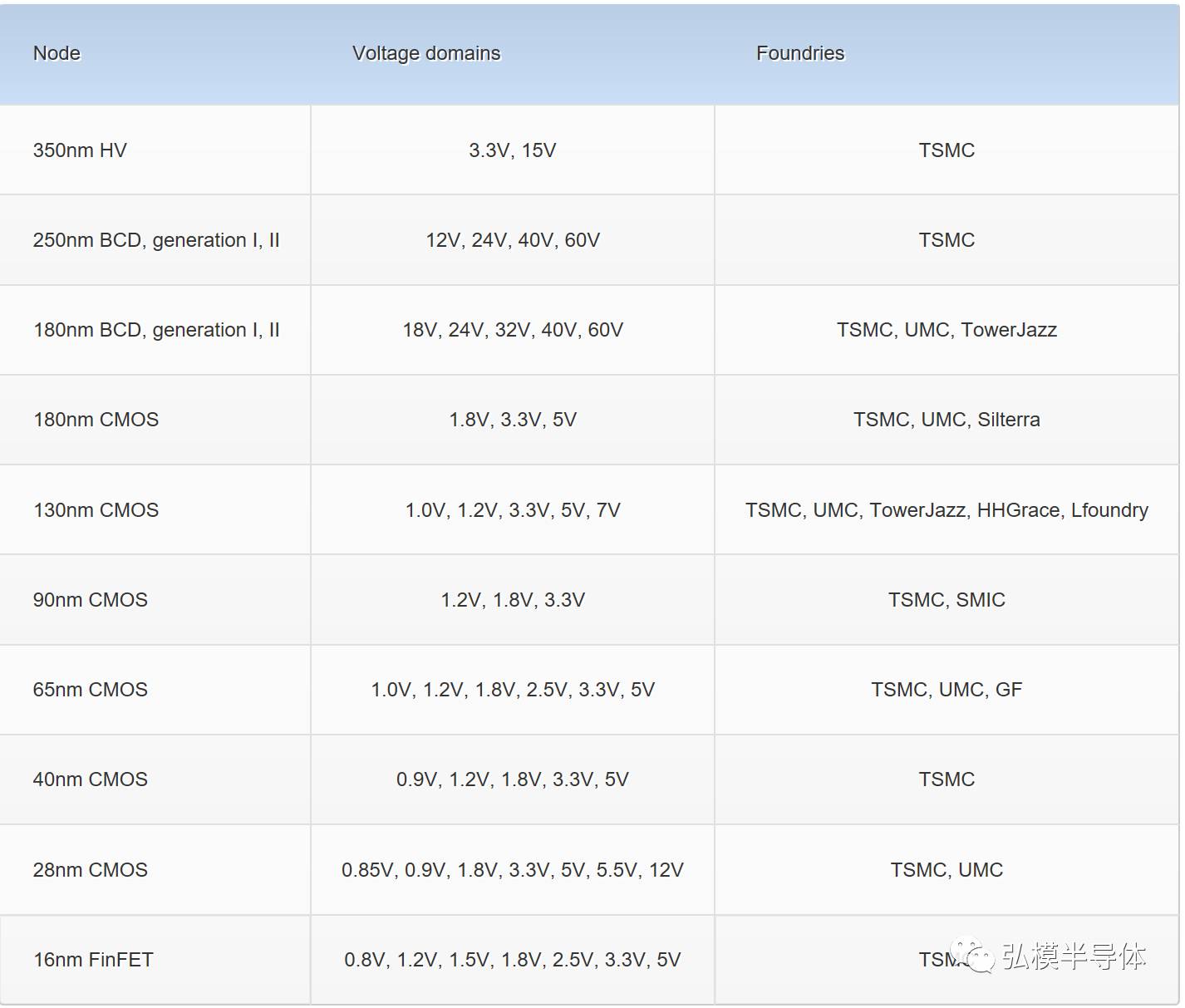

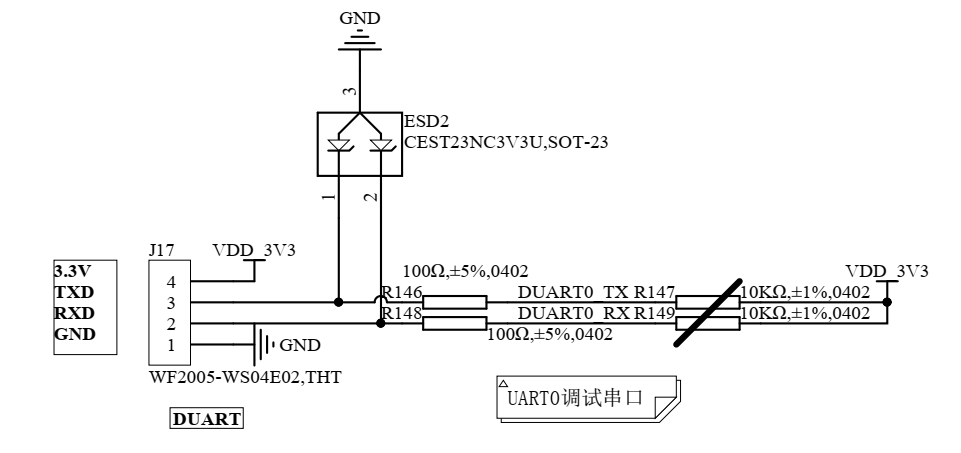

用于控制光学部件和处理信号的发送或接收之前的电子电路,一般采用先进的CMOS技术,比如像28纳米工艺制程。接口一般含有高速(10Gbps,25Gbps或甚至56gbps)的SerDes型电路。为了设计这样的高速差分电路,设计者利用薄氧化物晶体管。然而,这些晶体管是非常敏感的,像静电放电(ESD)的瞬态事件非常容易损坏器件。 这些晶体管可以忍受在瞬态事件的最大电压基本为4V以下。尽管敏感的器件PAD没有连接到封装的外面,但它们在组装过程中仍然会接收ESD的压力。因此,需要在PAD 周边放入足够的ESD保护电路。另一方面,对于信号完整性,在接口焊盘和电源线之间的电容限制是很重要的。

许多先进的CMOS半导体厂提供了一套I/O和ESD保护电路,设计者可以使用。然而,这些标准的、通用的接口块并不适合硅光设计。

一般来说,ESD模块漏电太高

该接口通常运行在一个电压电平低于标准的I/O电压(1.0V相比1.8V,2.5V或3.3V)

高速SerDes电路不能容忍在信号路径上有大量的寄生电容或电阻增加。一个典型的模拟I/O会引入寄生电容150ff,远远超出可容忍的范围。

当然,除了接口部分,SOI光子元器件也需要保针对ESD应力的保护。

经验和优势:

在过去的10年中,国际上很多设计硅光子学产品的公司 (LUXTERA, RocklyPhotonics, Gennum, Nanotech, HiLightSemi...) 得到了我们的支持。在这些项目中,我们的工程师专注于保护高速接口(TX,RX)和低压PAD的保护。 工程师开发的ESD保护,寄生电容在15ff以下,比典型的28nmCMOS 制程ESD保护器件低十倍。

On-chip ESD (Silicon Proven)资源:

-

半导体

+关注

关注

328文章

24520浏览量

202178 -

探测器

+关注

关注

14文章

2440浏览量

72070 -

静电保护

+关注

关注

1文章

131浏览量

19078

发布评论请先 登录

相关推荐

防雷及ESD静电保护器件的发展趋势| 浪拓电子

ESD静电保护区和非静电防护区之间的通道的最小距离

关于光链路需要定制的ESD静电保护的应用和介绍

关于光链路需要定制的ESD静电保护的应用和介绍

评论