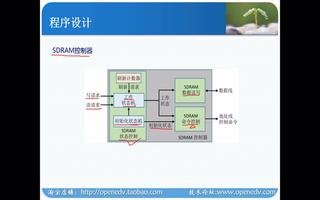

SDRAM具有多种工作模式,内部操作是一个复杂的状态机。SDRAM器件的引脚分为以下几类。(1)控制信号:包括片选、时钟、时钟使能、行列地址选择、读写有效及数据有效。(2)地址信号:时分复用引脚,根据行列地址选择引脚,控制输入的地址为行地址或列地址。(3)数据信号:双向引脚,受数据有效控制。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1602文章

21320浏览量

593161 -

控制

+关注

关注

4文章

997浏览量

122142

发布评论请先 登录

相关推荐

为什么使用SDRAM

目录一、为什么使用SDRAM二、SDRAM芯片W9825G6KH三、stm32f4的fmc接口四、stm32cubemx配置fmc五、实验现象:六、源码:七、注意事项:八、参考记录:硬件平台:正点

发表于 08-04 08:49

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文

,SDRAM的原理和时序,SDRAM控制器,动态随即存储器SDRAM模块功能简介,基于FPGA的SDRA

发表于 12-25 08:00

•56次下载

正点原子开拓者FPGA视频:SDRAM简介

同步动态随机存取内存(synchronous dynamic random-access memory,简称SDRAM)是有一个同步接口的动态随机存取内存(DRAM)。通常DRAM是有一个异步接口

正点原子开拓者FPGA:SDRAM读写测试实验(2)

SDRAM从发展到现在已经经历了五代,分别是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDR

正点原子开拓者FPGA:SDRAM读写测试实验

SDRAM在计算机中被广泛使用,从起初的SDRAM到之后一代的DDR(或称DDR1),然后是DDR2和DDR3进入大众市场,2015年开始DDR4进入消费市场。

正点原子开拓者FPGA:SDRAM时序操作

同步动态随机存取内存(synchronous dynamic random-access memory,简称SDRAM)是有一个同步接口的动态随机存取内存(DRAM)。通常DRAM是有一个异步接口

基于FPGA的DDR3SDRAM控制器设计及实现简介

基于FPGA的DDR3SDRAM控制器设计及实现简介(arm嵌入式开发平台PB)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现

发表于 07-30 09:05

•7次下载

基于FPGA的SDRAM控制器的设计与实现简介

基于FPGA的SDRAM控制器的设计与实现简介(嵌入式开发工程师和基层公务员)-该文档为基于FPGA的SDRAM控制器的设计与实现

发表于 07-30 09:34

•11次下载

正点原子FPGA之SDRAM:SDRAM简介

正点原子FPGA之SDRAM:SDRAM简介

评论