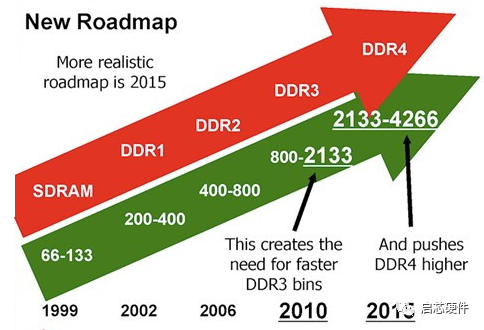

廉价的双倍数据速率(DDR)内存(以及DDR2和DDR3等后来的版本)为台式机和笔记本电脑的工作内存提供了支柱。通过在脉冲序列的前沿和后沿上为存储器提供时钟,存储器吞吐量加倍,而功耗仅略微增加。但是,为了充分利用这种吞吐量并避免这种高频方案的常见问题,例如,无意中触发逻辑器件的振铃和反射,总线终端电路需要自己的电源。为了有效地工作,该电源必须提供主存储器芯片组电源的输入电压的一半,同时能够提供源电流和吸收电流。

本文介绍DDR存储器电源的独特需求,然后检查主要供应商的一些专用电源控制器,以减轻设计工程师的挑战。

DDR的特殊要求

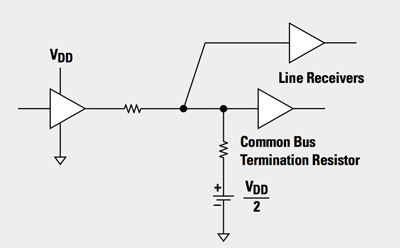

图1说明了一种用于计算机时钟分配网络的流行终端方案,旨在防止可能无意中触发连接到总线的逻辑设备的虚假振铃和反射。这种拓扑结构的另一个优点是,与简单地通过直接接地的电阻器终止线路相比,它将时钟网络中消耗的功率减半(当总线高一半时,而其他时间则低)。权衡要求额外的电源产生VDD/2。

图1:在公共总线终端电阻线上增加第二个电源,使电阻上的平均功耗减半(德州仪器公司提供)。

终端电阻连接到第二电源电压(VTT),该电压等于主电源电压(VDD)的一半。连接第二个电压的结果是,无论电源电压如何,终端电阻的功耗都是恒定的,并且等于VTT(或VDD/2)平方除以终端电阻(来自P =V²/R)。但是,对二次电源的要求是不寻常的。除电源电压(VTT)为主电源电压(VDD)的一半外,器件还需要提供源电流和吸收电流(图2)。当VDD为低电平时,电流从VTT电源流入驱动器。但是,当VDD为高电平时,电流从驱动器流向VTT电源。同样重要的是,VTT电源在状态之间平滑切换,以避免增加功耗的低效率。

图2:DDR存储器VTT电源的工作模式。在左侧,器件以降压模式工作,并在右侧提供电流,作为升压电源和吸收电流(德州仪器公司提供)。

同步开关DC/DC稳压器通常用于VTT电源,因为它比线性低压差稳压器(LDO)更有效(尽管一些设计人员更青睐LDO,因为它更容易融入到LDO中。电源设计)。然而,在这两种不同的工作模式下保持高效率(低功耗)和良好的瞬态响应是一项挑战。

在同步开关降压稳压器中,精确控制从高端MOSFET导通点到低端器件导通点的过渡。可以几乎没有损失地进行高侧到低侧的转换。实际上,首先关闭高侧开关,这允许外部储能电感器将相电压摆动到零。通过使用比较器来感测相电压,然后在没有电压的情况下打开底部开关,可以实现两个器件的零电压切换。相反,从低端到高端的转换是“硬切换”,并且由于相电压必须在正时切换,导致一些交叉传导和电容损耗,因此会产生一些低效率。¹

但是,在升压模式下反之亦然:零电压切换发生在低端到高端转换期间,硬切换发生在电感拉低时。电源设计人员已经提出了一些巧妙的技巧来克服在电源长时间以降压或升压配置工作时很难工作的硬切换低效率,并且很少(如果有的话)在两种模式之间切换。

DDR存储器电路中次级稳压器的降压和升压操作(源极和吸收电流)之间的持续快速翻转,同时器件保持恒定输出电压为主电源(VDD)的一半,与输入电压无关,如果要保持高效率,则输出电流需要与用于传统电源的控制方案相比的不同类型的控制方案。

用于DDR电源的控制模块

幸运的是,DDR电源设计人员不必担心提出控制机制,因为几家主要半导体供应商已将注意力转移到任务上,并已实现商业化的控制器DDR内存电源的独特需求。

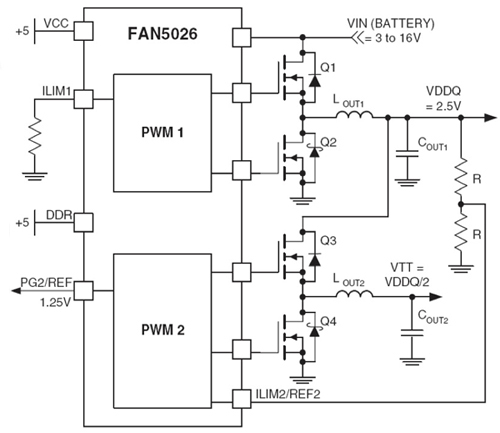

飞兆半导体提供用于存储器应用的FAN5026双DDR/双输出开关控制器。该器件设计用作双脉冲宽度调制(PWM)控制器,驱动两个同步开关稳压器。

在DDR模式下,一个通道跟踪另一个通道的输出电压,并提供必要的输出电流吸收和源功能。该器件提供两个主电源(VDD)输出和一个跟踪VDD/2的二次电源(VTT)。该芯片可在3至16 V的输入范围内工作,该公司表示该器件可在0.9至5.5 V范围内调节两个输出电压,提供高效率和稳压。同步整流和迟滞工作可在轻负载条件下保持效率。

该模块面向服务器和台式机DDR内存电源或显卡电源要求等应用。图3显示了FAN5026的应用电路。

图3:Fairchild FAN5026 DDR电源控制器的应用电路。

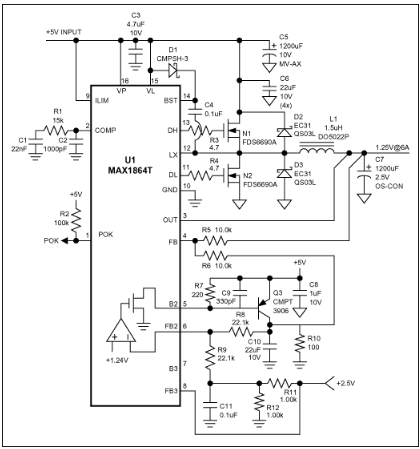

德州仪器还提供DDR和DDR2控制器模块TPS51020。该芯片可在4.5至28 V输入电压下工作,专为高性能,高效率应用而设计,其中与电流检测电阻相关的损耗是不可接受的。例子包括锂离子电池供电的便携式计算机。通过在PWM串中启用自动跳过操作,可以保持轻载条件下的高效率(图4)。

图4:TI的TPS51020专为便携式计算机而设计。该公司称该器件为双开关稳压器DDR电源提供单芯片解决方案。在DDR模式下,TPS51020提供DDR应用所需的所有功能,包括VTT的VDD/2跟踪,电流源和吸收能力以及VTT参考输出。

凌力尔特公司将LTC3876作为完整的DDR电源解决方案提供。该器件兼容DDR,DDR2,DDR3和未来DDRX低电压标准,集成了VDD和VTT控制器以及精密线性VTT参考。该公司表示,差分输出检测放大器和精密内部基准电压相结合,可提供精确的VDD电源。

VTT控制器跟踪精度VTT参考值,总直流误差小于20 mV。在跟踪VDD/2时,参考电压保持1.2%的调节精度。 LTC3876的输入范围为4.5至38 V,VDD范围为1.0至2.5 V,相应的VTT输出范围为0.5至1.25 V.

DDR内存及其后续版本使现代计算机能够在高速而不会显着增加功耗。但是,如果要在DDR运行的高频率下避免杂散信号,则需要仔细设计芯片组并终止公共总线。幸运的是,通过选择市场上的一种商用DDR电源模块,工程师可以在电源设计方面取得重大进展。这些器件集成了为存储器芯片组供电所需的所有功能,并为精确跟踪主电源的终端跟踪提供恒定的减半电压。

-

电源

+关注

关注

182文章

16553浏览量

244699 -

存储器

+关注

关注

38文章

7148浏览量

161984 -

DDR

+关注

关注

9文章

677浏览量

64240

发布评论请先 登录

相关推荐

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 电源解决方案同步降压控制器数据表

完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表

完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表

具有同步降压控制器、2A LDO和缓冲基准的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4内存电源解决方案数据表

完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表

TPS65295完整 DDR4 存储器电源解决方案数据表

TPS65296-完整 LPDDR4/LPDDR4X存储器电源解决方案数据表

如何使用SCR XRAM作为程序存储器和数据存储器?

Altera内存解决方案

DDR内存终端电源

DDR存储器电源的内存解决方案

DDR存储器电源的内存解决方案

评论