严格来讲,是存储器(memory)和储存器(storage)。前者是指在运算中的暂存器,譬如SRAM和DRAM;后者是数据永久储存的器件,如NAND、HDD甚或仍在服役的磁带。之所以会有这样复杂的样态,最主要的原因是CPU运算速度与储存器读写速度之间存有巨大落差。所以从CPU与最终储存器之间,必须建立数层的中介存储器来转换,CPU与几个层次的髙速缓存(cache)SRAM整合在一起,然后外接速度较慢、但每位元价格稍便宜的DRAM,最后到速度差几个数量级、但每位元价格最低廉的的SSD,这就是现存所谓的存储器体制(memory hierarchy)。

这样层层的转送变成现在运算最大的速度和能耗瓶颈,单从能耗来讲,计算机从储存器撷取所需要的数据层层上传、运算完又层层回送储存,这些传递所损耗的能量占整个过程的80%以上。至于速度更不用讲了,运算CPU的速度与储存器的速度有好几个数量级的差距,虽然可以用中介存储器的处理来减少怠速,但一个完整的运算/储存周期大部分的时间是用在传递和储存数据。

之所以有这样的困境是因为几乎所有的储存器或存储器都面临这样的两难:要读写快的,就不容易稳定储存;要稳定储存的,读写速度就慢。这不仅是在过去半导体遭遇的困境,以后在新兴存储器、甚至量子位元我们还会再遭遇类似的问题。譬如超导体量子位元计算快,但量子位元退相干(decoherence)也快,容易产生错误。氮缺陷纳米钻石 (nitrogen vacancy nano diamond)量子位元很稳定,甚至在室温下也可以维持好一阵子,但读写却是千难万难。

目前半导体对于存储器体制的处理方式是用不同材料、不同运作机制,提供不同特性的存储器/储存器,层层部署。最理想的状况是在存储器/储存器中直接运算—两者合而为一,就没有传送、读写等功耗和速度等的损失问题,这就是现在已经开始进入议题的in-memory computing,今年的IEDM会议就有以PCM做in-memory computing展示的论文。但是能做这样工作的存储器/储存器要具备三个特性,一是转换(switch)要快。再者,密度要高,因为现在CPU的gate count很多。最后,要能永久储存。但是目前同时具有这三个性质的存储器/储存器还不存在,所以这是长远目标。

近期比较可能达到的是过去已开始谈论的储存级存储器(Storage Class Memory;SCM),或者意涵稍有差异、现在另外叫Permanent Memory (PM)。要之,两者都是整合了存储器和储存器的功能的单一器件,至少缩短了数据传递的流程。现在跨出第一步的是PCM阵营,基本上PCM由于多层堆栈,密度可以加高,读写速度虽远较NAND为髙,但仍不如DRAM,所以还是需要以微控制器来调节,结构好像与现在的NAND SSD没太大差别。但是由于终端储存器与CPU运算的差距大幅缩小,量变有可能导致质变。譬如可匹配的平行处理核就可以大幅增加。

另一个可以与之竞争的对手是MRAM。目前没有大厂生产制造,价格居髙不下。但是技术的进展已到写入时间10ns,访问时闲20ns,略优于DRAM。而其耐久性近乎无穷大,只是单元细胞的尺寸(cell size)还降不下来。但是MRAM是可以如NAND般往3D发展的,而PCM的堆栈到8层已达最大经济效益,功耗比较大,耐久性也颇有不如。两者的竞争,将是存储器/储存器演化的重要观察指标。

-

存储器

+关注

关注

38文章

7148浏览量

161978 -

cpu

+关注

关注

68文章

10438浏览量

206534 -

SSD

+关注

关注

20文章

2689浏览量

115485

原文标题:【椽经阁】存储器体制的未来演变

文章出处:【微信号:DIGITIMES,微信公众号:DIGITIMES】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

STM32F103DMA模块存储器到存储器可以实现循环吗?

如何使用SCR XRAM作为程序存储器和数据存储器?

AT89C52怎么选择外部存储器?

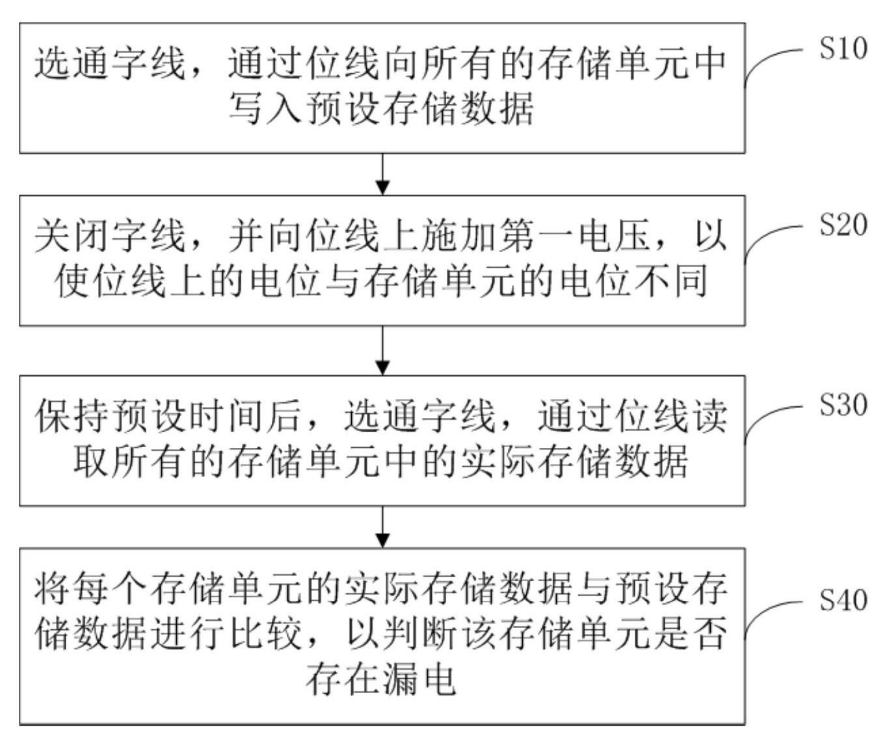

长鑫存储“存储器的检测方法及存储器”专利公布

AXI内部存储器接口的功能

存储器体制的现状和未来改变

存储器体制的现状和未来改变

评论