声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

32文章

1794浏览量

130522 -

IP

+关注

关注

5文章

1404浏览量

148272 -

PCIe

+关注

关注

13文章

1083浏览量

80835

发布评论请先 登录

相关推荐

如何利用Tcl脚本在Manage IP方式下实现对IP的高效管理

在Vivado下,有两种方式管理IP。一种是创建FPGA工程之后,在当前工程中选中IP Catalog,生成所需IP,这时相应的IP会被自动

如何创建硬件在环工程

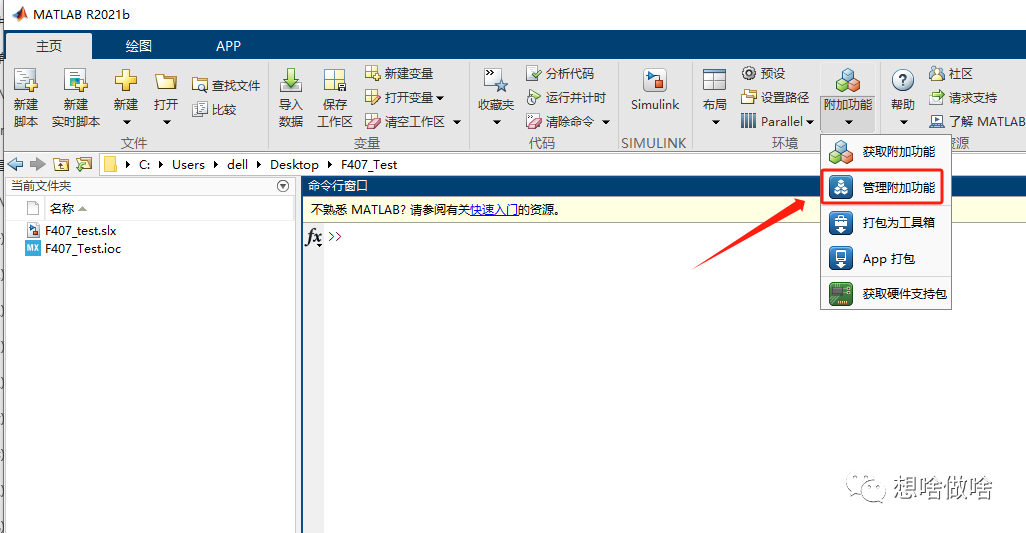

我们很多时候使用的STM32单片机型号无法与官方硬件支持包自带的型号一一对应上,而matlab 2021b版至最新版本可以支持 F4xx系列单片机+CubeMX自定义型号配置使用,本篇以“STM32F407VGT6”型号为例如何创建硬件

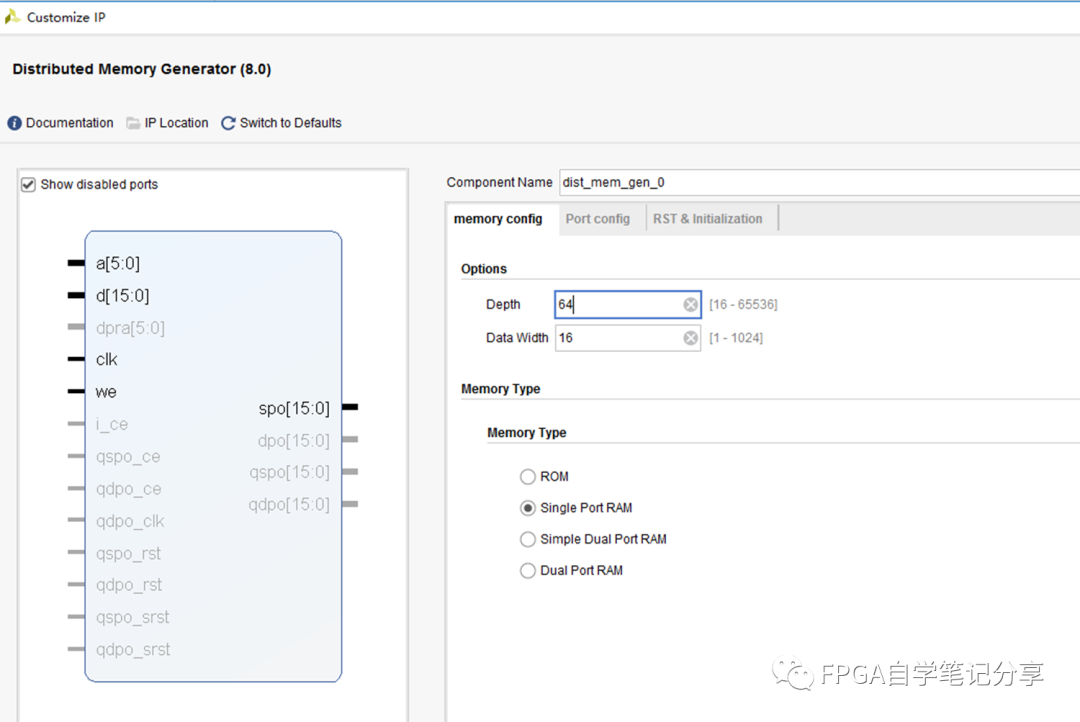

Distributed Memory Generator IP核简介

Distributed Memory Generator IP 核采用 LUT RAM 资源创建各种不同的存储器结构。IP可用来创建只读存储器 (ROM)、单端口随机存取存储器 (RA

使用MATLAB Simulink和HDL编码器创建自定义IP--AWB

自动白平衡模块的设计是使用 HDL Coder 在 MATLAB 和 Simulink 中创建的。HDL Coder能够生成 HDL 文件,这些文件可以作为 IP 在我们的目标 FPGA 中运行。

Vivado Design Suite用户指南:创建和打包自定义IP

电子发烧友网站提供《Vivado Design Suite用户指南:创建和打包自定义IP.pdf》资料免费下载

发表于 09-13 11:34

•0次下载

把子模块包含网表的RTL代码添加到BD中的方法分享

Vivado以IP为核心的设计理念的一个重要支撑就是IP Integrator(简称IPI,IP集成器)。用户可以很便捷地把VivadoIP Catalog中的

使用uIP TCP/IP堆叠的TCP客户端实例

应用程序:使用 uIP TCP/IP 堆叠的 TCP 客户端实例

BSP 版本: M480系列 BSP CMSIS v3.03.001

硬件: NuMaker-PFM-M487 VER 3.0

发表于 08-22 07:47

Integrator/LM-XCV400+逻辑模块用户指南

Integrator/LM-XCV400+逻辑模块被设计为开发用于ARM内核的ASB、AHB和APB外设的平台。

您可以通过三种方式使用它:

·作为独立系统,具有基准电源·具有集成器核心模块和集成

发表于 08-12 07:44

CIC IP用户手册

CIC IP 用户手册 CIC(Cascaded Integrator–Comb Filter),级联积分梳状滤波器,是一种特殊的 FIR 滤波器,其特色是所有滤波系数都为 1,常用于可变数据速率系统。

发表于 08-09 07:42

Integrator/CM940T、CM920T、CM740T和CM720T用户指南

Integrator核心模块为您提供了一个灵活的开发系统的基础,该系统可以以多种不同的方式使用。凭借强大的电源和与Multi-ICE调试器的简单连接,它提供了一个基本的开发系统。通过将核心模块安装到主板上,您可以构建正在开发的系统的逼真仿真。直通板连接器允许最多四个核心模块堆叠在一块主板上。

发表于 08-08 06:50

ARM Integrator/CM926EJ-S、CM946E-S、CM9666E-S、CM1026EJ-S和CM1136JF-S用户指南

本章介绍了ARM Integrator/CMX26EJ-S、Integrator/CM946E-S、IntegratorCM966E-S、积分器/CM1026EJ-S和积分器/CM1136JF-S的核心模块。

发表于 08-02 07:38

无法使用esp8266webserver.h库在给esp8266的静态IP中创建服务器怎么解决?

我无法使用 esp8266webserver.h 库在给我的 esp8266 的静态 IP 中创建服务器。esp8266 采用给定的静态 IP,但它没有为静态 IP

发表于 06-05 13:07

如何使用IP Integrator创建硬件设计

如何使用IP Integrator创建硬件设计

评论