声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

559文章

8216浏览量

364003 -

赛灵思

+关注

关注

33文章

1797浏览量

133151 -

带宽

+关注

关注

3文章

1029浏览量

43025

发布评论请先 登录

相关推荐

热点推荐

请问如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?

如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?有参考教程吗?小白求教

主要是引脚分配,我这边有移植到Xilinx Artix-7 系列XC7A100T-f

发表于 11-11 07:44

如何不用olimex ARM-USB-TINY-H debugger实现调试?

我用的板子是Nexys4 DDR,也就是Artix-7 100T,具体型号是xc7a100ticsg324-1L。

我到e200_opensource/fpga/artydevkit

发表于 11-10 08:15

蜂鸟E203在黑金XC7A200T型FPGA上的移植工作

一、队伍介绍

本篇介绍的内容是蜂鸟E203在黑金XC7A200T型FPGA上的移植工作。

二、前言

由于我们队的设计需要用到DDR,比赛提供的MCU200

发表于 10-31 07:54

一代蜂鸟E203移植普通Artix7核心板中IDE的cfg配置文件修改

大家好,本次我们团队想要分享的是如何将一代蜂鸟E203移植入自己的FPGA并协同NucleiStudio进行Debug时,其中cfg配置文件的修改;

首先我们使用的是Xilinx Artix-7

发表于 10-29 06:45

fpga开发板 璞致Artix-7系列之PA-Starlite Artix7 A735T 75T 100T 200T开发板用户手册-学习板

Artix-7系列开发板是一款基于Xilinx XC7A35T/75T/100T/200T芯片的低成本F

【TES600G】青翼凌云科技基于JFM7K325T FPGA+FT-M6678 DSP的全国产化信号处理平台

的Kintex-7系列FPGAJFM7K325T16作为协处理单元,具有1个FMC子卡接口,具有4路SFP+万兆光纤接口,具有2路RJ45千兆以太网接口,其中1路挂在FP

国产!全志T113-i 双核Cortex-A7@1.2GHz 工业开发板—ARM + DSP、RISC-V核间通信开发案例

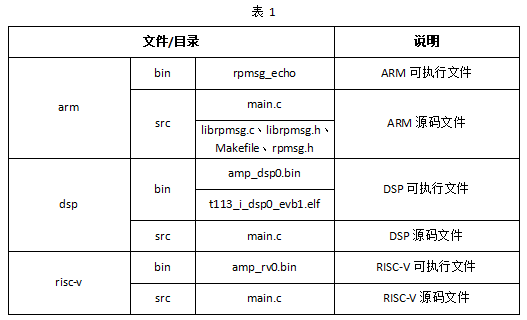

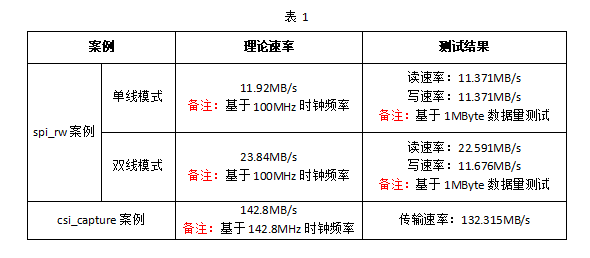

本文档主要介绍T113-i处理器的ARM + DSP、RISC-V核间通信开发案例,演示T113-i处理器ARM Cortex-A7与HiF

全国产V7-690T FPGA核心板/算法验证板设计

使用,可无限扩展信号处理能力。FMC连接器也满足标准规范,可以插入标准的FMC或FMC+子板。

SOM-404电路原理框图设计:

技术特点:

国产化率100%,与进口器件兼容

FPGA:可选

发表于 04-09 11:25

求助,关于A/D输入信号带宽的问题求解

信号的最高频率还是真正的模拟信号带宽?

2、从datasheet上如何看器件所容许的最大信号带宽参数?如1GSPS的采样A/D,是否就可容

发表于 02-06 06:47

【米尔-Xilinx XC7A100T FPGA开发板试用】 UART测试

硬件:

一 米尔-Xilinx XC7A100T FPG

二 12V电源适配器

三 下载器

四 win10笔记本

软件:

一 Vivado (指导手册有详细的安装下载流程)

二 官方示例工程

这个

发表于 01-12 10:10

【米尔-Xilinx XC7A100T FPGA开发板试用】Key-test

硬件:

一Xilinx XC7A100T FPGA开发板

二12V电源适配器

三下载器

四 win10笔记本

软件:

一Vivado (指导手册有详细的安装下载流程)

二官方按键示例工程

按键示例

发表于 01-09 16:08

米尔-Xilinx XC7A100T FPGA开发板试用

MYB-J7A100T-I 底板⽀持串口,网口,HDMI,PCIE,Micro SD 卡接口,SFP+,摄像头,扩展口等多种接口。

1.核心板硬件资源:

2.底板资源:

开发板接口:

1.CIS

1

发表于 01-08 10:49

当DSP与FPGA通讯的时候,XZCS0、XZCS6、XZCS7会影响ADS8556的工作吗?

您好,我想用3个ads8556和1个FPGA都通过TMS320F28335的XINTF接口与DSP相连,3个ads8556占用了XZCS0、XZCS6、XZCS7三个片选信号,DSP

发表于 12-20 07:30

【米尔-紫光MYB-J7A100T国产FPGA开发板试用】米尔-紫光PG2L100H国产FPGA开发板开箱评测

很感恩能收到电子发烧友[论坛](https://bbs.elecfans.申请的 米尔-紫光L100H国产FPGA开发板,现在特地来写篇测评报告,米尔-紫光MYB-J7A100T国产FPGA

发表于 12-09 11:11

有着最高DSP带宽的Artix-7 A100T FPGA器件介绍

有着最高DSP带宽的Artix-7 A100T FPGA器件介绍

评论