在FPGA设计过程中,使用好双口RAM,也是提高效率的一种方法。

官方将双口RAM分为简单双口RAM和真双口RAM。

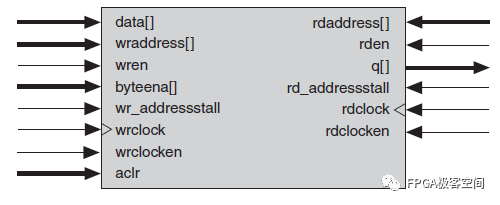

简单双口RAM只有一个写端口,一个读端口。

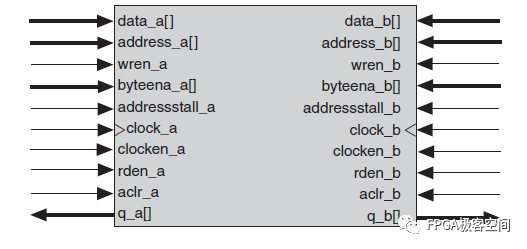

真双口RAM分别有两个写端口和两个读端口。

无论是简单双口RAM还是真双口RAM,在没有读操作的情况下,应将读使能rden信号拉成低电平,节省功耗。

在两种情况下,都应当避免read-during-write,虽然可在软件中进行设置,但是,作为设计者,应当尽量避免此种情况。

对于真双口RAM,还应当避免两个读端口或者两个写端口同时操作同一个地址,RAM中并没有此种冲突解决电路,设计者应该避免这种冲突。

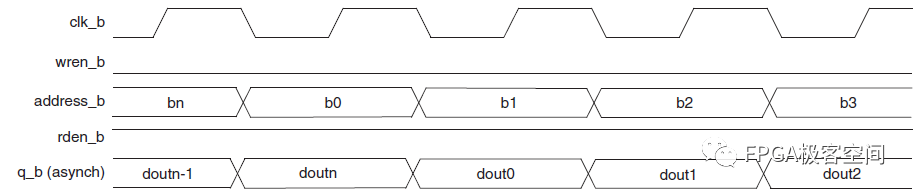

无论是那种双口RAM,读时序图是相同的。

当读使能有效时,数据会在时钟下一个上升沿从Q端输出。

真双口RAM给设计带来很多便利。在高速存储中,需要对连续的数据同时处理,使用简单双口RAM只能读取一个数据,而使用真双口RAM可以同时读取两个数据,这样明显提高读取速度以及处理速度。

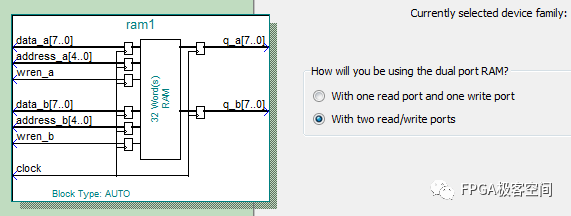

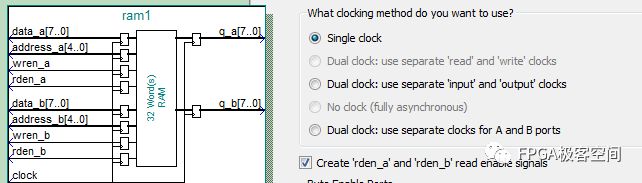

调用真双口RAM,如图设置。

这里可以设置时钟方案,而读使能rden并非必须信号。当使用rden信号时,此信号高电平有效,当不使用rden信号时,给定地址,下一个脉冲数据从q端口送出。

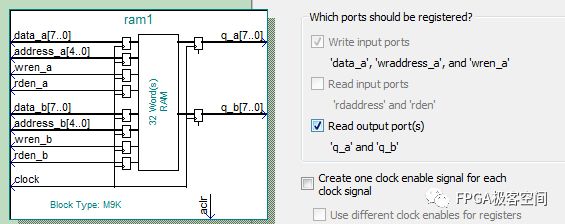

这里的设置非常重要,当选中read output ports时,q端会增加一级寄存器。虽然这样增加流水线能够提高电路的速度,但同时从读使能有效到最终数据有效将会多延迟一个时钟周期。在设计中要格外注意。根据设计自行设置。

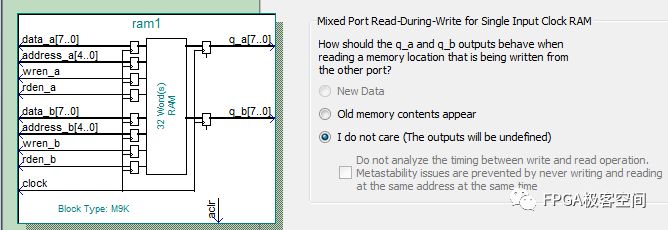

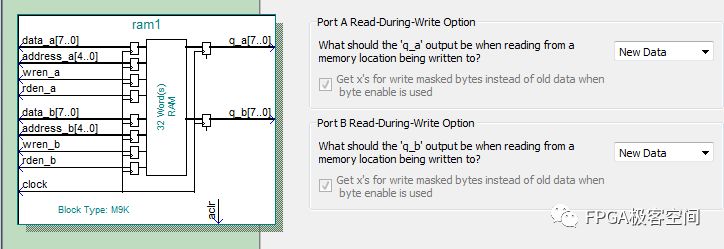

上面两张图是指定对同一地址操作时的输出。作为设计者,应尽量在自己的设计中避免这种情况发生。

真双口RAM用好了是非常省时间的。之前我们文章中提到硬件FFT的实现,在实现过程中,使用基2的设计方案,需要同时读取两个RAM数据,这种情况下可以使用真双口RAM提高效率。

-

FPGA

+关注

关注

1602文章

21320浏览量

593158 -

RAM

+关注

关注

7文章

1321浏览量

113705 -

电平

+关注

关注

5文章

338浏览量

39563

原文标题:双口RAM,值得研究

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

RAM分为简单双口RAM和真双口RAM

RAM分为简单双口RAM和真双口RAM

评论