通常所说的JTAG大致分两类,一类用于测试芯片的电气特性,检测芯片是否有问题;一类用于Debug;一般支持JTAG的CPU内都包含了这两个模块。

一个含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,象UART,Timers,GPIO等等的寄存器。

下面是一个设置AT91M40800的命令序列,关闭中断,设置CS0-CS3, 并进行Remap,适用于AXD(ADS带的Debug)

setmem 0xfffff124,0xFFFFFFFF,32 ---关闭所有中断setmem 0xffe00000,0x0100253d,32 ---设置CS0 0xffe00004,0x02002021,32 ---设置CS1setmem 0xffe00008,0x0300253d,32 ---设置CS2setmem 0xffe0000C,0x0400253d,32 ---设置CS3setmem 0xffe00020,1,32 ---Remap

如果要在ADW(SDT带的DEBUG)中使用,则要改为:

let 0xfffff124=0xFFFFFFFF ---关闭所有中断let 0xffe00000=0x0100253d ---设置CS0let 0xffe00004=0x02002021 ---设置CS1let 0xffe00008=0x0300253d ---设置CS2let 0xffe0000C=0x0400253d ---设置CS3let 0xffe00020=1 ---Remap

为了方便使用,可以将上述命令保存为一个文件config.ini, 在Console窗口输入 ob config.ini 即可执行。

使用其他debug,大体类似,只是命令和命令的格式不同。

设置RAM时,设置的寄存器以及寄存器的值必须和要运行程序的设置一致。一般编译生成的目标文件是ELF格式,或类似的格式,包含有目标码运行地址,运行地址在Link时候确定。

Debug下载程序时根据ELF文件中的地址信息下载程序到指定的地址。如果在把RAM的基地址设置为0x10000000, 而在编译的时候指定Firmware的开始地址在0x02000000, 下载的时候,目标码将被下载到0x02000000,显然下载会失败。

使用这种方式,比起FlashPGM的写Flash,速度似乎要快一些。

01

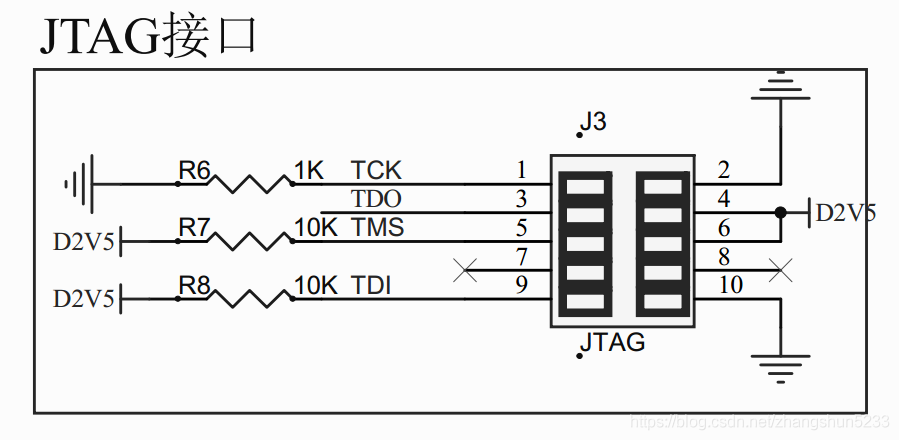

关于简单JTAG电缆

目前有各种各样简单JTAG电缆,其实只是一个电平转换电路,同时还起到保护作用。JTAG的逻辑则由运行在PC上的软件实现,所以在理论上,任何一个简单JTAG电缆,都可以支持各种应用软件,如Debug等。

我就曾使用同一个JTAG电缆写Xilinx CPLD,AXD/ADW调试程序。关键再于软件的支持,大多数软件都不提供设定功能,因而只能支持某种JTAG电缆。

关于简单JTAG电缆的速度。JTAG是串行接口,使用打印口的简单JTAG电缆,利用的是打印口的输出带锁存的特点,使用软件通过I/O产生JTAG时序。

由JTAG标准决定,通过JTAG写/读一个字节要一系列的操作,根据我的分析,使用简单JTAG电缆,利用打印口,通过JTAG输出一个字节到目标板,平均需要43个打印口I/O, 在我机器上(P4 1.7G),每秒大约可进行660K次 I/O 操作,所以下载速度大约在660K/43, 约等于15K Byte/S. 对于其他机器,I/O速度大致相同,一般在600K ~ 800K.

02

关于如何提高JTAG下载速度

很明显,使用简单JTAG电缆无法提高速度。要提高速度,大致有两种办法:

1、使用嵌入式系统提供JTAG接口,嵌入式系统和微机之间通过USB/Ethernet相连,这要求使用MCU。

2、使用CPLD/FPGA提供JTAG接口,CPLD/FPGA和微机之间使用EPP接口(一般微机打印口都支持EPP模式),EPP接口完成微机和CPLD/FPGA之间的数据传输,CPLD/FPGA完成JTAG时序。

这两种方法本人都实现过。

第一个方法可以达到比较高的速度,实测超过了200KByte/S(注意:是Byte,不是Bit);但是相对来说,硬件复杂,制造相对复杂。

第二种相对来说,下载速度要慢一些,最快时达到96KByte/S,但电路简单,制造方便,而且速度可以满足需要。第二种方案还有一个缺点,由于进行I/O操作时,CPU不会被释放,因此在下载程序时,微机CPU显得很繁忙。

总的来说,本人认为,对于个人爱好者来说,第二种方法更可取。

-

嵌入式

+关注

关注

4981文章

18278浏览量

288377 -

寄存器

+关注

关注

30文章

5028浏览量

117712 -

JTAG

+关注

关注

6文章

383浏览量

71150

原文标题:你的设计为什么出问题?也许是嵌入式JTAG接口惹的祸

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

含有JTAG Debug接口模块的CPU提高下载速度

求助关于FPGA jtag下载

嵌入式开发arm技术JTAG接口解读

ISE JTAG Chain无法找到电缆

JTAG接口下载线的制作

STK500 ISP JTAG下载烧录

H-JTAG调试手册

JTAG接口分类及如何提高JTAG下载速度

JTAG两大类详解及JTAG电缆提速方法

嵌入式JTAG接口你了解多少

FPGA JTAG接口下载速度很慢咋办?

关于简单JTAG电缆,如何提高JTAG下载速度

关于简单JTAG电缆,如何提高JTAG下载速度

评论