声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

544文章

7682浏览量

344348 -

ti

+关注

关注

111文章

8187浏览量

210924 -

Cache

+关注

关注

0文章

127浏览量

27978

发布评论请先 登录

相关推荐

DSP上如何加载LINUX内核运行?

你好

最近在官网下载了在C64+,C66X的LINUX内核,我打算在C6455板卡上运行其LINUX内核,但我阅读使用手册,发现其

发表于 05-25 01:41

C6670 Cache一致性维护的问题

d的64 Bytes Cache Line对齐

并在CMD文件中,将该变量分配到共享存储区

.shareMemotest load >> MSMCSRAM

3. 在

发表于 06-19 04:23

C6678 多核程序的初始化及L1P cache一致性问题

P 32KB cache,L1D 32KB cache,LL2 全部做SRAM。请问,L1P cache和LL2之间的

发表于 06-21 14:21

6618虚拟定点数学库IQmath

慢一倍,不知道什么原因?另外C64+系列的定点虚拟库中,有定义16bit数据的类型,但没有想过不同Q值得运算函数。怀疑是不是数据长度依旧采用32bit所以速度没有显著提升。求大神解答!

1

发表于 06-21 11:23

请问C6748分别在simu和emu下调用运算库DSP_dotprod,cycle数不对,emulation下慢4倍,这是为什么?

支持C67芯片,不知道C64的库是不是全支持,现在运算结果是正确的)DSP_dotprod.h中说cycle=N/4+16,在CCS5.4的

发表于 06-21 06:21

C6000 DSP二级cache的工作机理,是不是说,代码段.text中的指令要从DDR或者SDRAM中被搬运或者映射到L1P cache中才能被执行?

本帖最后由 一只耳朵怪 于 2018-6-22 14:18 编辑

关于C6000 DSP 二级cache的工作机理有一些问题,像和大家讨论下。谢谢!cpu一上电,就要开始一条条的

发表于 06-22 02:29

在DSP/BIOS想将L2的64k配置成cache,请问需要怎么操作?

您好,我使用的芯片是C6748,使用DSP/BIOS。C6748的L1P L1D L2都可以部分配置成缓存或RAM。

发表于 08-02 06:54

c6000 dsp的 cache line有多长

请问一下c6000 dsp的 cache line有多长?也就是一个数组,取其中一个元素,会把这个元素附近的多少个元素带入到缓存中?是加载这个元素两边的数据,还是后面的数据?多谢了!

发表于 05-22 15:06

基于c64+的DSP芯片的特点

此次培训课程,会让您了解到,基于c64+的DSP芯片,能满足电信,医疗,视频处理应用领域中,高性能DSP的需求。由DSP高性能部门技术支持工程师为您全程指导,敬请观看。

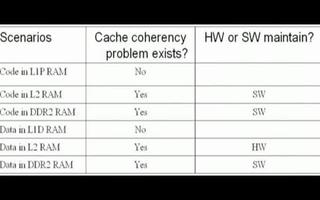

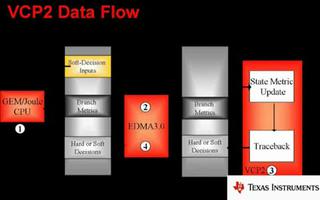

DSP上Cache 在 C64+ 系列中的应用(1)

DSP上Cache 在 C64+ 系列中的应用(1)

评论