声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

544文章

7682浏览量

344356 -

ti

+关注

关注

111文章

8187浏览量

210924

发布评论请先 登录

相关推荐

C64x+ DSP的可屏蔽硬件异常(EXCEP)

请问有谁使用过TI C64x+ 以上DSP的异常处理功能吗?我在使用该功能时碰到不少问题,希望能与使用过该功能的小伙伴一起讨论交流。我目前的问题是,通过“SEW”指令触发软件异常时,系统会反复进入

发表于 05-16 15:37

请教关于C64x+, 中断嵌套,参考资料有些冲突,

to pending interrupts”,说可屏蔽中断,不可以被嵌套。2.在“”TMS320C64x/C64x+ DSPCPU and Instruction Set”中,又有一篇专门讲

发表于 07-25 09:27

请教两个关于C64x+两个简单问题

1:我用的是C6424,是小端模式。我看见CCS配置平台有能设置成大端模式,于是设置了大端模式,编译一切都可以通道。最后在load到DSP的RAM 就报错误,请问有人设置过C64X+的大小端没事没有

发表于 08-01 06:40

C6457板子,想用CCS3.3来调试,请问仿真器的配置该如何选择?

我设计的C6457板子,想用CCS3.3来调试,仿真器的配置该如何选择?C64X+还是C64XX?C64X+里面只有C6455啊?

发表于 08-07 06:38

DSP C64x+异常处理的原因是什么?

你好,我使用的芯片是OMAP3530,对应的DSP型号为dm3730,开发环境为CCS3.3,BIOS5.4。在DSP/BIOS系统下开发。现在想使用C64x+芯片提供的异常处理机制来监测处理系统

发表于 08-13 08:17

C64x+与C64x CACHE的区别是什么

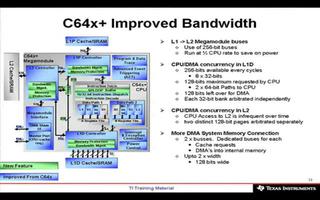

和充分利用miss pipelining变得非常重要。对C64x+来说,有了L1 SRAM、比较大的L1 cache容量、low-overhead snooping和L2 cache

发表于 12-04 16:04

C64x+与C64x CACHE的区别是什么

和充分利用miss pipelining变得非常重要。对C64x+来说,有了L1 SRAM、比较大的L1 cache容量、low-overhead snooping和L2 cache

发表于 12-14 15:33

C64x+ DSP高速缓存一致性分析与维护

C64x+ DSP高速缓存一致性分析与维护

高速缓存(CACHE)作为内核和低速存储器之间的桥梁,基于代码和数据的时间和空间相关性,以块为单位由硬件控制器自动加载内核所需

发表于 01-04 12:00

•1294次阅读

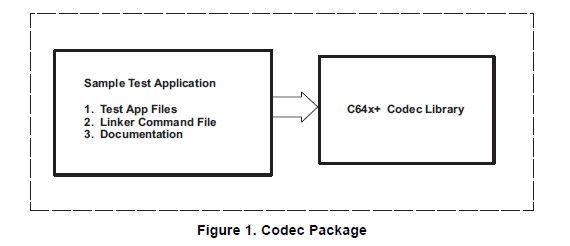

C64x视频设备的差异基于DSP平台运行的不同的TMS320C64x+编码解码器

本应用报告描述了运行C64x+™视频设备的差异基于平台不同的C64x+编解码软件。该文件假定编解码器软件是针对C64x+的数字信号处理器(DSP)为核心的。许多TI

发表于 04-18 17:14

•4次下载

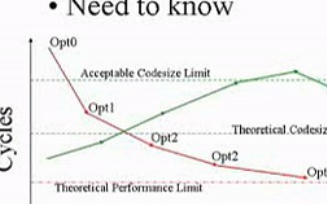

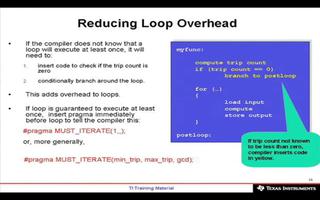

介绍 TMS320C64x 的c代码优化

TMS320C64x+网络课程4——c 代码优化,其中包括:优化c编译程序, 编写c源代码, 环路改造, DSP编制程序的基本规则。此网络培训针对C64x+,每次一个专题,由DSP高性

讲解利用 C64x+ 平台优化的方法

讲解利用 C64x+ 平台优化的方法

评论