你评估过一个ADC的噪声性能,并且发现测得的性能不同于器件数据表中所给出的额定性能吗?在高精度数据采集系统中实现高分辨率需要对模数转换器 (ADC) 噪声有一定的认识和了解。有必要了解数据表如何指定噪声性能,以及外部噪声源对总体系统性能的影响方式。其中的一个噪声源示例就是我的同事Ryan Andrews在他的博文,“小心!你的ADC的性能也许只和它的电源性能差不多。”中所谈到过的电源噪声。在这篇博文中,我将会看一看基准噪声如何影响增量-累加ADC中的DC噪声性能。

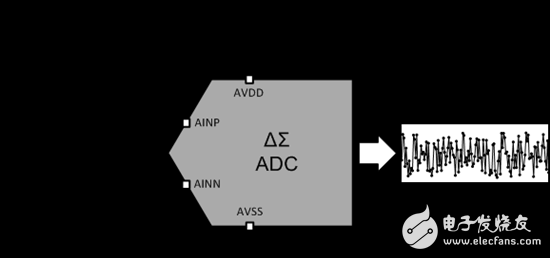

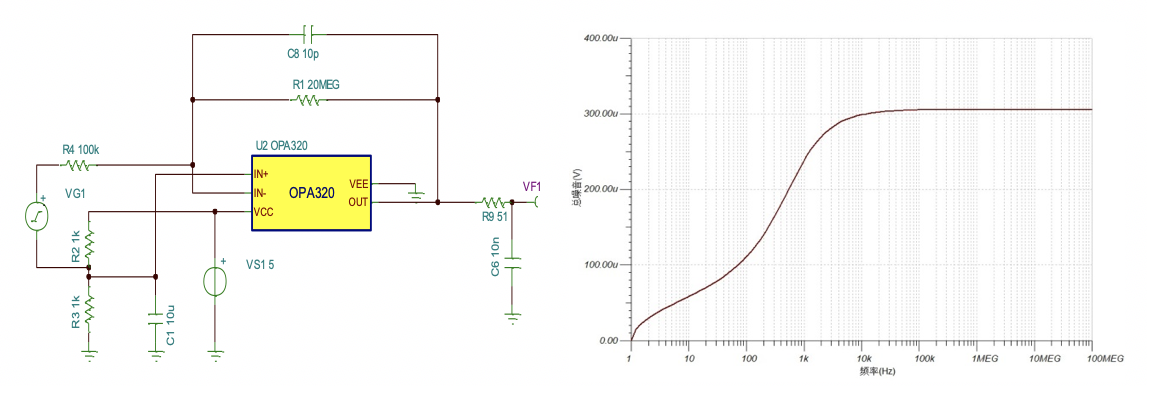

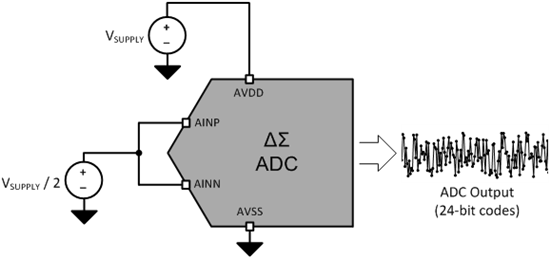

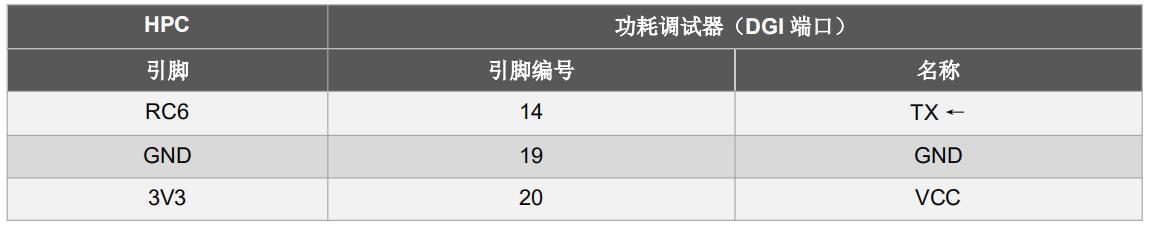

如图1所示,你可以用短接至中电源电压的正负输入来指定和测量一个ADC的DC噪声性能。通过测量这个条件下的噪声,ADC输出代码内的噪声几乎不受基准电压、基准噪声或输入信号噪声变化的影响。虽然这个测试条件相对于实际应用来说是一个过于理想的情况,它的确较好地给出了一个不受某些外部噪声源影响的ADC噪声性能。

图1:ADC噪声性能测试(和调试)配置

提示:调试时,在开始其它系统噪声性能测试之前,用评估隔离式ADC噪声性能的短接输入测试来开始评估系统的噪声性能。

基准噪声如何影响ADC DC噪声性能

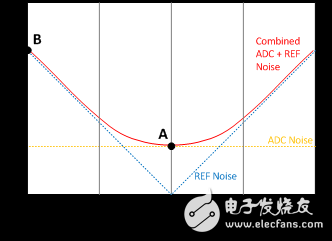

这个影响与ADC的基本任务相关;而ADC的基本任务就是提供一个输出代码,来表示输入信号电压与基准电压的比率。输入和基准电压都会将一个噪声项添加到这个比率中,如方程式1所示:

(1)

输入信号噪声,

,对于ADC转换结果的影响是非常直接的。ADC将捕捉未被滤除掉的任何噪声—使用外部电阻-电容 (RC) 滤波器,或者增量-累加ADC的信号滤波器进行过滤。由于

对于方程式1中的比率有直接影响,你可以在输出代码中进行观察。

提示:在评估ADC噪声性能时,由于输入信号的噪声直接影响ADC的输出结果,请确保输入信号是一个低噪声源。

然而,基准噪声,

,对于ADC转换结果的影响并不直接,这是因为

出现在分母中。当分子为零时(就与ADC输入被短接的情况一样),这个比率始终为零,而

项将不会影响比率。当分子与分母大体相等时,

将会对比率有很大的影响。当比率介于0和1之间时,

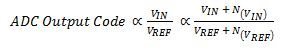

的影响由比率值来衡量。图2显示的是得出的特性运行方式。

图2:ADC和基准噪声与输入电压之间的关系

当通过使用均方根增加的方法将基准噪声添加到ADC的噪声中时,这个组合噪声是输入电压的函数,它会在正或负输入电压变大时增加。在图2中的曲线上,有几个点需要注意:

-

点A,这是用ADC数据表中给出的短接输入测得的ADC噪声。

-

点B,这是总带宽限制基准噪声,通常受到ADC数字滤波器带宽的限制。

如果你知道针对噪声源的噪声频谱密度和噪声带宽的话,你就能够计算出基准噪声(点B);否则的话,将一个满量程电压输入施加到ADC上,并且测量噪声性能,这样通常能够获得一个比较好的基准噪声测量值。

如何选择一个基准电压源

对于在整个ADC输入范围内实现低噪声/高分辨率性能来说,一个低噪声基准十分重要。基准噪声需求将取决于系统的目标分辨率、输入信号范围和数据速率(而这通常限制了输入和基准噪声带宽)。当噪声带宽受到较慢数据速率限制时,或者输入信号跨度被限制在ADC满量程范围内的一个较小区间内,系统能够耐受额外的基准噪声。

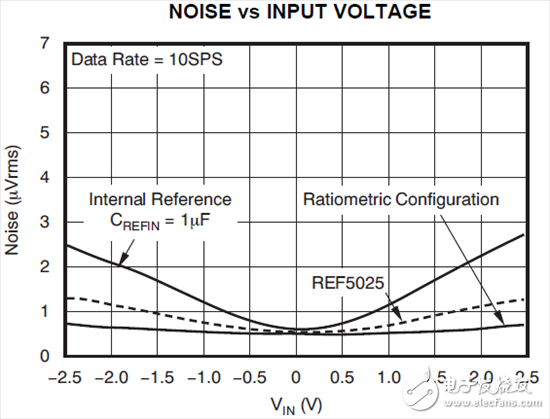

很多增量-累加ADC包含一个集成基准,它为大多数应用提供了充足的性能。对于要求更加严格的应用,使用一个外部基准也许可以提升输入处于正和负满量程范围附近时的噪声性能。外部高精度基准可以实现更低的噪声性能,这是因为它们的功耗更高。图3将24位ADS1259增量-累加ADC的噪声性能与内部基准源、一个外部REF5025电压源,以及一个比例换算的基准源进行比较。

图3:具有内部、外部和比例换算基准源的ADS1259噪声性能

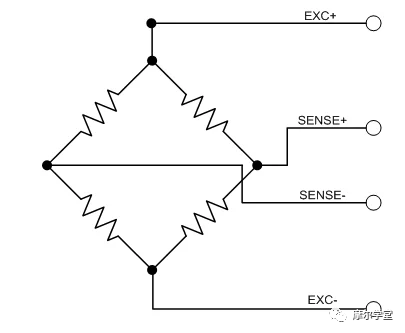

虽然外部基准也许能够实现比集成基准更好的噪声性能,而比例换算基准配置的表现更佳。一个比例换算配置在基准电压和输入信号激励方面共用同样的电压源。通过共用一个共同的电压和噪声源,方程式1中的和往往在比率中相互抵消。

当你下次评估ADC的噪声性能时,请确保将基准噪声效应考虑在内。此外,只要传感器需要一个激励源,比例换算测量实现方式应该成为你的首选。

-

adc

+关注

关注

95文章

5651浏览量

539453 -

噪声发生器

+关注

关注

0文章

22浏览量

9801 -

ADS1259

+关注

关注

0文章

6浏览量

11829

发布评论请先 登录

相关推荐

基于ADC的放大器噪声性能评估

ADC电源的噪声要求

使用DC / DC转换器为ADC供电

DC–DC转换器为GSPS ADC提供高效输电网络

GSPS ADC搭配DC-DC转换器,提高输电网络效能

增量累加ADC是什么组成的?

增量累加ADC的应用

电压基准噪声对于增量-累加ADC分辨率的影响

如何影响累加ADC中的DC噪声性能

如何影响累加ADC中的DC噪声性能

评论