乘法 DAC 是波形发生应用的理想构建模块。因为乘法数模转换器 (DAC) 的 R-2R 架构非常适合低噪声、低毛刺、快速建立的应用。

从固定参考输入电压产生波形时,必须考虑一些重要的交流规格,包括建立时间、中间电平毛刺和数字 SFDR。

今天我们就来分析下这些与波形发生相关的重要 DAC 规格。

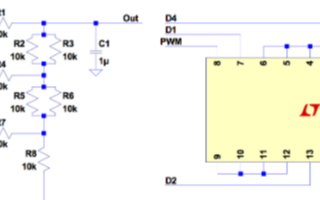

建立时间假设 DAC 由真实的宽带低阻抗信号源(参考电压和接地引脚)驱动,那么它会迅速建立。因此,乘法 DAC 的压摆率和建立时间主要由运算放大器决定。决定运算放大器交流性能的规格包括其输入电容(必须保持最小)和 3 dB 小信号带宽。注意,运算放大器的带宽之所以受限,是因为它必须驱动 DAC 反馈电阻这一较大负载。例如,10 kΩ 的反馈电阻就是一个相当大的负载,它是决定电路配置带宽的主要极点。

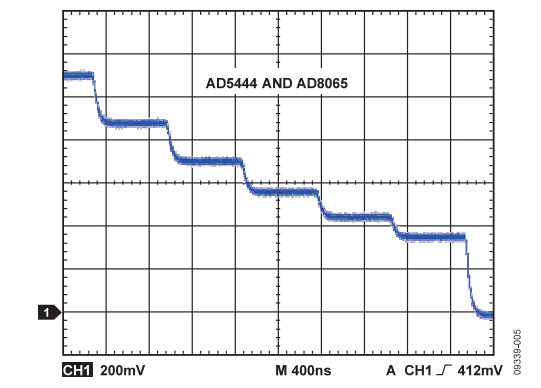

图 1. 100 ns 建立时间

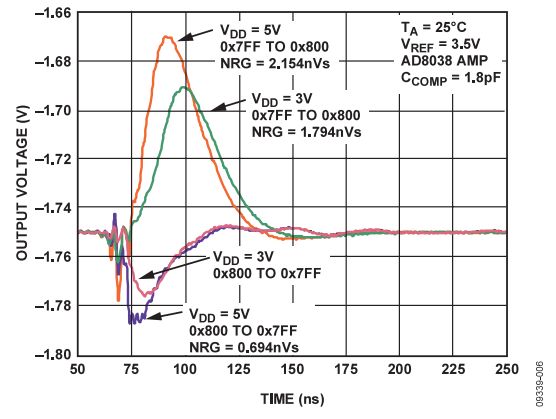

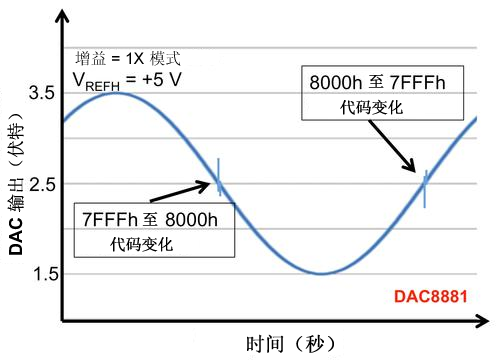

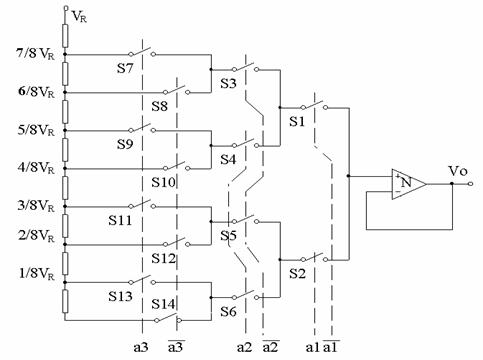

中间电平毛刺对于 R-2R 结构,代码变化引起的主要毛刺出现在围绕中间电平发生 1 LSB 变化时。在一个 12 位系统中(如 DACAD5444), 中间电平变化是从 7FFH 至 800H 或从 800H 至 7FFH 的代码 变化。如果毛刺很严重,可能会给电机 / 阀门 / 执行器控制应用带来不利影响。当乘法 DAC 试图从 7FFH 变为 800H时,DAC 的 MSB 切换速度低于其它位的切换速度。因此, 在 MSB 切换至 1 前的几纳秒内,DAC 看到的是 000H。图2 中的黄色曲线显示的就是这种情况 ;在 MSB 切换并将 DAC 输出拉回 800H 之前,输出朝 0 V 变化。

图 2. 中间电平毛刺

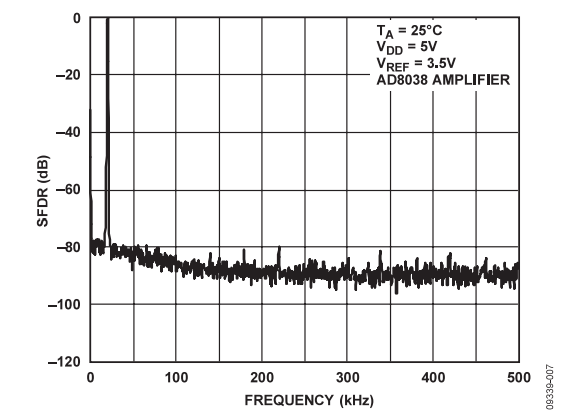

数字 SFDR无杂散动态范围 (SFDR) 指 DAC 的可用动态范围,超出此范围,杂散噪声就会干扰基波信号或使其失真。SFDR 衡量基波与 DC 至全奈奎斯特带宽(DAC 采样速率的一半) 范围内的最大谐波或非谐波相关杂散的幅值之差。窄带 SFDR 衡量任意窗口范围内的 SFDR。理想正弦波的每个周期有无数个点。然而,用数字方式产生的正弦波受固定更新速率和 DAC 分辨率的限制。每个周期的点数由下式给出 :

其中 :

N = 采样点数

Clock = DAC 的更新速率

fOUT = 所产生波形的输出频率

图3所示为使用 12 位 AD5444 产生的更新速率为 1 MHz 的 20 kHz 正弦波,每个周期有 50 个采样点。AD5444 的最大更新速率为 2.7 MSPS。若要产生采样点更多的波形,必须使用更快的更新速率。并行接口的 AD5445 提供 20 MSPS 的最大更新速率。

图3. 宽带 SFDR,fOUT = 20 kHz,时钟 = 1 MHz

-

信号源

+关注

关注

5文章

537浏览量

47357 -

数模转换器

+关注

关注

14文章

1272浏览量

85181

原文标题:输出波形怎么样,就看这些规格了

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

令人困扰的DAC输出短时毛刺脉冲干扰

利用PWM和小型R-2R梯形DAC达到减小纹波和提高分辨率的效果

分析下那些与波形发生相关的重要乘法数模转换器(DAC)规格

在低噪声的前置放大器中使用低电阻值

将PWM与小型R-2R梯形结合可以改善两者。它可以显着降低PWM纹波并提高DAC的分辨率

电阻器梯形结构:R-2R DAC与MDAC架构

该设计可减少DAC R-2R架构干扰

使用FPGA驱动R-2R电路输出正弦波资料分享

分析与波形发生相关的重要 DAC 规格

实现DA转换器双极性电压输出的双R-2R电阻网络结构

两种非常相似的架构:R-2R DAC 与 MDAC

高压R-2R DAC的去毛刺技术

为何说R-2R架构非常适合低噪声、低毛刺应用

为何说R-2R架构非常适合低噪声、低毛刺应用

评论