我知道,我对与电子有关的所有事情都很着迷,但不论从哪个角度看,今天的现场可编程门阵列(FPGA),都显得“鹤立鸡群”,真是非常棒的器件。如果在这个智能时代,在这个领域,想拥有一技之长的你还没有关注FPGA,那么世界将抛弃你,时代将抛弃你。本公众号作者ALIFPGA,多年FPGA开发经验,所有文章皆为多年学习和工作经验之总结。

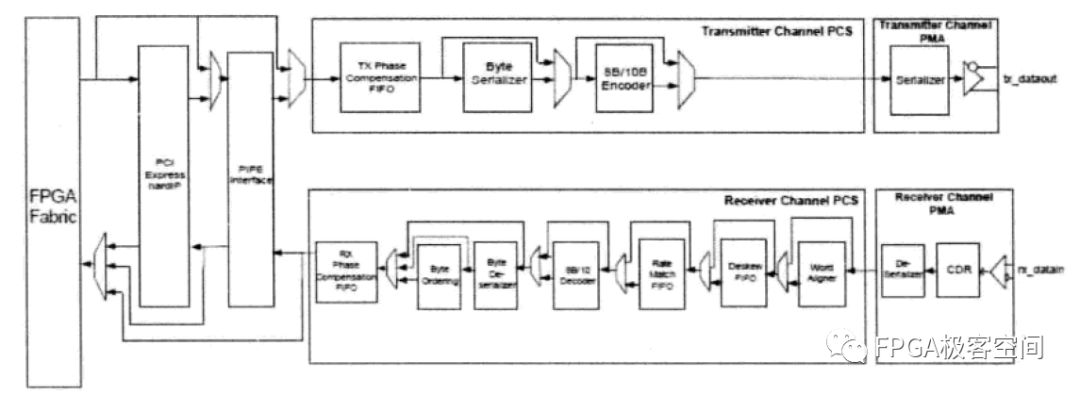

Stratix IV GX内嵌SERDES结构如图所示

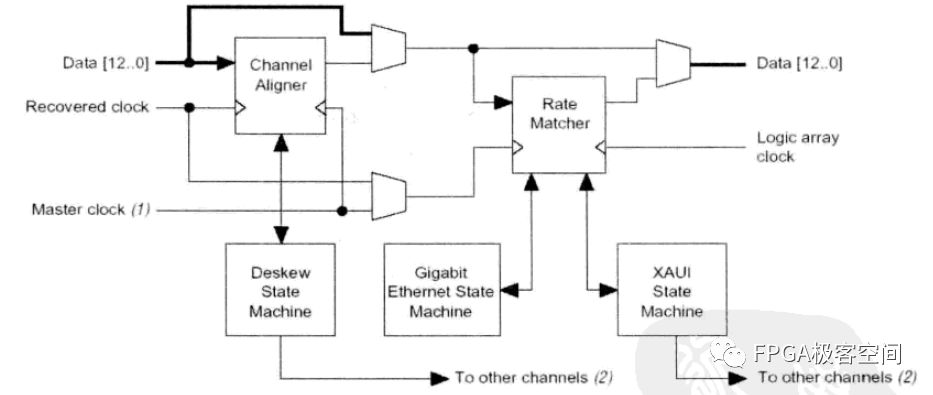

通道对齐(Channel Aligner)和速率匹配(Rate Matcher)。

Channel Aligner和Rate Matcher根据各种接口标准的物理编码子层(PCS,Phsical Coding Sub-layer)规定,将数据的所有通道对齐,并适配数据速率,同步编码状态机。常用的接口标准有GE、10GE和XAUI等,这部分电路结构示意图所示。

8B/10B解码。

8B/10B解码器在这里完成8B/10B解码的功能,将10bit数据转换为8bit源数据。

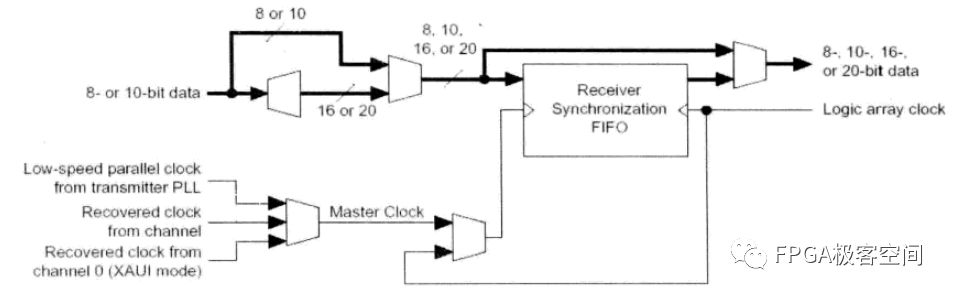

收端到逻辑资源的接口。

SERDES恢复出的数据进入FPGA有一个解复用和时钟域转换的问题,Stratix GX包含了专用电路可以完成8/10bit数据到8/10/20bit数据的Mux/Demux,另外SERDES收端到FPGA内部通用逻辑资源之间还有FIFO可以完成数据接口同步,其电路结构如图所示。

发送方向的结构相对简单多,只要按照收端数据流向反向追溯,就非常容易理解发端主要模块的功能与结构,发端主要包含以下功能模块。

(1)FPGA逻辑资料SERDES发端的接口电路。

从FPGA逻辑资源到发端内嵌8字节深的FIFO用以完成数据接口的同步,另外还有Mux/Demux电路,其结构与收端到FPGA逻辑资源接口电路相似。

(2)8B/10B编码。

将8bit源数据编码为10bit数据,减少连”0”或连”1”串。

(3)发端PLL。

发端PLL参数如图所示。

(4)并串转换电路(Serializer)。

其并串转换的顺序是低位(LSB)先出。

(5)输出缓冲。

其支持的I/O标准和可编程匹配阻抗特性与收端缓冲性能相似。值得一提的是,其Vod电压动态可编程范围为400Mv~1600mV,而且新器件的预加重范围提升为0%~140%(Vod为800mV条件下)。

值得强调的是,Altera Stratix GX的SERDES模块的可测试性非常好,提供丰富的环回模式,便于用户上板调试。Stratix GX的SERDES支持以下测试模式。

信道环回(Channel loopback):包括串行环回(Serial loopback)、反向链路串行环回(Reverse serial loopback )、并信环回(Parallerl loopback)和方向链路并行环回((Reverse parallel loopback)4种模式。

BIST(Built-In Self Test,内嵌式自测)产生与校验(BIST generator &verifier):包括BIST 8B并行环回、BIST并行环回和BIST串行环回3种模式。

PRBS产生与校验(BIST generator& verifier):包括PRBS并行环回和PRBS串行环回两种模

-

FPGA

+关注

关注

1602文章

21320浏览量

593155 -

解码器

+关注

关注

9文章

1073浏览量

40157

原文标题:Stratix IV GX内嵌的SERDES(二)

文章出处:【微信号:ALIFPGA,微信公众号:FPGA极客空间】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

解决FPGA一个解复用和时钟域转换问题

解决FPGA一个解复用和时钟域转换问题

评论