在集成电路制造工艺升级的过程中,High-K和FinFET的出现对摩尔定律的延续发生了重要的作用,并一再打破了过去专家对行业的预测。近年来,随着工艺的进一步演进,业界又开始产生了对晶体管能否继续缩进产生了疑惑。

在今日开幕的CSTIC2018上,FinFET的发明者胡正明教授发表了题为《Will Scaling End?What Then?》的演讲,探讨集成电路制造的发展方向。

胡教授表示,在1999年的时候,业界的普遍观点是晶体管微缩将会在35纳米的时候结束。

然而,就在同一年,UC Berkeley推出了45纳米的FinFET晶体管。得益于新的晶体管构造模式,器件的性能测试参数获得了不错的效果。

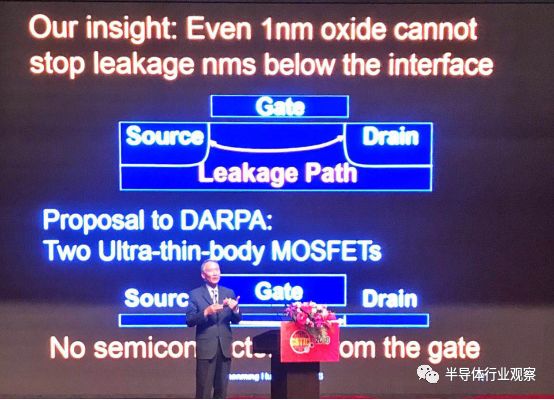

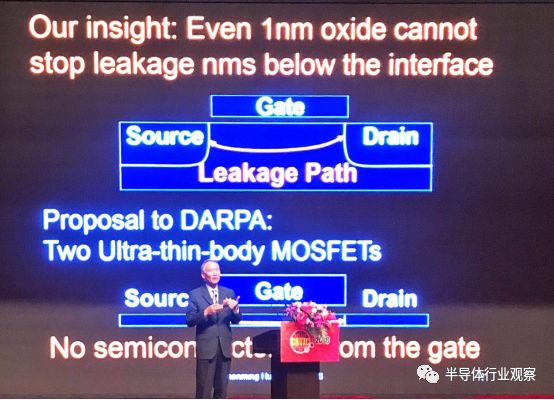

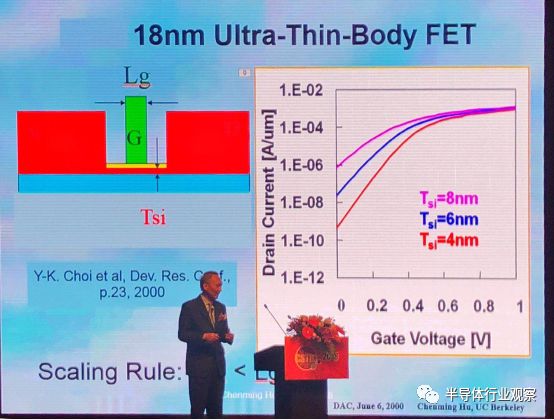

在当时,胡正明教授团队即发现,即使1nm的氧化层也无法消除界面以下数纳米处的漏电,所以他们向DARPA提议了两种Ultra-thin-body的MOSFET。

其中之一就是堪称改变整个半导体历史的FinFET:

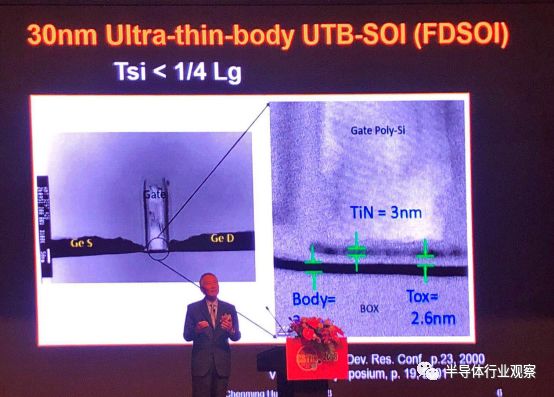

另一结构就是UTB-SOI (FDSOI):

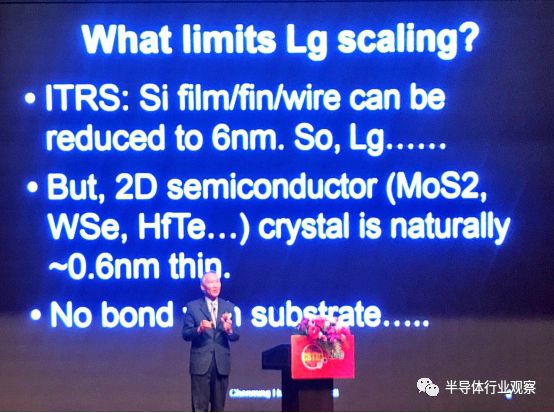

在谈到限制Lg微缩的原因,根据ITRS的的观点,硅的film/fin/wire能够减小到6nm。

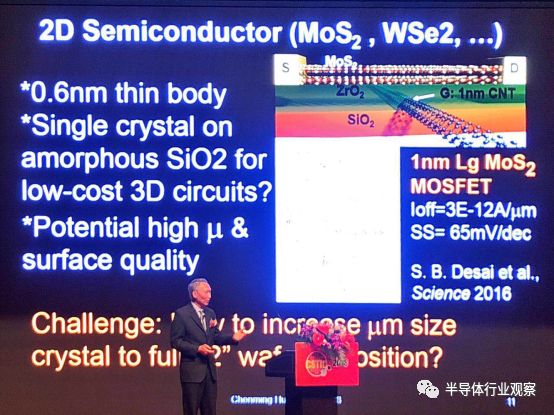

但是,MoS2、WSe和HfTE等材料的晶体天然厚度就是0.6nm,基于这些材料的2D晶体管拥有更短的Lg和更好的电学特性,但是制作工艺很困难,想要在12寸wafer上均匀生长其实有很大的挑战。

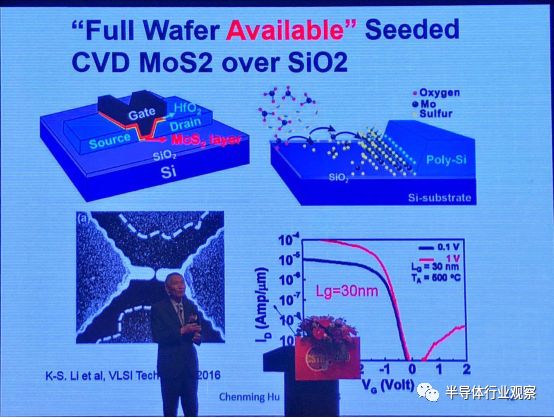

他进一步指出,Full wafer available Seeded CVD MOS2 over SiO2

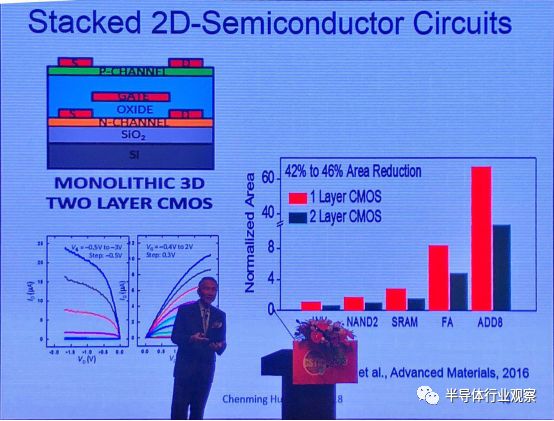

之后胡教授介绍了堆叠的2D半导体电路

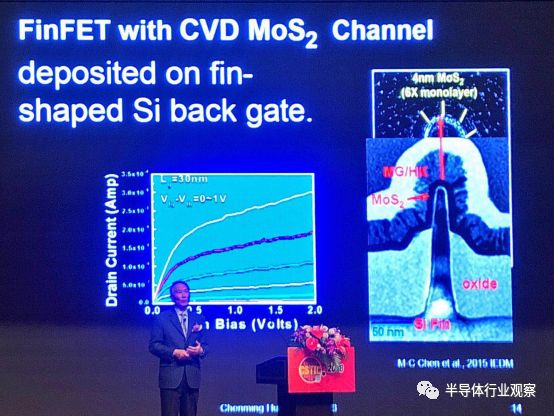

还谈到了CVD MoS2 沟道放置在鳍状Si back gate的FinFET

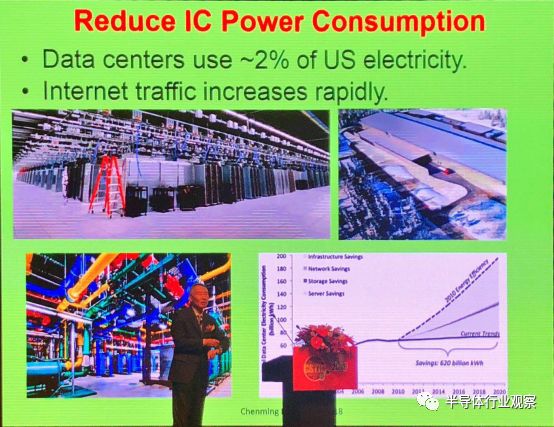

胡教授强调了降低IC功耗的重要性

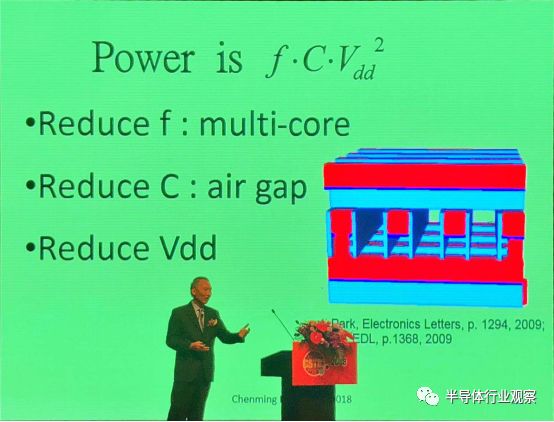

要达到降低功耗的目的,那就需要从以下三个方向考虑:

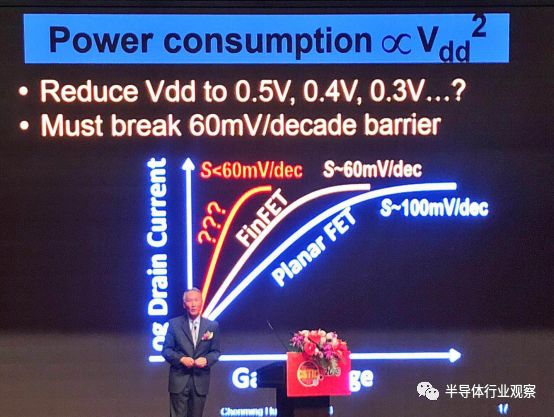

首先他分享了关于降低Vdd的观点

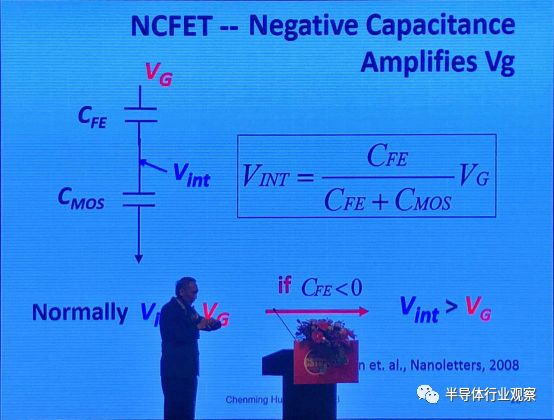

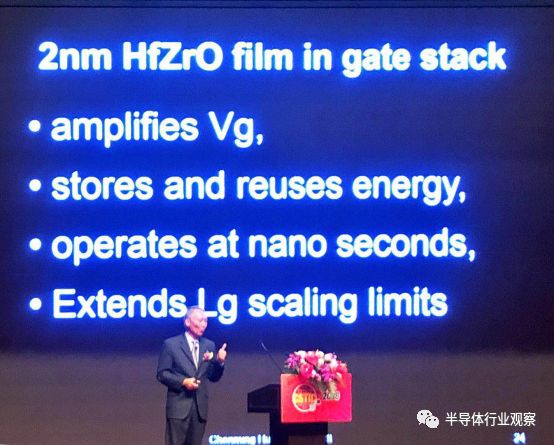

然后胡教授还谈到了负电容晶体管(NCFET)

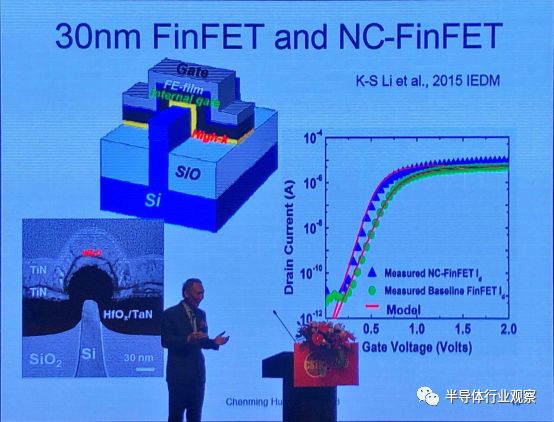

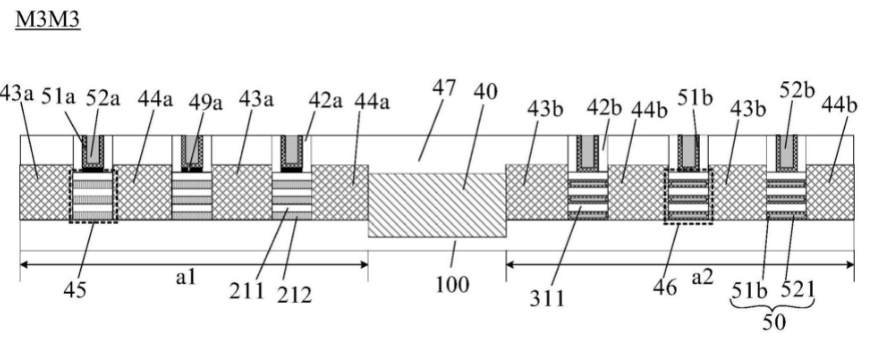

他将30纳米 FinFET和NCFET做了对比

并进一步强调了NCFET的特性

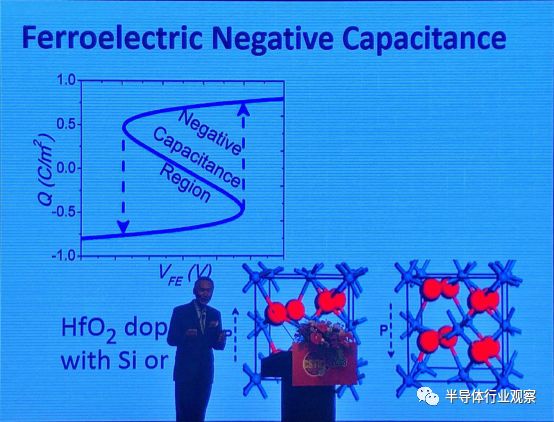

之后胡教授还介绍了Ferroelectric Negative Capacitance

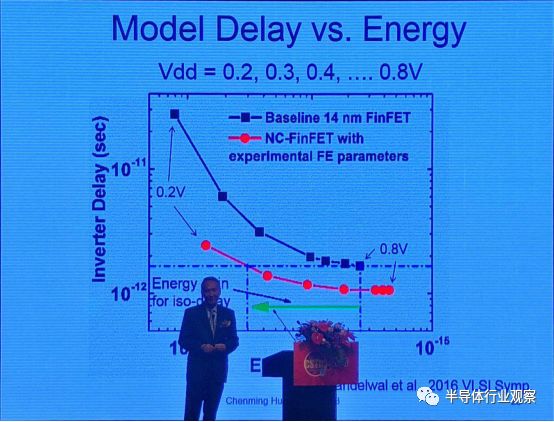

还做了一个不同电压下的表现对比

他还总结了以下几点

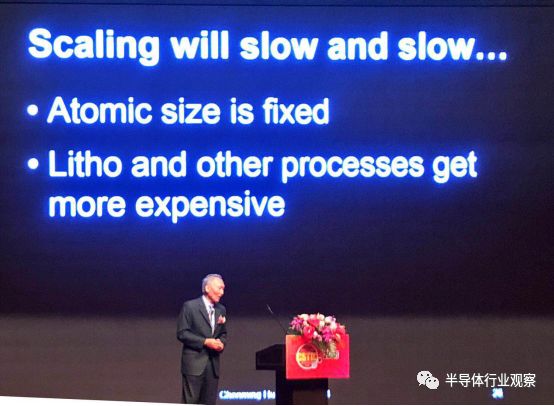

胡教授表示,晶体管微缩会变得越来越慢。

一方面因为原子的尺寸是固定的,会达到物理极限;另一方面光刻和其他制造技术变得越来越昂贵。但是通过器件创新,cost-power-speed能够继续改进。

整个半导体产业一定能长期增长。不是每个人都会获益,有输家和赢家,但是因为半导体体量很大,赢家会很成功。过去几年半导体产值超过1995年前所有总和,半导体成长不会慢于全球经济增长,因为人们需要更智能的设备。

最后,胡教授就他这个演讲,做了一个总结:

-

集成电路

+关注

关注

5320文章

10732浏览量

353355 -

半导体

+关注

关注

328文章

24506浏览量

202092 -

晶体管

+关注

关注

76文章

9054浏览量

135188

原文标题:胡正明:晶体管微缩会终结吗?

文章出处:【微信号:MooreNEWS,微信公众号:摩尔芯闻】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

探秘我国集成电路科技工作者早期创业足迹

在特殊类型晶体管的时候如何分析?

集成电路制造的起源和发展

集成电路制造工艺升级的过程中,晶体管微缩会终结吗?

集成电路制造工艺升级的过程中,晶体管微缩会终结吗?

评论