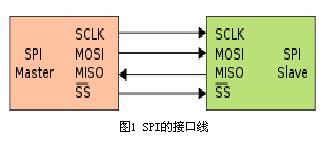

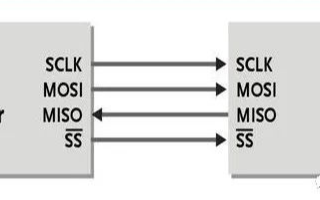

SPI(Serial Peripheral Interface,串行外设接口)是Motorola公司提出的一种同步串行数据传输标准,在很多器件中被广泛应用。1. 接口SPI接口经常被称为4线串行总线,以主/从方式工作,数据传输过程由主机初始化。如图1所示,其使用的4条信号线分别为:1) SCLK:串行时钟,用来同步数据传输,由主机输出;2) MOSI:主机输出从机输入数据线;3) MISO:主机输入从机输出数据线;4) SS:片选线,低电平有效,由主机输出。在SPI总线上,某一时刻可以出现多个从机,但只能存在一个主机,主机通过片选线来确定要通信的从机。这就要求从机的MISO口具有三态特性,使得该口线在器件未被选通时表现为高阻抗。

2. 数据传输

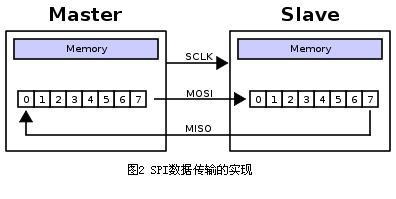

在一个SPI时钟周期内,会完成如下操作:1) 主机通过MOSI线发送1位数据,从机通过该线读取这1位数据;2) 从机通过MISO线发送1位数据,主机通过该线读取这1位数据。这是通过移位寄存器来实现的。如图2所示,主机和从机各有一个移位寄存器,且二者连接成环。随着时钟脉冲,数据按照从高位到低位的方式依次移出主机寄存器和从机寄存器,并且依次移入从机寄存器和主机寄存器。当寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。

3. 时钟极性和时钟相位

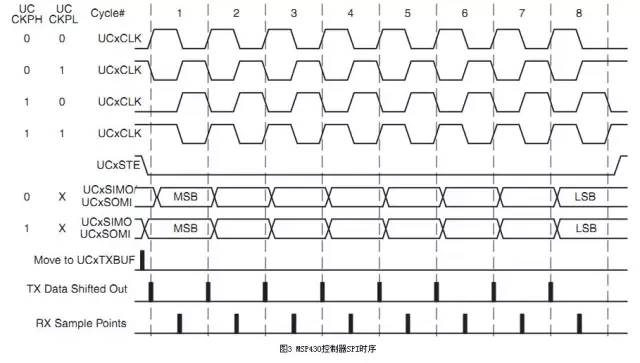

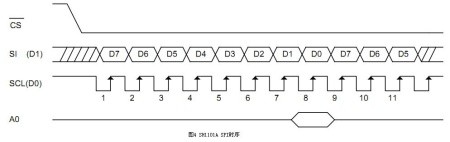

在SPI操作中,最重要的两项设置就是时钟极性(CPOL或UCCKPL)和时钟相位(CPHA或UCCKPH)。时钟极性设置时钟空闲时的电平,时钟相位设置读取数据和发送数据的时钟沿。主机和从机的发送数据是同时完成的,两者的接收数据也是同时完成的。所以为了保证主从机正确通信,应使得它们的SPI具有相同的时钟极性和时钟相位。举例来说,分别选取MSP430控制器和OLED驱动SH1101A为主从机,图3和图4为它们的SPI时序。由图4可知,SH1101A的SPI时钟空闲时为高电平,并且在后时钟沿接收数据,则MSP430控制器SPI的设置应与此保持一致。从图3中可以看出,要使得时钟在空闲时为高电平,应将UCCKPL置1;要使得在后时钟沿接收数据,应将UCCKPH清零。

4. 优缺点SPI接口具有如下优点:1) 支持全双工操作;2) 操作简单;3) 数据传输速率较高。同时,它也具有如下缺点:1) 需要占用主机较多的口线(每个从机都需要一根片选线);2) 只支持单个主机。

-

SPI

+关注

关注

17文章

1615浏览量

89597 -

CPOL

+关注

关注

0文章

9浏览量

9990 -

CPHA

+关注

关注

0文章

8浏览量

9343 -

miso

+关注

关注

0文章

6浏览量

5377

原文标题:弄懂SPI接口

文章出处:【微信号:eet-china,微信公众号:电子工程专辑】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SPI通信的四种方式 FPGA的SPI从机实现方案

SPI中主机和从机模式的区别是什么?

HbirdV2-SoC中如何配置QSPI1和QSPI2的时钟极性CPOL和时钟相位CPHA?

正投、背投、吊装以及桌面安装的优缺点解析

ofdm技术的优缺点解析,ofdm技术原理介绍

SPI接口的概念,数据传输, 时钟极性、时钟相位以及优缺点解析

SPI接口的概念,数据传输, 时钟极性、时钟相位以及优缺点解析

评论