1 引言

射频功率放大器是无线发射机中的核心模块之一,也是无线收发机*耗最大的模块,为了 降低功耗,延长电池寿命,要求它具有高效和大功率输出。随着硅CMOS 工艺的不断改进,采用 标准CMOS 工艺实现高性能的功率放大器是当今射频电路向尺寸更小、价格更低以及全片集成方 向发展的必然趋势,科研工作者们在相关理论研究以及电路性能的改进方面做了大量工作[1~5]。 本文基于0.18μm CMOS 工艺,主要从高效率和集成化的角度优化考虑,设计实现了一个工作频 率在2.4GHz 处的两级全集成E 类开关模式功率放大器,获得较好的仿真效果。

2 工作原理

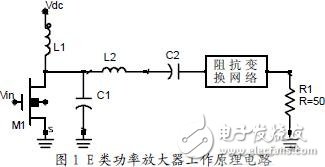

图1 给出了标准E 类功率放大器工作原理电路。其中,扼流电感 L1 阻止交流信号通过,并 给晶体管提供直流电流。 L2 、 C2 组成一个串联谐振网络,以使流过该网络的电流为理想的正弦 信号,所有谐波成分都被滤除。并联接地电容 C1 由两部分组成,一部分是晶体管的寄生电容,另 一部分是实际引入的电容。驱动电压过驱动使得晶体管M1 可近似作为开关来使用,当它导通时,晶体管上压降为零;而当它截止时,流过晶体管的电流为零。E 类功率放大器正是通过对开关上 的电压整形,使得在开关导通瞬间,开关上的电压和电压变化斜率都近似为零,从而达到减小开 关损耗,提高效率的目的。通常电路元件参数可由以下公式大致确定[6]:

其中,Q为电路品质因数,ω 为工作频率, dc V 、dc I 为漏端电压、电流, RL 为获得所需功率out P 而将终端50Ω 电阻进行阻抗变换得到的匹配电阻。

3 电路设计与分析

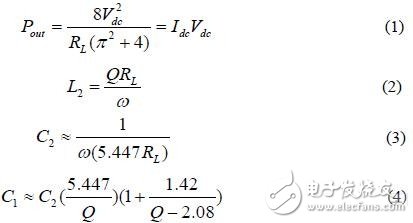

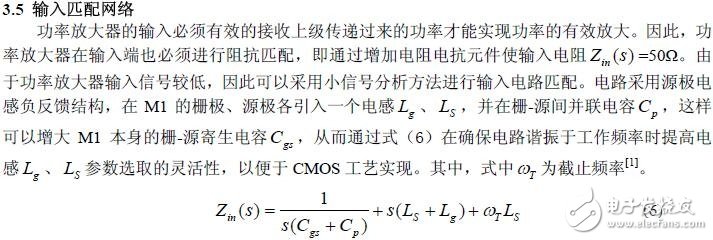

通常情况,单级功率放大器增益仅为 10dB 左右,需要增加高增益的驱动级来提高整体功放 的增益。因此,功率放大器设计一般就分为功率输出级、输出匹配、增益驱动级、级间匹配、输 入匹配等部分。图2 为本文基于这种结构思想、采用0.18μm CMOS 工艺设计实现的两级全集成 E 类开关模式功率放大器的具体电路,其中驱动级为准F 类,输出级为E 类。

3.1 功率输出级

功率输出级采用工作原理中介绍的标准 E 类功率放大器结构,这种直接由M3 管构成的共源 结构能够充分利用电源电压的幅度,提高输出电压摆幅。由于E 类功率放大器的漏端最高电压可 能升高到3.6Vd 2 [1],为保证MOS 管不被击穿,电路选用2V 电压供电。功率输出级是射频功率 放大器中最关键的一级,它的性能特性包括输出功率、效率等将直接影响整个放大器的性能。晶 体管必须选取在最小电压降时至少可以提供dc I 大小的直流电流,且工作在线性区。同时,还得 对该晶体管的输出功率和效率进行扫描*估,以确保选取的晶体管可以达到预设计的性能指标要 求。我们在设计过程中的经验表明,通过负载牵引(Load-Pull)技术能有效的预测输出晶体管的 输出功率和效率,并在整体电路设计好后这两项指标还会有所提高。

3.2 输出匹配网络

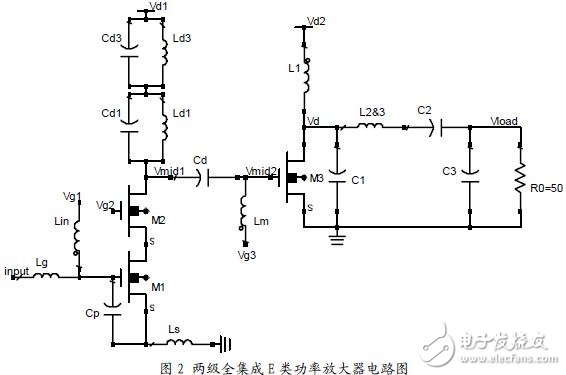

通常电路终端接的是 50Ω 的电阻,为获得理想的输出功率由公式(1)计算得到的实际负载 RL 通常比较小,需要阻抗变换。输出匹配网络的目的就是提供器件的输出端到负载阻抗之间的最大 功率传输所需要的阻抗。为了最小化无源器件和有效滤除高次谐波分量,电路选用如图3 线框中 所示的L 型低通阻抗匹配结构。这样, L 型低通阻抗变换电路电感 L3 便可与功率输出级的串联 谐振电感 L2 合二为一成电感L2&3 ,从而有效减少片上电感所占据的芯片面积。由于功率放大器 工作频率较高,使得晶体管阻抗特性的各参数受到工作频率、输入电平、输出端负载阻抗、电源 偏置以及温度等的影响。功率放大器晶体管的阻抗一般来讲是一个复数,并且不仅会随着频率的 变化而变化,还会随输出信号的电压和电流而变化,这样输出级与天线之间的阻抗变换网络的实 现就比较困难。在设计中,输出阻抗变换网络我们采用Load-Pull 技术来获取最佳负载阻抗,然 后根据该阻值利用Smith 图解设计工具便可获得低通阻抗匹配元件的具体参数。

3.3 增益驱动级

增益驱动级采用由 M1、M2 组成的共源共栅(Cascode)结构加两个谐振网络一起构成的准 F 类放大器模式。共源共栅结构可以有效降低Miller 电容的影响,提高输入-输出之间的隔离度。 两个谐振网络中: Cd1 和L d1 构成的谐振器调谐在ω 处, Cd 3 和Ld 3 构成的谐振器调谐在3ω 处。 通过适当地调谐这四个参数,确保谐振网络对二次谐波短路,输出电路为基波和三次谐波叠加, 从而获得E 类放大器所需的近似方波驱动信号。在电路性能测试中我们发现,由于准F 类放大器 结构的开关电压峰峰值可达到2Vd1,因此增益驱动级的电源电压可以大大降低,从而可以有效减 少整个电路的直流功耗,提高电路的整体效率。

3.4 级间匹配网络

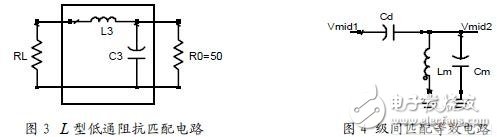

级间匹配网络需要匹配前一级器件的输出阻抗和后一级器件的输入阻抗,应选择高增益的级 间拓扑,并实现平坦的增益响应。级间匹配还应具备级间隔直流功能,通常加入隔直电容Cd 。 电路并联电感 Lm 可使功率输出级输入端看到的MOS 管寄生电容Cm 减小,从而提高电压传输效 率[5]。级间匹配等效电路如图4 所示,从增益驱动级输出端看到的等效阻抗为:

增益驱动级的方波信号是由基波和三次谐波叠加而成,因此通过公式(5)要确保增益驱动 级输出端看到的三次谐波和基波等效阻抗必须具有相同的容性或感性,否则会由于相位相反无法 形成方波。此外,测试中我们还发现Cd 值对传输效率影响比较敏感,为提高电压传输效率, Cd 一般需要取较大值。

4 仿真分析

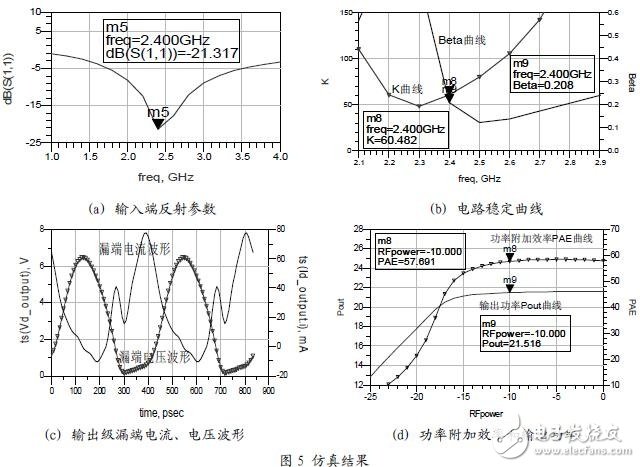

本设计基于0.18μm CMOS 工艺,充分考虑了片上电感品质因数不高、电感值较小和占有面 积较大的局限条件下,实现了电路的全片集成。在2V 电源电压条件下利用ADS2005A 进行仿真, 仿真结果如图5 所示。

当电流Id 趋于零时电压Vd达到峰值,而当电流Id 达到峰值时电压Vd趋于零,这与理想E 类开关 模式功率放大器的输出目标基本吻合,从而实现电路较大功率和较高效率的输出。图(d)表明,电 路在输入功率为-10dBm 时的输出功率约为21.5dBm,功率附加效率达到了57.69%的较好结果, 相应功率增益为31dB。

在性能仿真过程中我们发现,电路各级的阻抗匹配对电路的影响都非常大,阻抗匹配是电路 设计成败的关键。采用Load-Pull 技术是获取最佳输出匹配负载和预测晶体管输出功率和效率的 有效且便捷的手段。此外,输出晶体管尺寸对整体电路的输出功率和效率有着密切的联系,存在 最佳尺寸,使得电路主要性能达到最优化,但相应对电路的工作条件如驱动级电源电压等的要求 更高,因此需要折中考虑。

5 结论

本文的创新点在于在输入匹配晶体管栅-源间并接电容 Cp 极大的提高了在片电感选择的灵 活性;同时采用准F 类放大器作为驱动级,获得了E 类功率放大器所需要的方波驱动信号。本文 设计的E 类开关模式功率放大器达到了全集成、高效、大功率输出的目的,与国内外设计相比达 到先进水平[3-5]。随着CMOS 工艺和电感工艺的不断改进,由该技术实现的功率放大器在未来无 线通信领域必将有着广泛的应用前景。

-

放大器

+关注

关注

142文章

12416浏览量

210006 -

电路设计

+关注

关注

6565文章

2317浏览量

195366 -

射频功率

+关注

关注

0文章

32浏览量

12882

发布评论请先 登录

相关推荐

两款固定增益放大器消除设计方案难题

可编程增益放大器在模数接口的应用

浅析CMOS高线性变增益放大器

基于双路差动放大器实现精密ADC驱动器设计

数字可编程增益放大器设计方案

E类射频功率放大器设计

基于LMP8358的高精度可编增益仪表放大器设计方案

采用包含增益驱动级,实现了全片集成的放大器设计方案

采用包含增益驱动级,实现了全片集成的放大器设计方案

评论