电子发烧友网报道(文/周凯扬)2022年1月,PCI-SIG发布了PCIe 6.0规范,正式拉开了接口带宽大幅升级的序幕。然而,在规范公布的两年时间里,也已经更新了6.0.1和6.1版本,PCIe 6.0似乎在设计层面上已经完善了。但我们这期间并没有看到PCIe 6.0产品的实际落地,甚至PCIe 5.0产品只是在消费级产品小批量落地而已。而在今年三月,根据PCI-SGI的预测,PCIe 6.0的硬件终于快要面世。

AI/ML、HPC和云端图形负载渴求的翻倍带宽

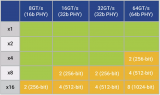

作为从服务器与PC起家的接口,PCIe近几年已经开始辐射到以数据为核心的应用中去,比如IoT、汽车和医疗电子等。从PCIe 3.0开始,每一代接口标准规范都会为速率带来翻倍的提升,PCIe 6.0更是将速率提升至64GT/s,x16单向带宽拔高至256GB/s。

这样的速率或许在IoT应用中显得有些多余,但在时下大热的AI/ML应用中,可以说是大幅提高计算效率的杀手锏。要知道目前爆火的生成式AI应用ChatGPT等,可谓受尽了大量同时访问与需求的困扰,即便H100的带宽再高,在PCIe 5.0下依然计算效率受限,得靠NVLink才能突破限制。

目前的数据中心,尤其是其中的AI服务器,已经成了带宽无底洞。何况对于处理AI/ML训练模型来说,以快制胜可以说是一条市场铁则。更快的带宽意味着生成式AI的并发响应更快,给到更短的文本、图形生成时间,从而进一步提升用户体验。而对于大部分托管/租用服务器的应用开发者来说,这也意味着运营成本大幅降低。

HPC也不例外,在长时间运转的HPC服务器中,带宽就意味着计算效率,尤其是量子力学、分子动力学所用到的软件,所需内存带宽更高。如果没有足够的带宽,就只能分节点来减小不同进程之间的带宽竞争。最后一大痛点是云游戏带来的,对于这种需要多并发高图形负载的运用而言,带宽就决定了云游戏的并发数以及图形质量。

AI/ML会加速PCIe 6.0的落地吗

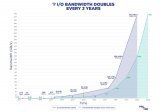

从PCIe的发展历史来看,平均3到4年就会正式推出新的规范,只有从3.0到4.0经历了7年的漫长的时间,这也是因为彼时的PCIe 3.0已经算是超前的标准,直到2015年后,全球数据流量进入爆发期。此后从4.0演进至5.0花了2年时间,从5.0演进至6.0花了三年时间。据推测,PCIe 7.0规范将在2025年正式推出。

然而我们也发现,基于新标准的PCIe产品在落地速度上并没有那么快。往往最先落地的是AI加速器、SSD等设备,毕竟本地处理速度再快也要网络速度跟上才行。就拿还未实现的800G以太网为例,其所需要的单向带宽也就是100GB/s,正好在PCIe 6.0的带宽覆盖范围内。

所以即便有着AI/ML的推进,今年应该只会有少数PCIe 6.0产品能够落地,且落地场景还是集中在数据中心领域,且先一步用于AI服务器上,这点从PCIe 6.0控制器IP、服务器CPU IP厂商的动向上也可以看出。

写在最后

PCIe 6.0作为目前最先进的接口标准之一,注定会为下一轮计算、存储技术的创新带来设计便利。但我们也应该实时关注市场需求,过去的PCIe能够维持主流接口的地位,正是靠的联合硬件厂商稳步推进市场需求,这个策略在AI时代依旧通用。

-

接口

+关注

关注

33文章

7640浏览量

148510 -

AI

+关注

关注

87文章

26459浏览量

264080 -

PCIe

+关注

关注

13文章

1083浏览量

80856

发布评论请先 登录

相关推荐

下一代PCIe5.0 /6.0技术热潮趋势与测试挑战

研扬最新COM-HPC模块让您获得源源不断的强劲性能

11月24日|泰克云上大讲堂—PCIe测试面面观

HPC与AI:完美融合

新思科技成功实现与英特尔PCIe 6.0测试芯片的互操作性

新思科技PCIe 6.0 IP与英特尔PCIe 6.0测试芯片实现互操作

PCIe 6.0的优化设计方案探讨分析

PCIe的基础知识整理

PCI Express突飞猛进:与PCIe 6.0实现高带宽互连

PCIe 6.0入门之什么是 PCIe 6.0

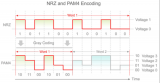

Samtec技术前沿 | 多重原因促使PCIe® 6.0采用了PAM4

多重原因促使PCIe®6.0采用了PAM4

PCIe 6.0元年,AI与HPC迎来新速度

PCIe 6.0元年,AI与HPC迎来新速度

评论