在PCBA生产中,经常容易在器件的尾端产生连锡现象,在生产中为了避免这种缺陷,设计时需要在器件的尾部加一对无电气属性的焊盘,即为偷锡焊盘。其作用是在焊接过程中,引导锡膏或焊锡流向正确的位置,从而提高焊接的一次性成功率。

在PCB设计中,我们经常需要处理各种封装的元件,其中SOP、QFP、DIP、SIP、ZIP等系列封装的元件就需要进行偷锡焊盘的处理。本文便主要为大家介绍偷锡焊盘的三种常见处理方式。

01

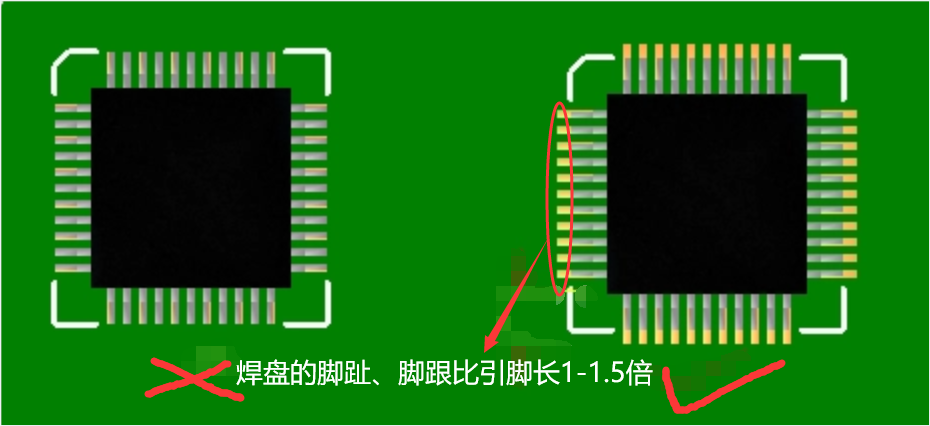

增长引脚焊盘

● 这种方式适用于QFP系列封装的元件。

在回流焊时,增长的引脚焊盘可以加强元件引脚的引力,有利于元件的居中对齐与定位;同时在波峰和手工焊接时,增长的引脚焊盘也可以起到偷锡的作用,具体要求如下:

01

焊盘宽度与元器件引脚相同。

02

焊盘长度为元器件引脚的1-1.5倍。

02

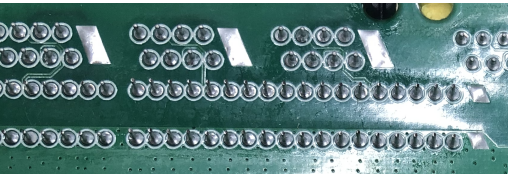

增加偷锡焊盘

●这种方式适合用于DIP、SIP、ZIP等系列封装的元件。

在原有的封装基础上,增加一个边脚焊盘,来达到元件引脚不连焊的目的,具体要求如下:

01

焊盘封装引脚间距小于1.27mm时,必须增加偷锡焊盘。

02

偷锡焊盘尺寸要比原焊盘尺寸大。

03

背面的偷锡焊盘,应加在PCBA走向的下游方位。

04

偷锡焊盘应与其相邻的末尾焊盘同一网络或悬空,不应与末尾焊盘有冲突,以免在偷锡焊盘与末尾焊盘连焊时,造成不同网络的短路。

05

若偷锡焊盘位于元件外框丝印的内部或覆盖外框丝印,应对外框丝印进行调整,以使偷锡焊盘位于元件外框丝印之外,避免造成焊接错位。

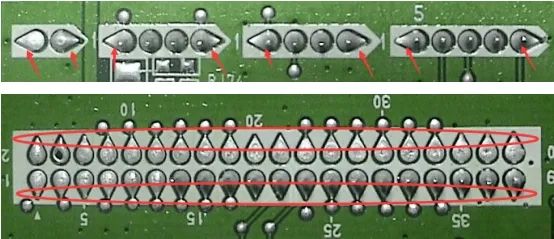

03

增加拖尾焊盘

●这种方式适用于DIP、SIP、ZIP等系列封装的元件。

在原有的封装基础上,如果在末尾焊盘位置,没有足够空间额外增加偷锡焊盘,则可以采用将末尾焊盘改为圆锥(泪滴)形,具体要求如下:

01

封装引脚间距小于2.0mm时,必须增加拖尾焊盘。

02

封装平行于PCBA走向时,只在末尾引脚增加拖尾焊盘。

03

封装垂直于PCBA走向时,每间隔一个引脚增加一个拖尾焊盘。

在PCB设计中,偷锡焊盘的处理是确保焊接质量和一次性成功率的关键;通过增长引脚焊盘、增加偷锡焊盘和增加拖尾焊盘等方式,可以避免元件引脚连焊,提高焊接效果。

在处理过程中,需要根据具体元件的封装和焊接要求,选择合适的处理方式,且需要注意细节,以确保焊接效果最佳。

华秋DFM软件是国内首款免费PCB可制造性和装配分析软件,拥有300万+元件库,可轻松高效完成装配分析。其PCB裸板的分析功能,开发了19大项,52细项检查规则,PCBA组装的分析功能,开发了10大项,234细项检查规则。

基本可涵盖所有可能发生的制造性问题,能帮助设计工程师在生产前检查出可制造性问题,且能够满足工程师需要的多种场景,将产品研制的迭代次数降到最低,减少成本。

https://dfm.elecfans.com/dl/software/hqdfm.zip?from=DFMGZH

华秋是一家致力于以信息化技术改善传统电子产业链服务模式的产业数智化服务平台,目前已全面打通产业上、中、下游,形成了电子产业链闭环生态,致力于为行业带来“高品质,短交期,高性价比”的一站式服务平台,可向广大客户提供媒体社区平台服务、元器件采购服务、PCB制造服务及可靠性制造分析服务、SMT贴片/PCBA加工服务,如有相关业务需求,请扫码填写以下表单,我们将为您对接专属服务。

点击上方图片关注我们

原文标题:【华秋干货铺】拒绝连锡!3种偷锡焊盘轻松拿捏

文章出处:【微信公众号:华秋电子】欢迎添加关注!文章转载请注明出处。

-

华秋电子

+关注

关注

18文章

453浏览量

13148

原文标题:【华秋干货铺】拒绝连锡!3种偷锡焊盘轻松拿捏

文章出处:【微信号:huaqiu-cn,微信公众号:华秋电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【华秋干货铺】拒绝连锡!3种偷锡焊盘轻松拿捏

【华秋干货铺】拒绝连锡!3种偷锡焊盘轻松拿捏

评论