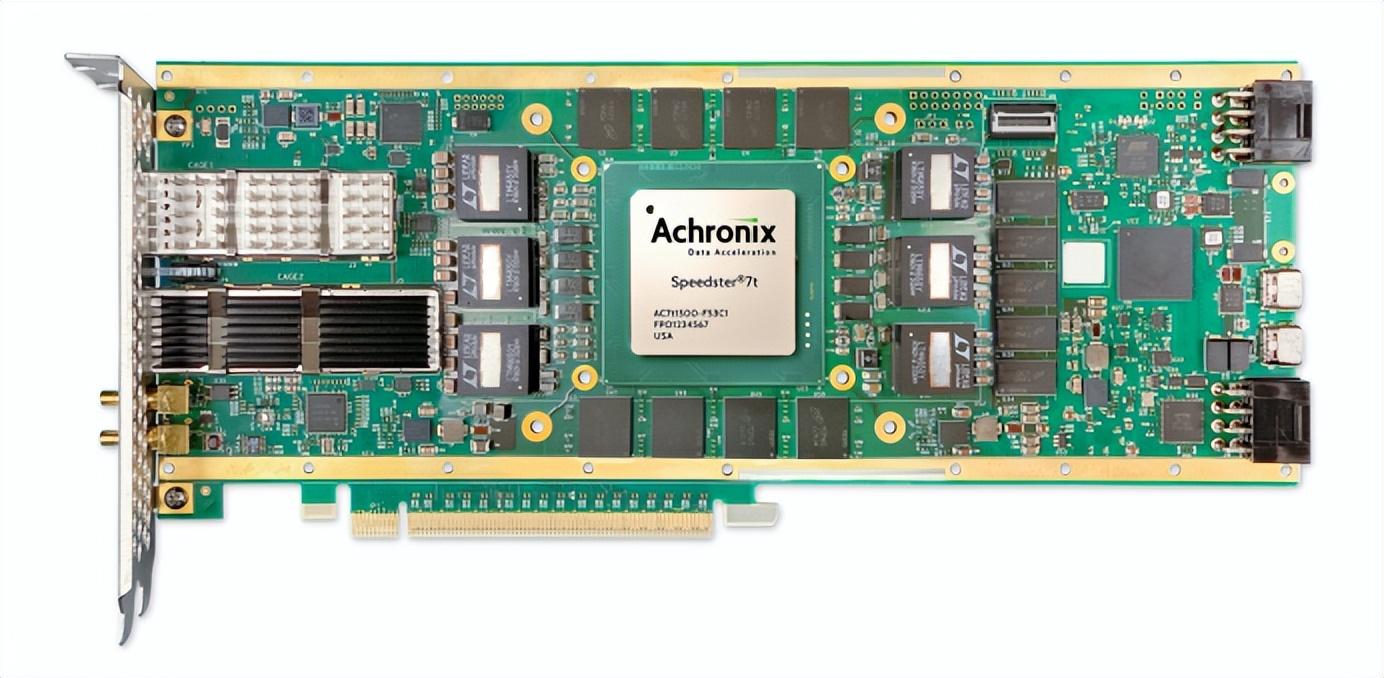

11月13-18日,Achronix将在全球极具影响力的高性能计算专业会议“International Conference on High-performance Computing, Networking, Storage and Analysis(SC22)”上,展出其全系列基于FPGA技术的硬件数据处理加速器产品和解决方案,包括Achronix专为超大数据带宽打造的Speedster7t FPGA芯片、面向异构计算等新兴SoC/ASIC的Speedcore嵌入式FPGA IP (eFPGA IP)、基于Speedster7t的VectorPath加速卡、以及可以支持上述全部产品的ACE开发工具。

由IEEE计算机学会等机构主办的该项活动汇集了高性能计算领域最新科技展示和学术成就发布,尽管该活动内容和覆盖领域不断增加和扩大,业界和学界还一直称其为SuperComputing,因而今年该项活动的简称为SC22,它将在美国德克萨斯州达拉斯市Kay Bailey Hutchison Convention Center举办。

SC22的主题是“大规模技术计算和数据科学的未来(the future of large-scale technical computing and data-driven science)”。今年各项活动的焦点将是上述相关领域内的最佳实践,包括架构和网络创新、云和分布式计算、数据分析、虚拟化、存储、机器学习和高性能计算(HPC)。

Achronix在SC22上的展位号为4123欢迎莅临Achronix的展位,并欢迎提前与我们预约以安排会议,我们将展出专门为人工智能、机器学习、网络技术、数据中心、智能汽车和其他高性能计算打造的FPGA技术。包括:

·VectorPath加速卡:它是用于快速原型开发和方案量产的PCIe加速卡,可提供400G和200G的以太网接口,以及高达4 Tbps的GDDR6存储带宽。

·Speedster7t系列FPGA芯片:它们是高性能的独立FPGA芯片,带有二维片上网络(2D network on chip),可提供ASIC级别的性能,以及FPGA的完全可编程性。

·Speedcore eFPGA IP:该系列eFPGA IP内核的出货量已超过1500万个,为各种ASIC和SoC提供了高性能和可编程逻辑的灵活性。

Achronix支持您的创新

Achronix乐于用最新FPGA科技来支持您的创新,共同去应对您的设计挑战。欢迎在SC22上参观我们的展台和预约会议,也欢迎大家在国内与我们的支持团队交流。凭借业内独有的FPGA产品组合,Achronix将能够为您定制一个高性能数据处理解决方案。

-

FPGA

+关注

关注

1603文章

21328浏览量

593275 -

加速器

+关注

关注

2文章

746浏览量

36600 -

Achronix

+关注

关注

1文章

69浏览量

22468

原文标题:Achronix将在SC22上展示全系列基于FPGA的硬件数据处理加速器

文章出处:【微信号:Achronix,微信公众号:Achronix】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Achronix FPGA增加对Bluespec提供的基于Linux的RISC-V软处理器的支持,以实现可扩展数据处理

为何高端FPGA都非常重视软件

【国产FPGA+OMAPL138开发板体验】(原创)7.硬件加速Sora文生视频源代码

FPGA图书分享系列-2024.01.31

《数据处理器:DPU编程入门》+初步熟悉这本书的结构和主要内容

21489的IIR加速器滤波参数设置如何对应加速器的滤波参数?

ADRF5700: 46 dB, 2 dB LSB, 5-Bit, 硅数字加速器, 100 MHz 至 22 GHz 初步数据表 ADI

《 AI加速器架构设计与实现》+第2章的阅读概括

Intel媒体加速器参考软件用户指南

英特尔媒体加速器参考软件发行说明

英特尔媒体加速器参考软件Linux版用户指南

Achronix“内外兼修”赋能AI/ML数据加速

Achronix将在SC22上展示全系列基于FPGA的硬件数据处理加速器

Achronix将在SC22上展示全系列基于FPGA的硬件数据处理加速器

评论